# 第5回日独情報技術フォーラム 会 議 録

期 間: 昭和63年11月24日~26日

会 場: 国立京都国際会館

### 平成元年3月

社団法人 日本電子機械工業会 社団法人 日本電子工業振興協会 日 本 貿 易 振 興 会 財団法人 日本情報処理開発協会

この資料は、日本自転車振興会から競輪収益の一部である機械工業振 興資金の補助を受けて昭和63年度に実施した「日・独フォーラム」の 一環としてとりまとめたものであります。

## 目 次

| 1. 日独情 | 青報技術フォーラム趣旨                   | 1   |

|--------|-------------------------------|-----|

| 2. 開会抽 | 矣拶                            |     |

| 2. 1   | 本田幸雄 通商産業省機械情報産業局電子機器課長       | 3   |

| 2. 2   | ギュンター・マークス研究技術省情報処理担当課長       | 4   |

| 2. 3   | 柳井久義 1日本側議長 芝浦工業大学学長          | 6   |

| 2. 4   | ワンター・L・エングル ドイツ側議長 アーヘン工科大学教授 | 7   |

| 3.各分科  | 4会サマリー                        |     |

| 3. 1   | ニューメディア分科会                    | 9   |

| 3. 2   | コンピュータ分科会                     | 14  |

| 3. 3   | 半導体分科会                        | 19  |

| 4. 閉会接 | <b>挨拶</b>                     |     |

| 4. 1   | 柳井久義 日本側議長 芝浦工業大学学長           | 25  |

| 4. 2   | ワンター・L・エングル ドイツ側議長 アーヘン工科大学教授 | 27  |

| 〔付録〕   |                               |     |

| 付録 1.  | 基調講演アブストラクト                   | 29  |

| 付録2.   | ニューメディア分科会アブストラクト             | 39  |

| 付録 3.  | コンピュータ分科会アブストラクト              | 107 |

| 付録 4.  | 半導体分科会アブストラクト                 | 185 |

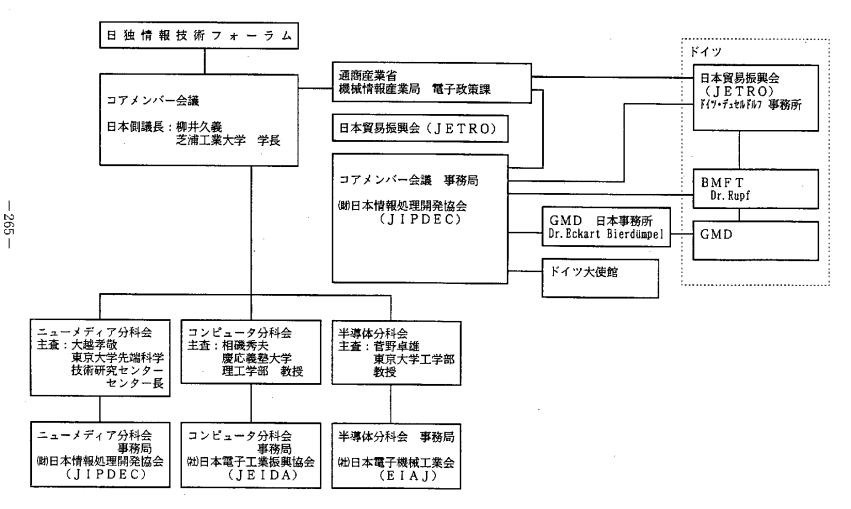

| 付録 5.  | 日独情報技術フォーラム体制                 | 265 |

| 付録 6.  | 第5回日独情報技術フォーラム・プログラム ······ 2 | 269 |

| 付録7.   | 企業訪問                          | 281 |

| 付録 8.  | 参加者名簿                         | 287 |

| 付録 9.  | 日独情報技術フォーラム開催経緯               |     |

|  |   |  | • |   |

|--|---|--|---|---|

|  | · |  |   |   |

|  |   |  |   |   |

|  |   |  |   |   |

|  | • |  |   | ^ |

|  |   |  |   |   |

|  |   |  |   |   |

|  |   |  |   |   |

|  |   |  |   |   |

|  |   |  |   |   |

|  |   |  |   |   |

1. 日独情報技術フォーラム趣旨

|   | <br><i>:</i> |  |

|---|--------------|--|

|   |              |  |

|   |              |  |

|   |              |  |

|   |              |  |

|   |              |  |

| , |              |  |

|   |              |  |

#### 1. 日独情報技術フォーラム趣旨

日独情報技術フォーラムは、高い技術レベルと経済力を有するドイツ連邦共和国とわが国が、情報技術分野における両国の相互理解と交流を一層深め、活発な産業、技術協力の展開を通じて世界の情報化に寄与していくことを目的に1983年8月ドイツ連邦共和国研究技術省のハインツ・リーゼンフ・バー(Dr. Heinz Riesenhuber) 大臣と当時の字野宗佑通商産業大臣との間で、その設置が合意されたものである。当該フォーラムは、両国の情報技術に関わる産業分野、学術分野、及び行政分野の指導的立場にある人々が一堂に会し、両国の研究開発のあり方、協力のあり方等について幅広い意見交換を行うと同時に、人的交流を深めることをねらいとしている。

当フォーラムは、毎年一回両国で交互に開かれることになっており、84年4月には第1回が東京で、85年4月には第2回がベルリンで、86年10月には第3回が東京で、87年10月には第4回がシュツットガルトで、それぞれ開催されている。

| ·. |   | , |          |

|----|---|---|----------|

|    |   |   |          |

|    |   |   |          |

|    |   |   |          |

|    |   |   |          |

| ,  |   |   |          |

| ,  | 1 |   |          |

|    |   |   | ·        |

|    |   |   |          |

|    |   |   | <u>.</u> |

|    |   |   |          |

|    |   |   |          |

|    |   |   |          |

|    |   |   |          |

|    |   |   |          |

|    |   | , |          |

|    |   | · |          |

|    |   |   |          |

|    |   |   |          |

## 2. 開 会 挨 拶

#### 2.1 本田幸雄 通商産業省機械情報産業局電子機器課長

皆様,おはようございます。ご紹介頂きました通商産業省機械情報産業局電子機 器課長の本田でございます。本日ここに第5回日独情報技術フォーラムが開催され ることに当たりまして,通商産業省を代表致しまして一言ご挨拶を申し上げます。

わが国の情報化は、本格化して以来約4半世紀を経ておりますが、近年の技術革 新に伴いネットワーク化を進めながら、産業、社会、家庭生活の各分野において、 広くかつ深く浸透しつつあります。また、情報化は地域社会の中にも点から線、線 から面へと急速にその輪を広げ、経済活動において、非常に重要な役割を果たしつ つあります。

しかしながら、高度情報化社会の実現に向けていまだ種々の問題が山積みされており、これらの課題への的確な対応が急務とされております。こうした認識のもとで、通商産業省といたしましては、情報化社会を底辺から支える情報処理技術者等の人材育成や、情報化教育の充実、ソフトウェアの量的・質的不足への対応、データベースの整備、多種多様な情報関連機器システムの相互運用性の確保、情報関連技術開発の一層の推進等を通じて、情報化基盤の整備及び情報化の推進の為、人材、ソフトウェア、ハードウェア、データベースの各方面から総合的な情報関連施策を展開しておるところでございます。

しかしながら、近年の情報化は国際的通信回線を用したトランザクション処理等に見られますように、国境を越えた情報の流通を促しております。また、ISOの場を中心にしたOSIプロトコルの審議、策定等にみられますように、今や国際的な協調ぬきには情報化を語ることはできません。その意味で、当省といたしましても、本フォーラムを積極的に推進しておるところでございます。

日独関係を振り返ってみますと、わが国はドイツ連邦共和国から医学、土木、機械などの分野において、多くの科学技術を導入いたしました。わが国の東半分の地域で使われている電気が50ヘルツなのは、最初にドイツから導入した発電機が50ヘルツだったためであります。また、戦後ではロータリーエンジンの技術がドイツ

連邦共和国から導入され、わが国で開花致しました。

近年では貿易、投資交流の面で、ドイツ連邦共和国とわが国とは、緊密な関係を維持しております。自動車、医療機器、コンピュータ等の工業製品を中心とする両国間の貿易は、ここ数年一貫して増加しています。ドイツ連邦共和国の11の州政府のうちの大半が対ドイツ連邦共和国投資の誘致の為の駐日事務所をわが国に設置されているのは、意外と知られていない事実でございます。

研究交流の面でも、1974年に締結されました科学技術協力協定のもとで広範な技術分野の研究協力が着実に実施されております。その一環で、1985年からドイツ連邦共和国の物理工学研究所と当方の計量研究所、1986年からドイツ連邦共和国の航空宇宙研究所と九州工業技術試験所との間で、それぞれ高安定レーザーを用心た超高感度センシング技術に関する研究と、耐熱性炭素セラミックスの開発とその高温特性に関する研究を、国際特定共同研究事業として実施しております。

また、科学技術協定以外にもドイツ連邦共和国のスペースラブD 2 計画にわが国の企業が参加しております。このように、研究交流の面を含め経済面全般において、ドイツ連邦共和国とわが国との間の協力関係が深まりつつあることは喜ばしいかぎりでございます。

国際的な情報化の進展、また、先進国間の多面的な協調の必要性を考える時、当 フォーラムの日独双方にとっての意義、重要性は従来にも増して大きなものになっ て来つつあります。

最後に本日から2日半にわたって開催されます当フォーラムが日独両国の研究交流に資する事を、ひいては日独関係の発展に寄与することを祈念致しまして、私のご挨拶にかえたいと思います。

#### 2.2 ギュンター・マークス 研究技術省情報処理担当課長

替様,おはようございます。まず、日本側関係者の皆様方に、この第5回日独情報技術フォーラムへのご尽力及び私共をお呼びいただきましたことに対しましてお礼を申し上げます。

ドイツ連邦共和国と日本は、盛んな輸出と高度な技術力を有する国といたしまし

て、知識と経験を交換する必要性にかられております。そのためには両国政府によって開催されますフォーラムが大変に重要な役割をはたすものでありましょう。

情報技術と言いますのは、テクノロジーの各分野の中におきましても、とりわけ 急速な進歩を遂げているという特徴を持っています。この分野で成功をおさめよう とするなら、常に目を未来に向けまして、その発展の本質的な傾向をいち早く、早 期につかむことが必要でございます。

なぜドイツ連邦共和国政府が情報技術に特に注目しているかと申しますと、その 理由としましては、この技術の持ちますその強力な広範囲に及ぼす効果でございま す。情報技術こそ、非常に広大なスケールによる製造及びサービスの基盤となるも のでありまして、これなくしては、そのような製造もサービスも考えられない、あ るいは競合力を持ち得ないものでありましょう。

この重要なポイントによって、情報技術は高度にランク付けされるテクノロジーとなっております。そして、産業と学術との協力体制及び国際的な方向性とを促しているのでございます。

ドイツと日本の企業は、市場におきましては競合相手でありまして、従って両者 が1つのテーブルに同席して意見を交換するということはそれ程簡単なことではご ざいませんでした。

しかしながら、国境を越えての協力と意見の交換があってこそ、今後の課題に打 ち勝っていけるのです。それ故に両国政府が5年前にこのフォーラムを設置する運 びとなりました。

これは1つの実験であったわけでございますが、成功した実験であると確信しております。産業と学術の専門家間のコンタクトが得られました事によって、両国政府の当面の目標はとりあえず達成されたわけでございますので、それ故に今回のフォーラムでは私達は、今後の協力体制がどのようにあるべきかについても考えていく必要があると思います。

私達は、この第5回日独情報技術フォーラムにおきましては、ニューメディア、 コンピュータ、半導体の分野での発展に関してのディスカッションを予定しており ます。これらの情報技術の核を成します本質的な分野でございます。参加者のリス トを拝見させて頂きましても、情報技術の未来についての私達のイメージをより豊かにしてくれるような、実り多い示唆に富んだディスカッションが期待できるもの と存じます。

では最後に第5回日独情報技術フォーラムが実り多く,成功裡に終わります事を 願いまして挨拶とさせていただきます。どうもありがとうございました。

#### 2.3 柳井久義 日本側議長 芝浦工業大学学長

皆様,おはようございます。今回の第5回日独情報技術フォーラムは日本におきまして,ここ京都で開催されることになりましたため,ドイツ側議長のエングル先生も多分日本語でご挨拶なさるようですので,私も日本語で挨拶させていただきます。

今回の第5回日独情報技術フォーラムが、この古都、京都で開かれることになりましたことを、たいへん嬉しく存じます。今回の日独情報技術フォーラムは第5回ということでございまして、過去4回のフォーラムでは参加者の皆様方のご協力によりましてお互いの研究、あるいは産業の状況というものや、情報技術に関しての状況というものを、たいへんよく理解し合えたのではなかろうかと思います。

第5回になりますので先ほどドクター・マークスがおっしゃいましたように、今後のあり方についても更に検討を要すると思いますが、今回はさらに情報の交換を深めるという意味において、従来同様に実りあるディスカッションが行われますことを期待しております。

それでは皆様、実りあるディスカッションを通して、仕事の面で大きな成果を挙 げていただきますと共に、また、この京都で、京都の秋を十分享受していただきた いと思います。どうもありがとうございました。

#### 2.4 ワルター・L・エングル ドイツ側議長 アーヘン工科大学教授

皆様、1984年に情報技術における第1回日独情報技術フォーラムが東京で開催されました。「討論会」の語源はラテン語のフォラムでありました。この単語は、「主会場」という意味です。このような自由意見の交換が行える、年に1度のフォーラムに発展することを確信する親しい友人達により出現したものであります。

今回は第5回目を迎え、このようなよい結果を得るに当たってご協力いただいた 方々に感謝しております。特に今までの日本側の議長であられた3名の方のお名前 を申し上げておきたいと思います。今は亡き元岡達教授、そしてやはり亡くなられ た宮川洋教授、そして現在新しい責務に挑んでいらっしゃる田中昭二教授です。

我々は変な社会に生きています。この社会はハイテクノロジーの恩恵を十分享受しているにもかかわらず、最新の技術進歩に対し反対または少なくとも恐れを感じています。高度技術革新により、ますます競争が激しくなってきている今日でありますが、これがなければ最新の技術が前進することはありえないでしょう。ただし、この場合でも協調し合う環境は重要であり、競争意識と矛盾してはならないと思います。

5年間でお互いの立場を理解し自由なアイデアを交換し、さらに友好を深めることが出来るようになったと感じます。しかしまだ改良の余地があります。今回皆様にお集まりいただいた目的の1つでもあると思います。このフォーラムは初めて京都で開かれましたのでドイツのご参加の方々へ少し話をさせていただきたいと存じます。

東京が外の世界の方を向いているのに対し、京都は未だに日本の源泉を見つめています。ですから、どうかこの機会を使って、昨日、奈良に行きましたように、京都の持つ文化遺産を訪ねるようではありませんか。皆さんの瞳を京美人の風情で楽しませ、皆さんの舌には京料理を味あわせましょう。1つだけ皆さんにお奨めしたいことがございます。真の学者魂の求めるままに冒険心を持ちなさい。観光客が通る路からはずれれば、何百という隠れた神社仏閣が静けさの中であなたを待ち、抱擁してくれるでしょう。そして、そこで平静を見いだしさらなる勤労の1年にそなえる力を取り戻しなさい。

今回の第5回日独情報技術フォーラムが両国の科学及び産業界の協調に貢献する ことを期待しております。ありがとうございました。

#### 柳井議長よりエングル議長の挨拶へのコメント

ちょっと合いの手を入れさせていただきます。ただ今エングル先生が日本語でお話になりましたが、一部の方はよくご存じだと思いますけれども日本の参加者のまだご存じない方もあろうかと思いますので、今もちろん原稿をお読みになったわけですが、その原稿は漢字及びカタカナで自分で書いておられます。そのことをご承知いただきたいと思いますのでちょっとご紹介しておきます。

### 3. 各分科会サマリー

#### 3. 各分科会サマリー

#### 3.1 ニューメディア分科会

[ニューメディア分科会日本側主査 大越孝敬]

まず最初に、過去4回のフォーラムにおける主題と討論をふりかえってみたいと思います。1984年の東京での第1回フォーラム及び1985年のベルリンでの第2回フォーラムでは、主題はかなり広範で新しい情報メディアのあらゆる局面を網羅しておりました。それらの初期の会合では、私たちの主な目的がお互いをよりよく知り合うことにあったからであります。再度東京で開かれた第3回フォーラムでは、話題は狭くなりました。光学広帯域ネットワーク及びHDTVという2つの主題が選ばれました。

昨年のシュツットガルトでの第4回フォーラムでは、主題はさらに狭められて、 発表は過去の主題の1つであるHDTVと3次元テレビジョンの研究に絞られました。

この京都会議の主題についての予備討論は、両国のコアメンバーの間で今年の4月に始まりました。ドイツと日本の間に多数のテレックスとテレファックスが往復した後に、今回は、現在強い関心のある4つの主な主題が含まれるように、話題の範囲を広げることが最終的に合意されました。それはここに示しましたように、広帯域ネットワーク及びISDN、光学スイッチ及び光学的信号処理、社会的アクセプタンス及びセキュリティ、並びにICカード、光カード及び、CD-ROMを含む新しい情報メディアであります。

次に発表の順に従いまして、話題と討論についてご報告申し上げたいと存じます。 木曜日の午後の第1セッションは、広帯域ネットワーク及びISDNが主題でした。東京大学の安田教授の最初の発表は、ビデオ送信の新しいコンセプトでるパケット形のビデオ送信機の説明でした。この計画ではビデオ情報が、パケット化されISDNまたは広域VAN、LANを通じてパケット形のメインシステムに送られます。この種の研究は、創始者の1人である安田教授を含め、世界中の多数の研究者によって現在極めて活発に行われています。 「Switching Concepts for Broadband ISDN」という表題の2番目の発表が、Siemens のシャッファー氏によって行われました。この表題は将来の広帯域ISDNにおける操作のATM(Asynchronous Transfer Mode)に関連したものでした。シャッファー氏は、このような新しいシステム技術の導入には「成長のシナリオ」とも呼ぶべきものが必要であることを強調されました。この種の大規模な社会的システムの改革には新旧システムの調和が必須であるからです。

日本電信電話の江川氏による3番目の発表は、「日本におけるISDN」とい表題で、前の2つの発表とは違って既存の狭帯域ISDNを扱ったものでした。日本でのISDN開発計画の第1段階は、1980年に始まり1985年まで続きました。この期間に得られた経験を通して、日本はCCITT(国際電信電話諮問委員会)による標準化研究に貢献することができました。そして現在日本の多くのメーカがデジタル電話端末機、高性能ファックス機など種々のISDN端末機を生産しています。今年の9月現在で、日本全国で約500名の加入者がISDNに参加しており、この数はいうまでもなく極めて急速に増加しています。

つぎの発表は、「広帯域通信の導入の概念」という表題で、西ドイツ郵電省のシュタイナー氏が講演されました。シュタイナー氏は、社会での需要量が未知であるためネットワークの計画を立てることがかなり難しく、既存の社会に広域VANを導入するのが困難なことを述べられました。そのため、発展的な形の融通性のある開発計画が再度必要とされます。そのようなダイナミックな西ドイツ郵電省の開発計画が詳しく説明されました。

つぎの5番目の発表では、ベルリンのHHIのハイト氏が、VANを含むTV放送のためのコヒーレント光学技術を説明されました。ハイト氏の主題は周波数分割多重TVまたは遠距離高精細度TV放送へのいわゆるヘテロダイン検波法の利用であり、その特徴は高い周波数選択度、迅速で効率的な同調性及び高い受信機感度であります。

HHIでの研究は1981年に始まり、1986年までには、10チャンネルの実験システムが完成し、現在ではこの計画はRACEプロジェクトの1部になっており、Philips, Siemens, HHI、Plessey, LEP、及びIMECのようなヨーロッ

パの大きな組織体がこれに従事しています。

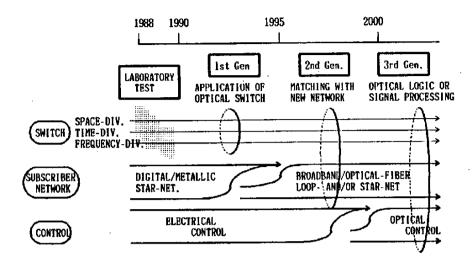

第2セッション(A)では、光学スイッチ及び光学的信号処理の技術の状況が討論されました。1番目の発表は、光学スイッチの最近の進歩という表題で日本電信電話の小林氏が行いました。遠隔通信におけるスイッチングの歴史に始まって、小林氏は音声、ビデオ、データなど各種の情報をすべて同時に取り扱うスイッチング技術、特に光学スイッチについての将来の対応を推測されました。同氏はまた、いわゆる周波数多重と時分割多重の組合せが将来有望であると推測されました。

つぎに、Universităt Münster のイエーガ教授がデジタル光学プロセッサーについて講演されました。教授は、この分野でのヨーロッパにおける計画とドイツ国内における計画の概要を説明されました。その計画というのは、「ヨーロッパ・ジョイント・オプティカル双安定性研究計画」の略称であるEJOB計画、及びデジタル光学プロセッサーについての他のBMFT、での試験研究であります。これらの計画において研究されている種々のデジタル処理技術が説明されました。

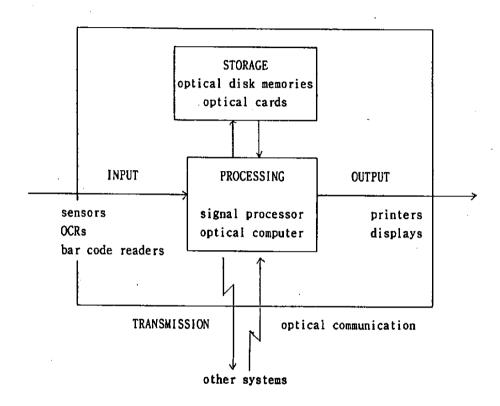

「光情報処理」と題する3番目の発表は、光産業技術振興協会(OITDA)の 石原氏が講演され、電子的方法と対比させて光学的方法の一般的な特徴を説明され ました。

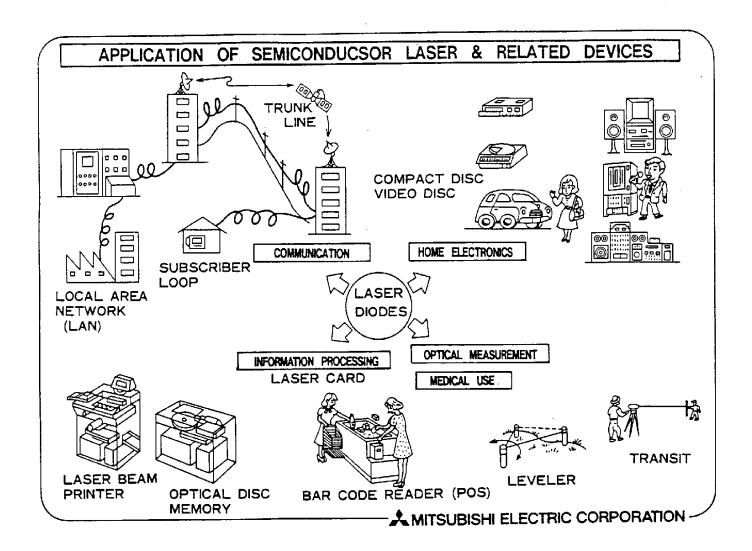

石原氏はまず、最近の既存の情報処理システムに如何に光学的方法が重要な役割を演じているかを述べられました。それは例えば記憶装置としての光ディスクや光学カード、情報伝達の手段としての光通信、読込み設置としてのバーコード及び読み取り装置としての光ディスプレーであります。すなわち石原氏によれば、オプト・エレクトロニクスに残された唯一の未開拓分野は情報処理の分野なのです。

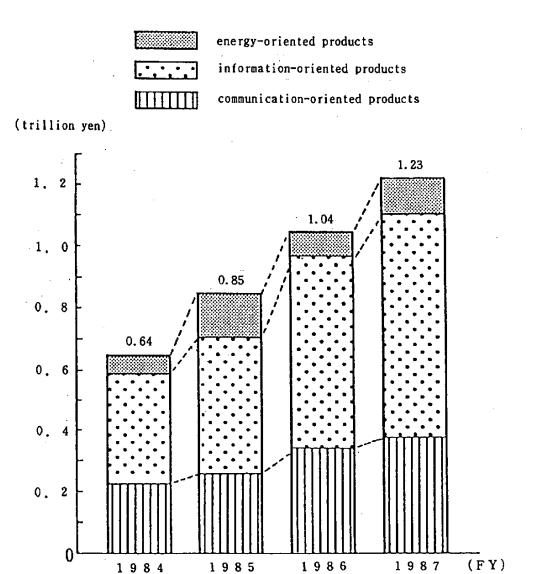

石原氏はまた、過去10年間に日本ではオプト・エレクトロニクス産業が爆発的な拡大を遂げ、1987年度の総生産額は1兆 2,300億円に達し、これは全エレクトロニクス産業の生産額の約10%であるとのべられました。

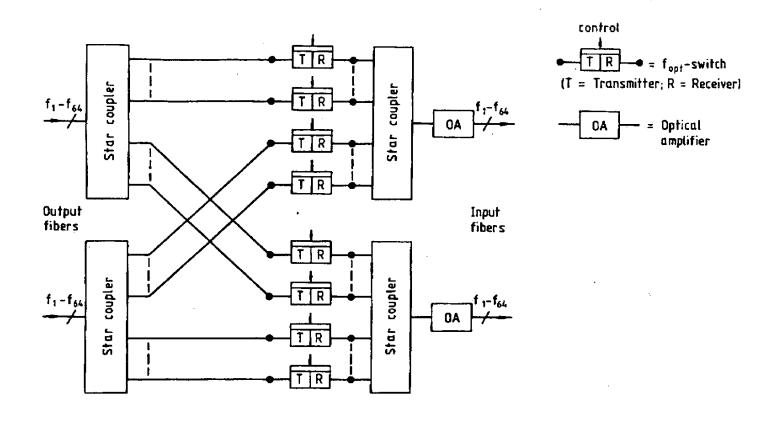

つぎに、HHIのハイト氏が光学スイッチ技術の現状を説明されました。過去及び近い未来の一般的動向の説明のあと、ハイト氏は種々のタイプの光学スイッチ、すなわち2次元、3次元及び周波数分割スイッチについて説明されました。ドイツ及びRACEプロジェクトに参加中のヨーロッパ諸国での研究活動を説明され、さ

らにこれらの研究プログラム中に開発されるべきスイッチング計画が、紹介されま した。

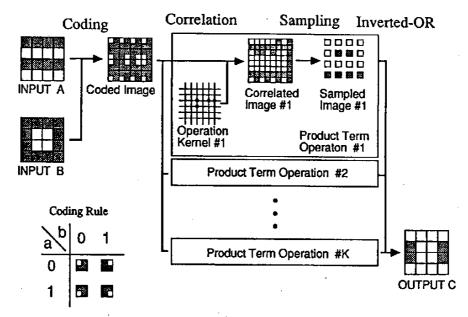

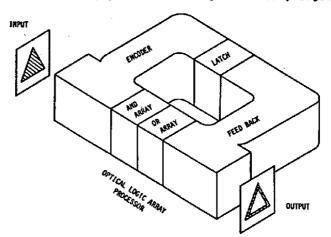

このセッションでの最後の発表は、「光学的並列デジタルコンピュータ」と題して大阪大学の一岡教授が講演されました。教授は、大阪大学の自分の研究室で考案され開発されたOPALSという光学的並列論理アレイ・システムについて主に説明されました。

その動作の1例として、日本では「迷い路」と呼ばれている迷路の正しい回答を 完全に光学的に算定する方法を説明され、聴衆に非常な興味を呼び起こしました。

第2セッション(B)の主題は、「社会的アクセプタンス及び情報セキュリティ」でした。これはやや社会科学指向の主題であります。1番目の発表は、「新情報化社会に於ける社会的アクセプタンス及びセキュリティ問題」という題で日本IBMの上園氏が講演され、情報セキュリティの問題についての考え方についての日本での一般的な状況を説明されました。そして、この主題について日本で行われた世論調査の結果を報告されました。その結論は、現在のところ日本人は一般に情報セキュリティの問題については、あまり意識していないということでした。

2番目の発表は西ドイツ郵電省のヴォルフェンシュテッター氏で表題は「ニューメディアにおける情報セキュリティ」でした。ヴォルフェンシュテッター氏はこの問題の理論的観点を説明されました。まず、セキュリティの問題を確実性の問題及び機密性の問題に分類し、西ドイツで現在進められている理論的研究について説明されました。

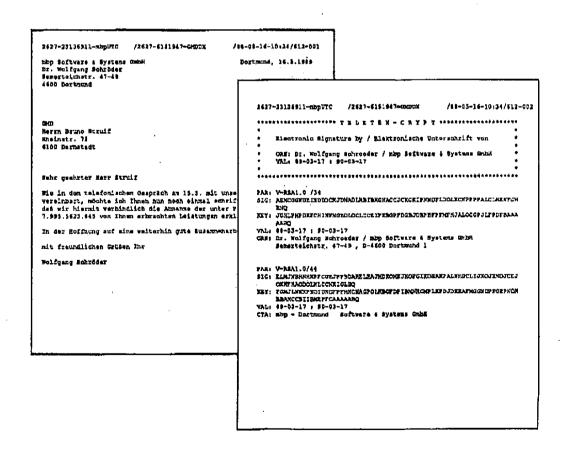

この第2セッション(B)の最後の発表は、mbp Software & Sysytems のシュレーダ氏で表題は「Electronic Signature as an Add On to the Teletex Service」でした。

電子署名(Electronic Signature)は、来たるべき情報化社会において極めて重要な技術になるでしょう。シュレーダ氏はドイツで開発中の興味あるこのシステムを説明されました。この分野に関してはドイツ人が日本人の数歩先を進んでいるように思われますし、日本の代表者は次回及びその次のフォーラムでドイツでの進歩についてもっと話しを聴きたいと感じました。

「ICカード、光カード及びCD-I、CD-ROMを含む新情報メディア」という表題の第4セッションは、「データ放送」という表題の日本放送協会の柳町氏の講演で始まりました。データ放送というのは、多分あまりよく知られていない概念であります。歴史的には、放送の対象は音声と音響から進歩して白黒のテレビジョン画像となり、つぎに完全なカラー画像になりました。将来出現すると思われるデータ放送は、符号化された情報が加入者のパーソナル・コンピュータに送られるという、放送の新しい様相であります。情報の内容はファクシミリ画像、コンピュータ音楽、パソコンのプログラム、データなど多岐にわたっています。

2人目の講演者の西ドイツ郵電省のハンメル氏で、西ドイツ郵電省によるデータ 放送の導入という題で話をされました。最初のデータ放送は実際にはいわゆるページングサービスといわれ、ユーロシグナルという名称で、1974年にフランス及びスイスと共にドイツで開始されました。これまでに 140,000人の加入者を獲得し、西ドイツ郵電省ではCTルーフと呼ばれるUHFラジオ通信用電波を使った新しいページング業務のための開発計画が、今年末に始まろうとしています。また、次の目標は現在、西ドイツで開発中の衛星を使ったデータ配送サービスであります。

つぎの3番目の発表は、「光カードの最近の進歩」という題の、オリンパス光学工業のウイリアムズ氏の講演でした。光カードは、標準的に1枚あたり2メガバイトの記憶容量を持ち、製造コストが安く大量生産できるのが特徴です。読み出し専用の光カードは、例えば小容量の電子出版に使用できます。読み出し/書き込み型のものには、医療カルテ、身分証明書、銀行カード及び保険などにわたるもっと広範囲な用途があります。

4番目の発表は西ドイツ郵電省のヴォルフェンシュテッター氏で、表題は「チップカード 一機能と用途 — 」でした。チップカードというのはとりもなおさず日本でICカードと呼ばれているものです。ICカードすなわちチップカードの歴史は1983年に遡ります。その後 5 年間、僅か 5 年の間に実に急速な進歩があり、ICカードは今やキャッシュレスの買い物、コインレスの電話通話、医療情報の記憶などの種々の用途に、また身分証明書としても使用されるようになりつつあります。

5番目の発表は、「日本におけるCD-ROMの現状」という表題で、新学社の 堀内氏が講演されました。CD-ROMとは、コンパクトディスク読み出し専用メモリーの略です。堀内氏によれば、ただ1枚のコンパクトディスクが驚くべき容量 を持ち、莫大な量の情報を記録できます。例えば、書類 250,000頁分、または書籍 2,000 冊分、またはフロッピーディスク 500枚ないし、1,000 枚分、または磁気テープ10本分に当たります。その上、例えば1枚3ドルとコストが非常に安く、CD-ROMは電子出版において強力な武器になりつつあります。

この最後のセッションの最後の発表者は、西ドイツ郵電省のシュタイナー氏でした。発表の表題は、「ビジネスの分野におけるビデオ通信」でありました。ビジネスの分野における高品質のビデオ通信は、広帯域通信の導入における重要な戦略分野であります。最初の主な用途であるビデオ会議は、既に主な先進国で導入されています。

結論として、私は2つの点を強調したいと思います。第一に、両国の技術と社会環境に関する類似点や相違点が今回の討論で非常によく理解されました。第2に、私が個人的に感じましたことは、私達日本人は比較的、機器や設置の製造に強く、それに対してドイツ人が社会と人間生活の利益と向上のために技術進歩の成果を実生活に利用することに極めて巧みであるということであります。

このセッションは非常に実り多いものであったと信じております。この機会にドイツ側のニューメディア共同議長であるHHIのバーク氏及びコアメンバーの皆様、そしてご出席の皆様のご協力に深く感謝いたしますとともに、皆様方のご好意に深く感謝申し上げます。ありがとうございました。

#### 3.2 コンピュータ分科会

#### 〔コンピュータ分科会日本側主査 相磯秀夫〕

コンピュータ分科会では3つのセッションを持ち、それぞれのセッションにおきまして原則として2つの話題をそれぞれの国から出し、討論には然るべき時間を充てられるようにしました。

第1セッションは「オペレーティング・シムテムとリアルタイム・システム」と

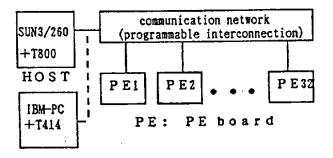

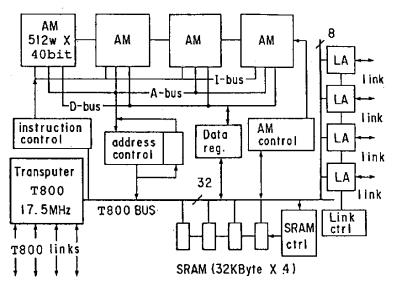

いう表題でTRON計画の概観から始まりました。TRON計画は、東京大学の坂村健助教授の指導による民間の意欲的な計画であり、日本IBMのような外資系企業を含む 118社で構成される非営利組織によって実施されています。

この計画の目的は、家庭、事務所及び産業機関を含む総合的なコンピュータ文化 を創造することであり、誰でも簡単に使えて、人間中心に設計されている点に特徴 があります。

講演者である日立製作所の伊藤氏は、この計画の背景、動機並びに潜在的な特徴を紹介され、また既に市場に出ている32ビットTRONマイクロプロセッサーの開発を含むサブプロジェクトも紹介されました。

続いて、日本電信電話の石野氏がC-TRONの研究開発に関する講演がありました。C-TRON計画は、TRON計画の最も重要なサブプロジェクトの1つであります。石野氏は、まずコンピュータと通信の影響について述べ、その効果的な実施のために幾つかの層からなる階層構造について論じ、最後にC-TRONの特徴を紹介しました。

ドイツ側からは、GMDのグース教授が現在GMDで開発中のBirlixオペレーティング・システムについて講演されました。グース教授はまずUNIXの中枢機能の不足を指摘され、この計画の目的を紹介されました。この計画は、現行のUNIXオペレーティング・システム中枢の機能不足を補うことを目的としています。設計の原理は、オブジェクト指向及び拡張可能という概念に基づいており、そのインタフェースはネットワーク指向機能の導入と機密保護、及びフェイルセーフ機構の実装に特に重点を置いており、現在のバークレイUNIXに対応しています。それはポストUNIXのオペレーティング・システムと思われます。

第1セッションの最後の講演は、Siemens のゲバルト氏のX/Open:OpenUNI X環境の紹介でした。ゲバルト氏はUNIX OS分野における事実上の標準規格 の定義とその意味について説明しました。また非営利的な研究開発コンソーシアム で行われている国際的なX/Openプロジェクトを紹介されました。<math>X/Openの目的 は、現存の標準規格または事実上の標準規格を共通の利用環境に適応させ採用する ことであって、新しい規格をつくることではありません。X/Openは、POSIX

プログラム言語、データ管理、ユーザー・インタフェースなどのような現存オペレ ーティング・システムのインタフェースの標準化に焦点を当てています。

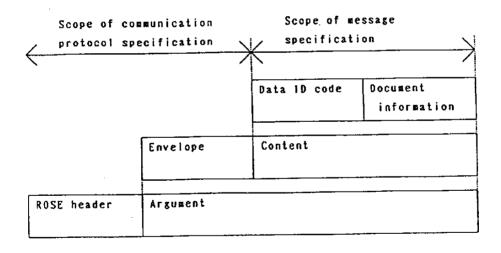

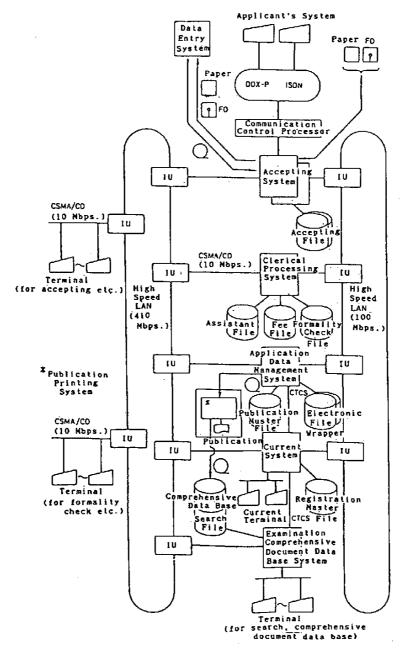

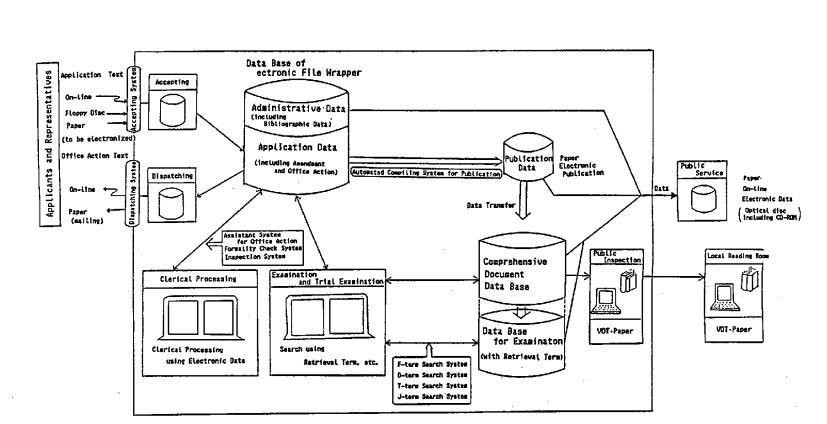

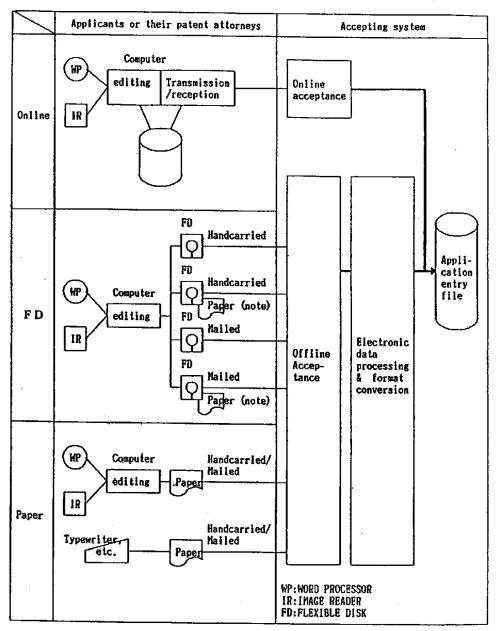

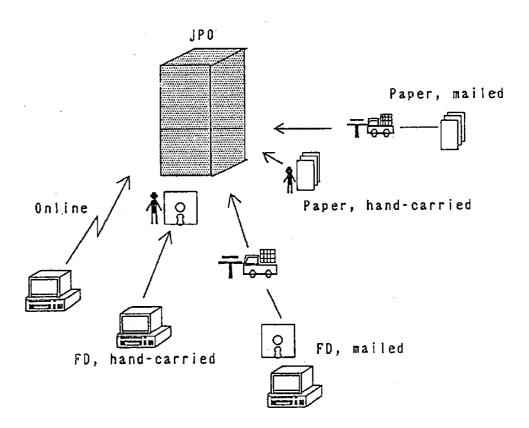

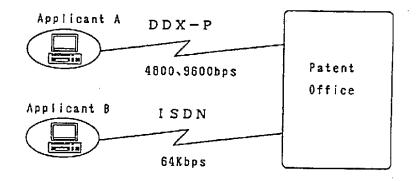

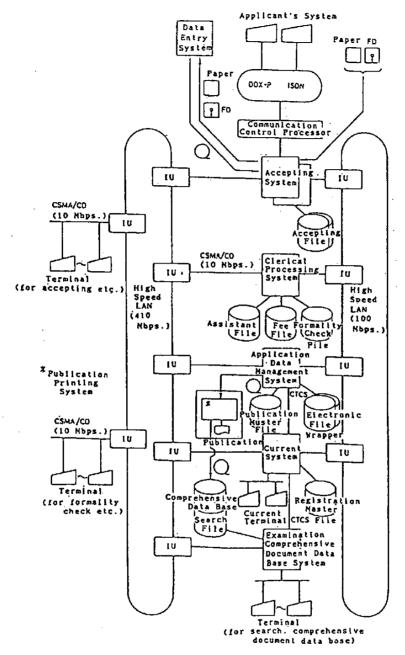

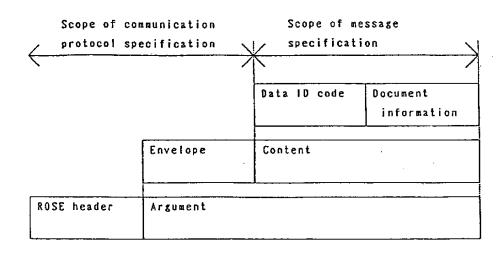

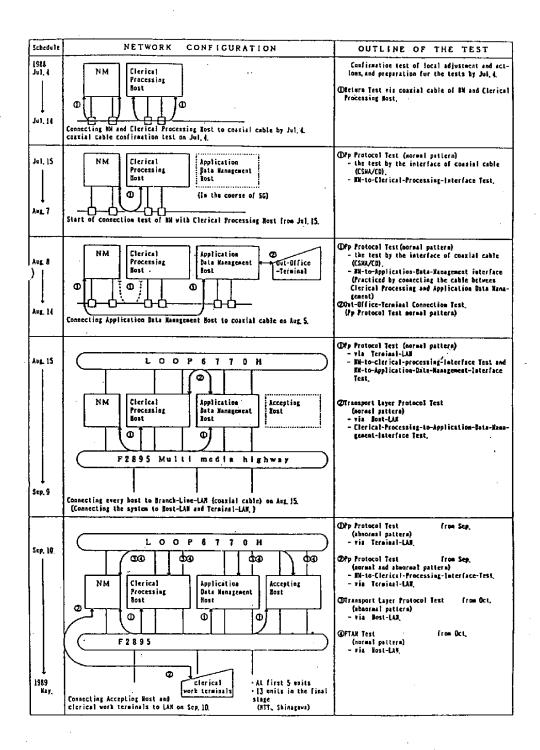

第2セッションでは、高度情報技術の応用についての最近のトピックスについて 討議されました。このセッションの最初の講演は日本の特許庁の石井氏の行ったオ ープンシステムの接続(OSI)概念に基づく電子特許出願システムの説明でした。 この計画の目標は、日本での書類提出によらない電子式特許出願制度の受け入れに あります。石井氏は、そのような大規模なシステムの開発の必要性を説明され、シ ステムの構成を紹介されました。このシステムは、OSIプロトコルの規格に基づ いて設計され全国的な大規模ネットワークと多数の高性能ワークステーションから 構成されています。これは、1990年の春先からの使用が予定されています。

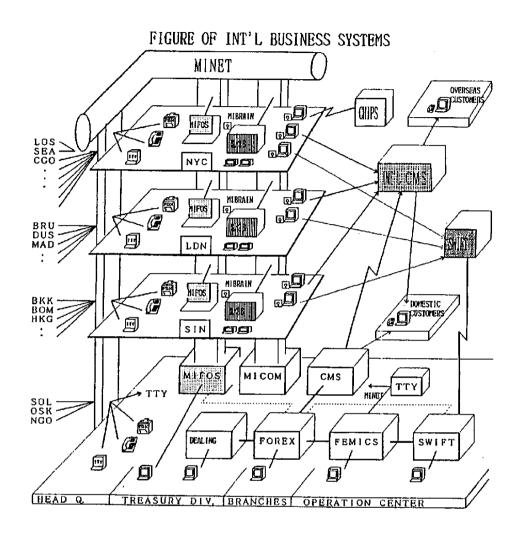

三井銀総合研究所の岩丸氏は、世界中で最も進んでいると認められている。日本の国際オンライン銀行業務システムについて講演されました。岩丸氏は日本の銀行業務システムの過去、現在及び未来を紹介されました。まず銀行業務の分類に始まって将来実施されるべき銀行業務システムの必要条件を指摘されました。また、3世代にわたるコンピュータ・ネットワーク及び情報処理システムによって支えられた日本の銀行業務のサポートについて詳しく説明されました。

現在の第3世代三井銀行業務システムは、世界中に接続されたコンピュータ・システムですが、地震による緊急災害にそなえて、同じバックアップ・コンピュータ・システムを他に準備しています。

ドイツ側からは、University of Saarbrucken のヴァルスター教授が知識ベース応用システムのためのインテリジェント・インタフェースについて興味ある講演をされました。ヴァルスター教授は、図形、ジェスチャー、自然言語、メニュー、スケッチング及びビデオが扱える高度な機能を持つエキスパートシステムに対するマルチモーダル・インタフェースの説明をされました。教授は、日本で研究の努力がほとんどされていないヒューマンインタフェース研究の重要な役割を強調されました。講演は、ドイツにおける他のインテリジェント・インタフェース計画の概要についても話されました。

Siemens のホーヴァイン氏は、工業オートメーションにおける知識ベース技術に

ついて講演されました。工業オートメーションの複雑化にともない、コンピュータ 支援設計(CAD)及びコンピュータ支援製造(CAM)の開発に対する要求が急 速に高まってきております。ホーヴァイン氏は、工業オートメーション、特に圧延 機のオートメーションにおける有用な知識ベースシステムの幾つかの例を紹介され ました。また、知識取得、ドキュメント処理及びその提供に使われるエキスパート システムの利用について説明され、効率向上の評価を通して開発されたシステムの 有用性を実証されました。

第3セッションでは、大阪学院大学の大村教授が映画及びアニメーションの製作に使用されるLINKS-2と称する専用マシンの概要を説明されました。アニメーションや映画の製作には普通膨大な計算時間がかかり、しかも芸術家にも複雑な仕事の負担を与えるものですが、そのような厳しい問題を軽減するためにこの計画は始められました。提案されたマシンのアーキテクチャは、むしろ簡単なものですが、自動アニメーション作業のために特殊化されたものであります。この専用マシンは近い将来、約1000台の処理装置から成る強力な大規模マルテプロセッサ・システムになるはずです。大村教授はまた、芸術家のようなコンピュータの専門家でないユーザが専門の知識なしにシステムを使えるような、簡単で使いやすいユーザ言語を提供するとの必要性を説明されました。

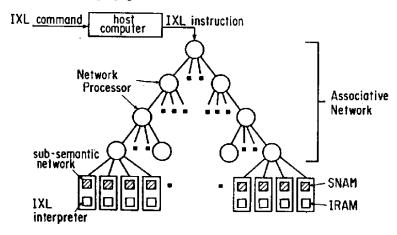

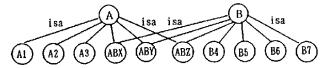

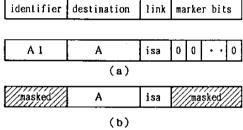

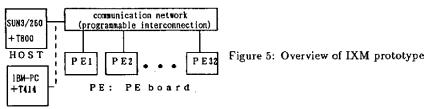

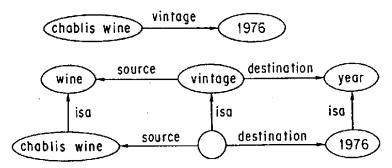

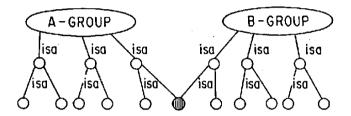

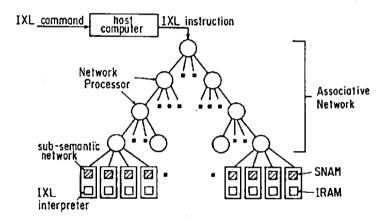

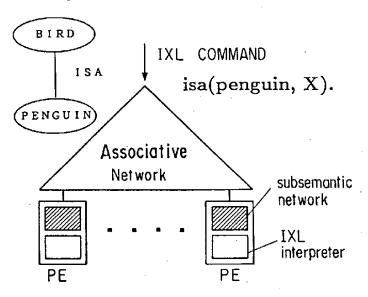

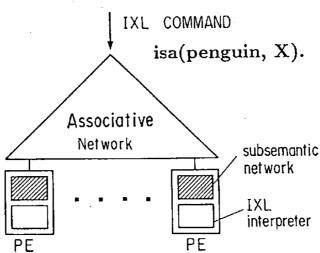

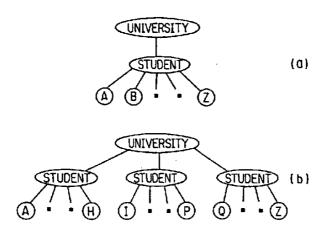

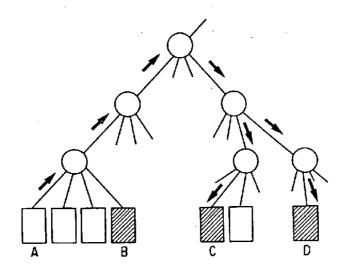

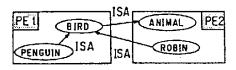

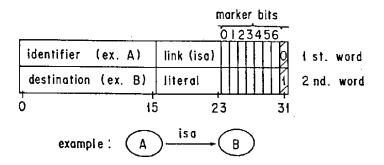

電子技術総合研究所の樋口氏は、セマンティック・ネットワーク・マシンIXMの計画について概要を説明されました。セマンティック・ネットワークは、人口知能問題にしばしば見られる知識の階層構造を理解するのに便利です。しかし、一般にセマンティック・ネットワークの処理には時間がかかり、普通のコンピュータではセマンティック・ネットワークに含まれる潜在的な並列性を効率的に利用することができません。樋口氏は、この問題を解決するため、セマンティック・ネットワークを効率的に処理するために多数の連想メモリを持つ大規模な並列処理アーキテクチャを提案しました。同氏は設計理念、機能の特徴及びアーキテクチャについて説明し、シミュレーションによって期待される性能を提示されました。

ドイツ側からは、SUPRENUMのゾルヘンバッハ氏がドイツの科学計算用スーパーコンピュータを紹介されました。スーパーコンピュータは、学問及び産業の

両分野で必須の道具であることが認められており、そのため種々のプロジェクトが 各国で活発に行われています。

ドイツのスーパーコンピュータは、SUPRENUM研究所という名の共同体で開発され、そのスーパーコンピュータはすでに市販されています。同氏はまず、応用プログラマーの観点からスーパーコンピュータについて重要な分類カテゴリーについて説明され、SUPRENUMのアーキテクチャ、ハードウェア、ソフトウェア、及びSUPRENUMのスーパーコンピュータの将来の構想を紹介されました。

第3セッションの2番目の講演者としてGMDのジロア教授が、順次プロローグ言語の並列処理のためのアーキテクチャについて説明されました。このシステムは並列演算のプロローグ・エンジンが付加された通常のUNIXワークステーションから成っています。エンジンは最適化された順次プロローグ・プログラムを実行するように設計されたパイプライン方式のユニフィケーションプロセッサから成り立っています。提案されたアーキテクチャは簡単なように思われますが、実際の観察に基づいて設計されたものです。これは現存の単一プロセッサーのプロローグマシンに比べて速度において決定的な利点をもっています。

第3セッションの最後に、University of Mainz のフォン・ジーレン教授がニューラルネットにおける計算と題する講演をされました。ニューラルネットの概念は、例えば多次元最適化問題、イメージ処理やパターン認識の研究に有効であることがよく知られています。また、ニューラルネットワークが大規模並列計算処理と密接な関係にあることを指摘しました。それは耐故障性の向上とゆるやかな性能低下を伴なう連続稼働の可能性を与えます。フォン・ジーレン教授は、計算ステップ、信号の冗長性の利用及び信頼度などの点について工学的システムと生物学的な神経系との関係を説明されました。そして、生物学的な情報処理の実例を示し、生物学的システムに見られる類の並列処理が、例えば、ビジョン処理に使用される工学システムにも活用できることを説明されました。

結論としまして、今回のフォーラムはお互いに有用な情報の交換が、でき、大変 有益なものでありました。講演者並びにセッションの運営に関与されました方々に 厚くお礼申し上げます。有難うございました。

#### 3.3 半導体分科会

#### [半導体分科会日本側主査 菅野卓雄]

半導体分科会で行われました各発表を要約したいと思います。ドイツ側の半導体 グループを統括されているルプレヒト教授が今年はご病気のため来日されなかった のは残念でございます。しかし、私たちはこの2日間本当に有益な研究会を持つこ とができました。

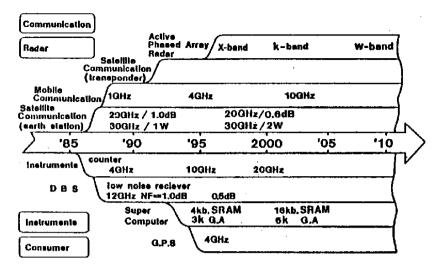

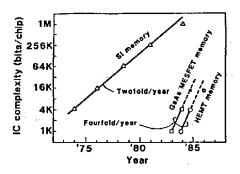

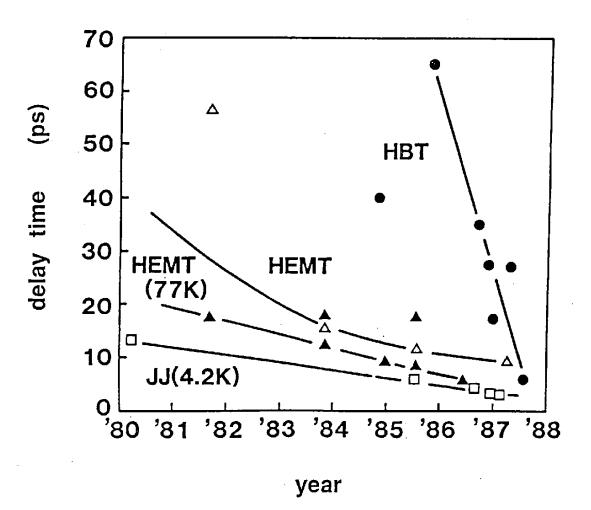

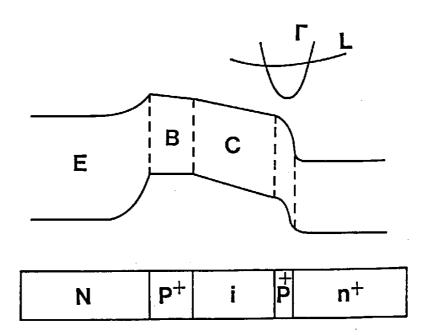

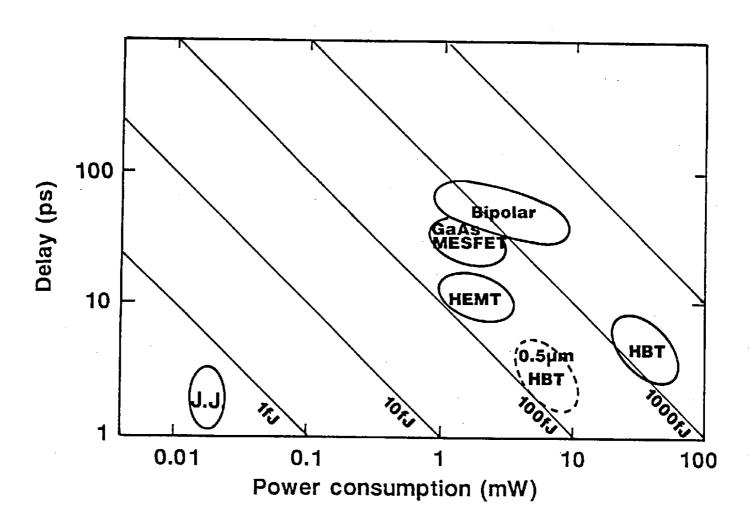

今年、私たちは3つの主題に議論の焦点を当てたいと考えました。その第1は特に遠距離通信用への半導体技術の応用であります。それで、第1セッションの表題は「ミリ波IC」及び「光データリンク」でした。また、私たちはⅢ-V族半導体技術の将来の見通しについてアイデアを得ようと思いましたので、第2セッションの議題は将来の情報システムにおけるⅢ-V族化合物半導体デバイスの役割ということになりました。もちろんシリコンは高速度デジタル用途でもⅢ-V族化合物半導体と競合しますので、第3セッションはサブピコ秒シリコン・オプトエレクトロニック・スイッチを含む高速度シリコンデバイス及び回路でした。

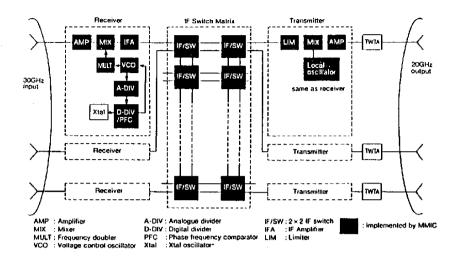

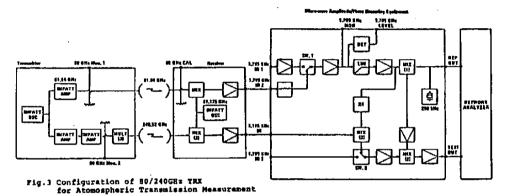

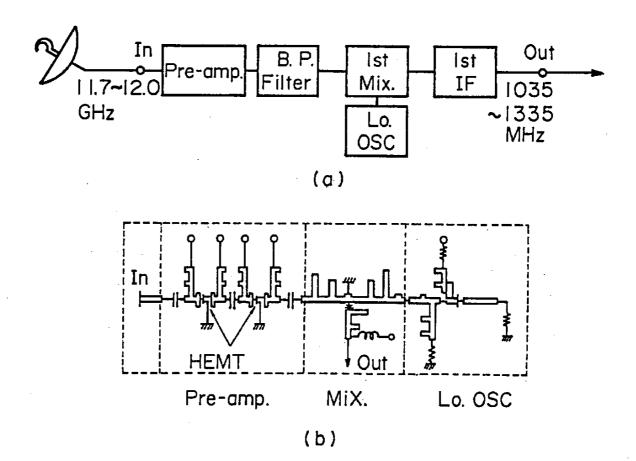

第1セッションの「ミリ波 I C 」及び「光データリンク」では、ミリ波 I C または30 G  $H_2$  V A N について 2 つの発表がありました。

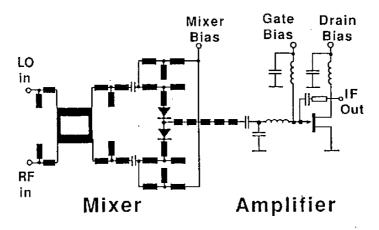

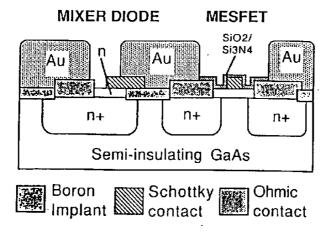

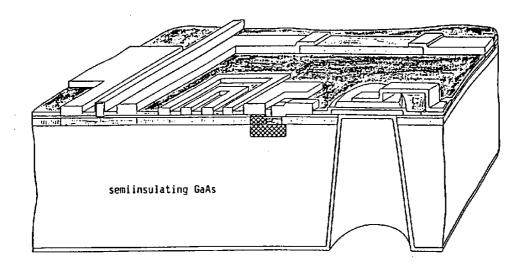

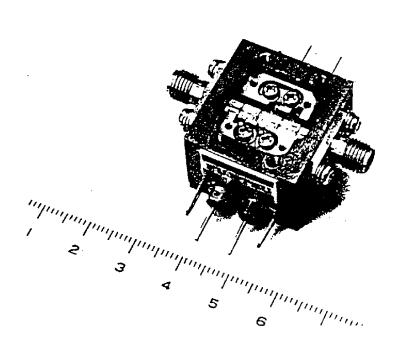

最初に日本電信電話の加藤氏、つぎにAEGのメンツェル氏が発表され、かなりよく似た技術開発が両国で行われていることがわかりました。日本では、加藤氏が衛星応答機用のモノリシック・ガリウム砒素ICを説明されました。加藤氏は、主要モノリシック・マイクロ波ICのためのこれらの5割のガリウム砒素ICが0.3ないし0.5ミクロンゲートのガリウム砒素MESFET及びショットキー・バリアダイオードを使用していることを報告されました。

メンツェ氏の発表でも、ガリウム砒素MESFET及びショットキー・バリアダイオードからなる35GHz受信機チップが報告されました。メンツェル氏は、周波数範囲を35GHzから60さらに94GHzにまで拡げる努力について報告されました。この努力にはHEMT増幅器の使用も含まれています。

3番目の発表もミリ波 I C でしたが、遠距離通信用だけでなく種々の用途につい

てでした。この発表では、工学試験衛星 6 号のためのミリ波送信システムが報告され、このシステムには38 GHzでの出力が 0.5 ワットの固体高出力増幅器と43 GHzでの雑音電波が 4.8 dBの低ノイズの増幅器が含まれています。

第2の用途は、核融合研究用の日本の原子炉であるJT60中でのプラズマの電子 温度を測定するためのミリ波送信システムを使ったプラズマ診断であります。

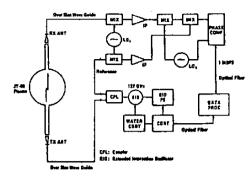

またもう1つの用途は大気中の伝搬の測定であります。このシステムでは2つの周波数が使用されました。すなわち2つの周波数の間の相互の位相シフトを測定するために80及び240GHzが使用されました。2つの周波数はもちろん位相の差を測るために干渉性であります。この興味あるデバイスは、アルミニウム・ガリウム砒素のヘテロMISゲートFETであり、このデバイスの性能の特徴は38GHzで8.1 dBという高い信号出力利得がえられたことであります。

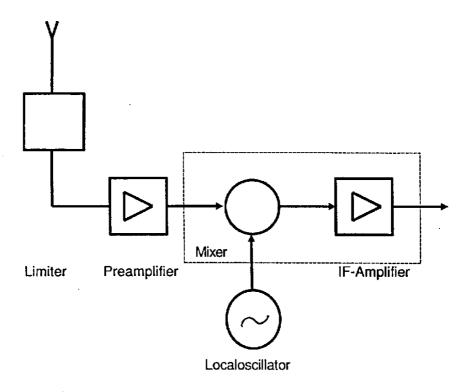

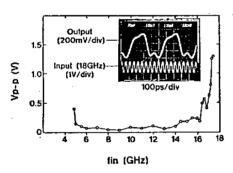

第1セッションの最後の発表は、SELのハイデマン氏でした。ハイデマン氏は、 光伝送技術の進歩並びに、毎秒5ないし10ギガビット伝送及び未来システムの可能 性、すなわち高速度信号処理技術の能力の可能性とシステムの限界と概要について 極めて広範の議論を行われました。もっとも顕著な成功はドイツで達成されました。 それは、分散シフトシングルモード光ファイバーを使った 111キロメートル用の5 ギガビット/秒の光通信であり、1.55ミクロンの分散フィードバックレーザが使用 されています。この成功は同氏自身によって達成されました。

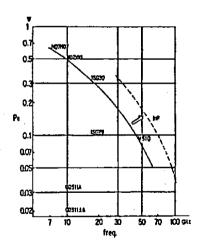

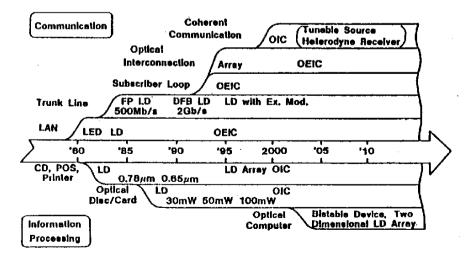

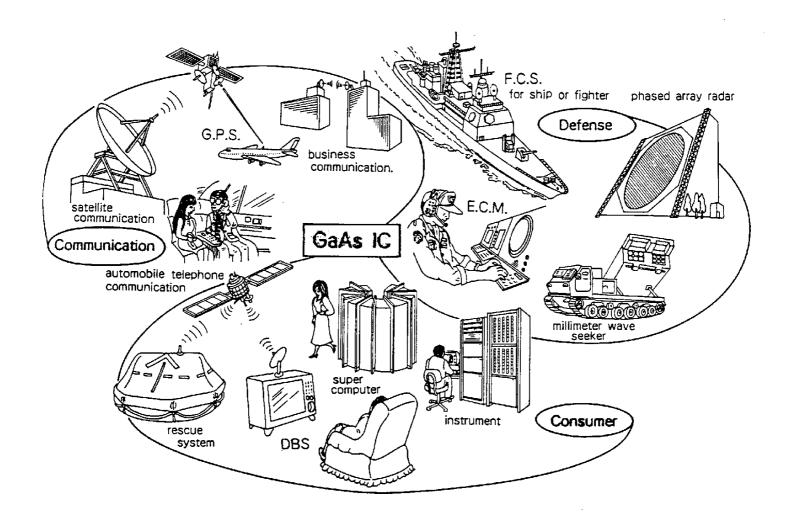

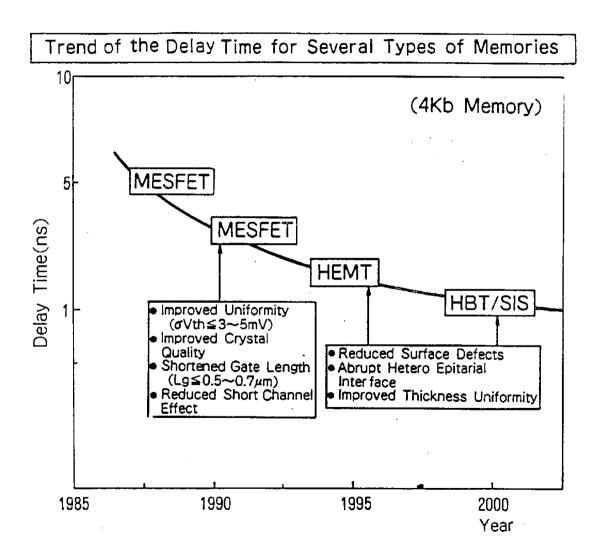

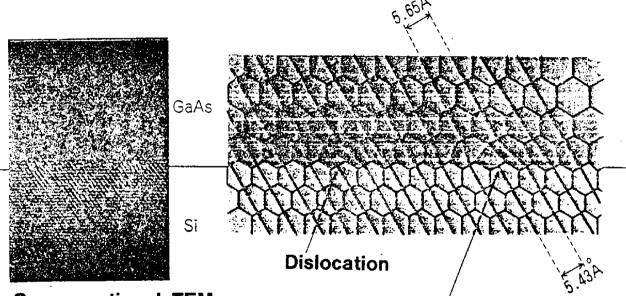

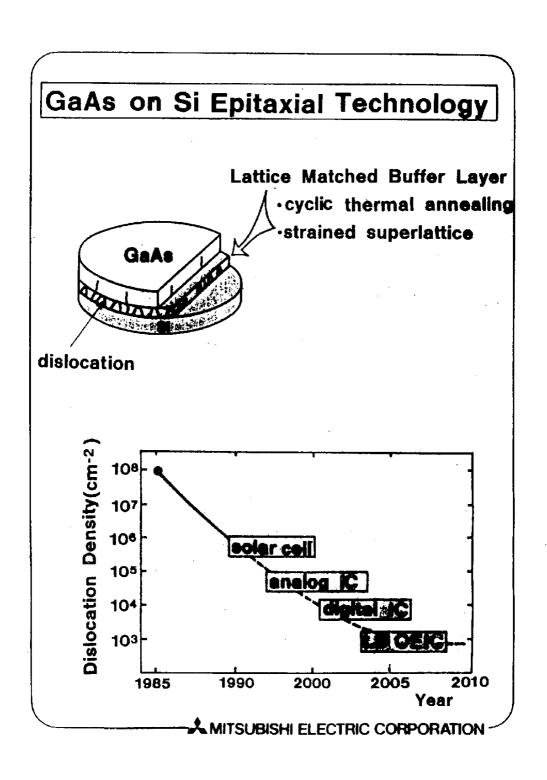

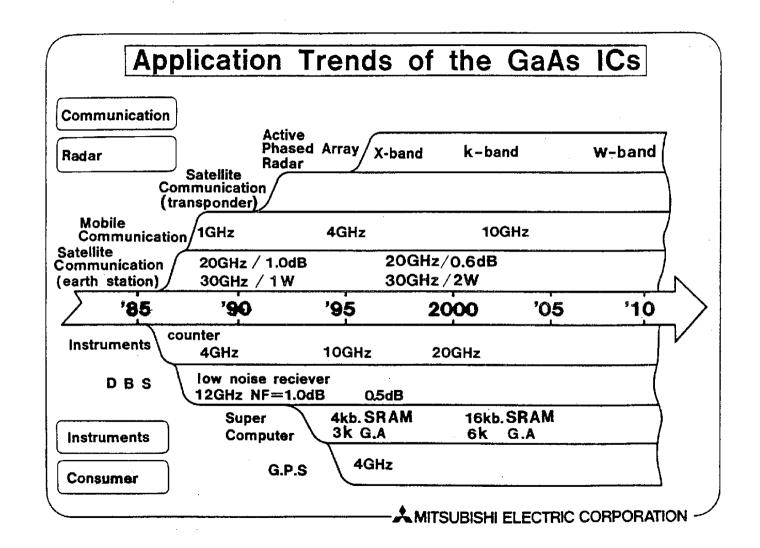

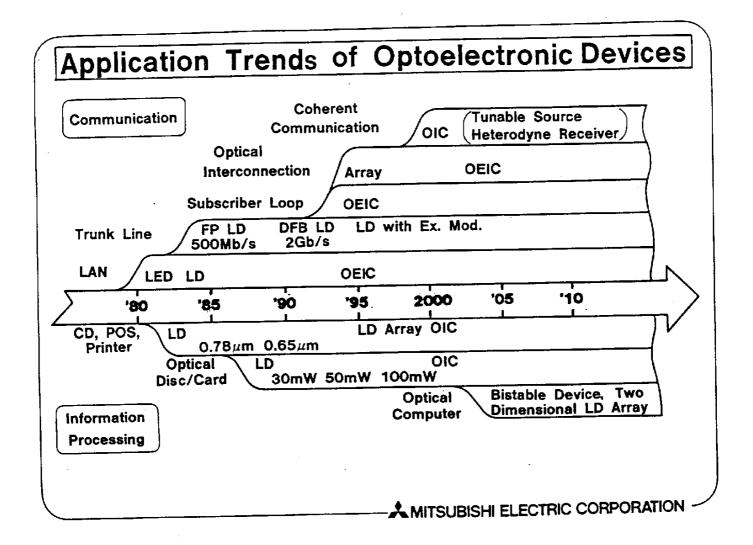

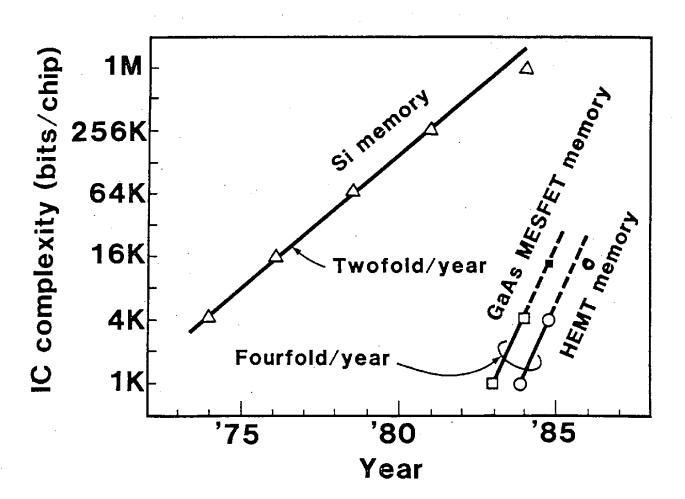

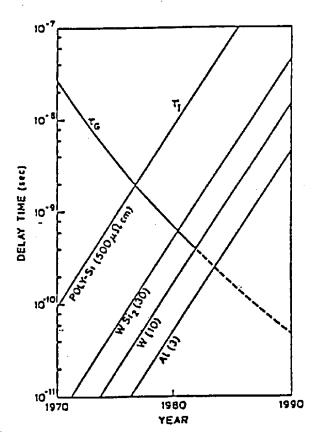

つぎにガリウム砒素技術の将来について論じることになりました。これは、三菱電機の柴山氏が講演されました。ガリウム砒素LSIの利用の動向および光コンピュータの話から始められ、そのあと、ガリウム砒素と光デバイスの技術動向が説明されました。現在ガリウム砒素ICを使用している実用的なデバイスは、ご存じのようにMESFETですが、3年以内にHEMTや自己整合型のFETが多分実用化され1995年にはヘテロバイポーラ・トランジスタがガリウム砒素ICに使用される実用的なデバイスになるだろうと述べられました。光デバイスの分野では、二重ヘテロ接合レーザが現在実用されていますが、ここ2、3年の内に量子井戸レーザが使われるようになるでしょうし、1993年には量子井戸レーザや量子ワイヤー、量子ボックスが使用されるでしょう。この討議はガリウム砒素デバイスのそのような

未来の展望について行われました。

何人かの人は柴山氏が光デバイスの将来についてかなり楽観的であると感じたでしょう。しかし、今朝私はTVと新聞で三菱電機が機能、光接続を持つメモリチップをガリウム砒素で実現したことを発表したことを知りまして、同氏がガリウム砒素IC技術への光技術の応用に自信をもっておられることがわかりました。同氏は過去に予測された市場はあまりにも楽観的すぎるとも言われました。今年の実際の市場規模は予想のちょうど半分であります。

2番目の発表は、Siemens のプラッデル氏でした。同氏は、将来の情報システムにおけるガリウム砒素の役割について述べられました。プラッデル氏は、半絶縁性ガリウム砒素の品質を向上させる努力を報告され、ガリウム砒素へのベリリウムのドーピングの有用性を強調されました。鉄ドーピングのデバイスでは、個別デバイス、小信号マイクロ波及びデジタルIC及びエピタキシャルデバイス、HEMTのパワーデバイスなどが説明されました。

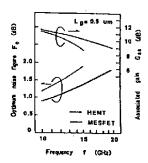

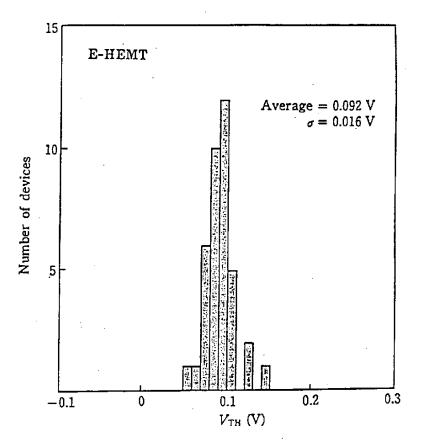

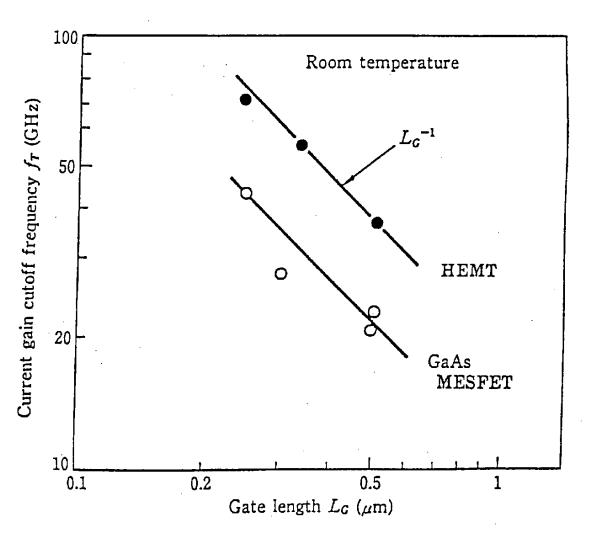

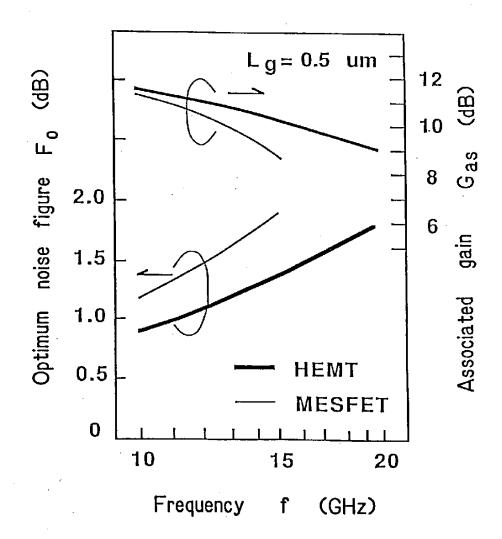

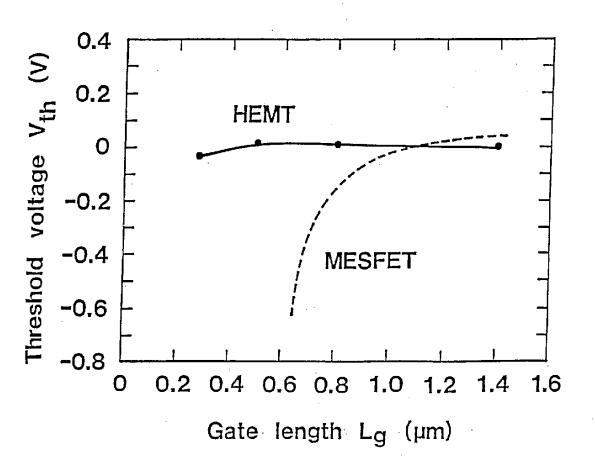

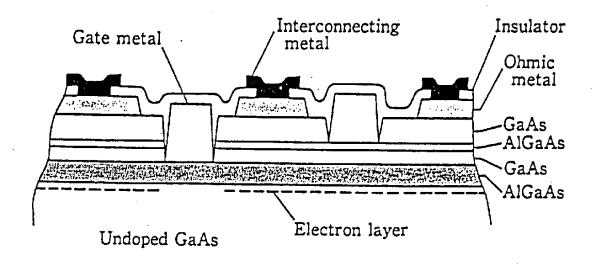

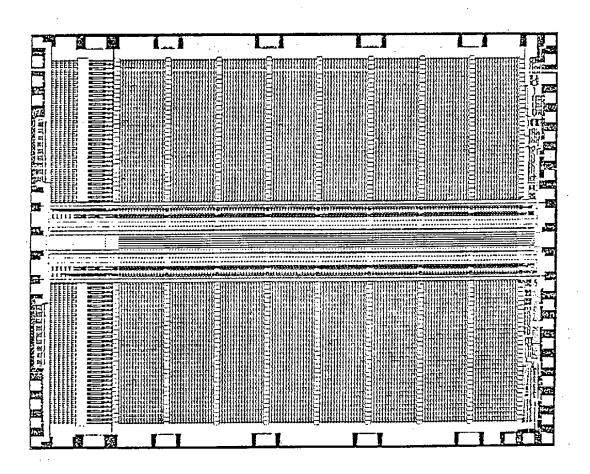

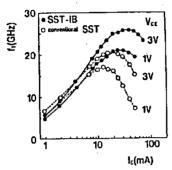

重要な成功の1つは、0.5ミクロンのデバイスの製造にIーラインステッパーを使うことでした。つぎに、富士通研究所の太宰氏がHEMT及び関連の新しいデバイス技術を説明されました。同氏は、現状と将来の動向及び将来の高速度システムに対するこれらのデバイスのインパクトの可能性を説明され、これらのデバイス技術の分野における富士通研究所の大きな成功について説明がありました。例えば低ノイズHEMTは現在20GHzで1.8dBの雑音指数であり、HEMT、LSIの例として16Kbit SRAMがHEMTで構成されています。このSRAMのアクセス時間は77°Kで3.4ナノセカンドであると報告されました。

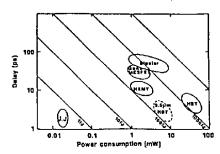

優れた成果の1つは、ヘテロバイポーラトランジスタによる高速度スイッチングです。太宰氏は、2.6 ピコ秒の遅延をゲートあたり60ミリワットの電力消費で達成したと報告されました。私の知る限りでは、これは接合デバイスで得られた最高の速度であり、ほぼジョセフソン接合技術に匹敵するものである。

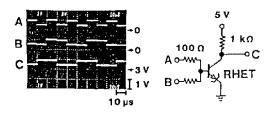

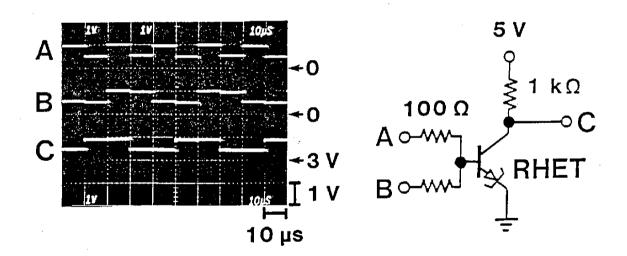

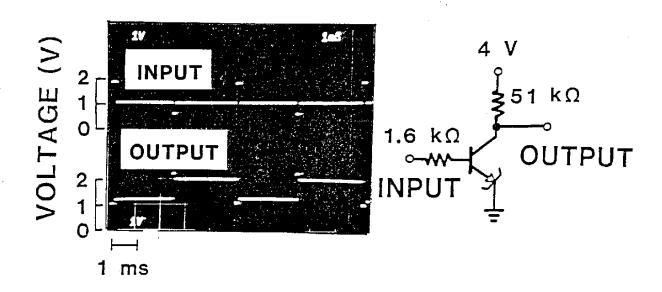

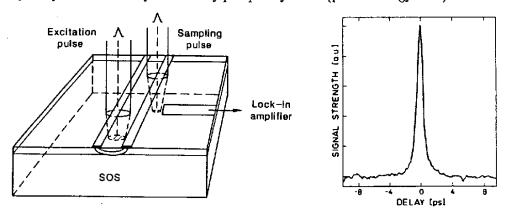

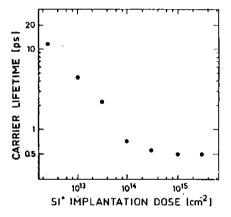

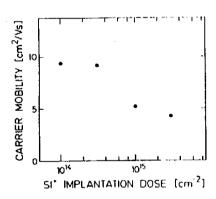

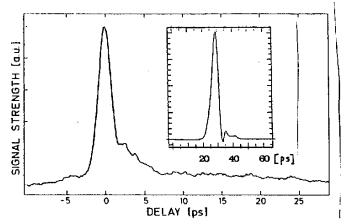

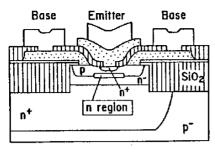

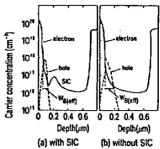

共鳴エミッタRをもつホット・エレクトロントランジスタはRHETと呼ばれ、 機能デバイスの一種であり単一のデバイスで排他的論理和回路を造ることができ 1ピコ秒のスイッチングの達成が期待されています。 4番目の発表は、MPIのラムスドルフ氏でピコ秒のシリコンスイッチの説明でした。ラムスドルフ氏は、SOI構造を使用したシリコン・スイッチで88フェムト秒のレーザーパルスから1ピコ秒の電子パルスが発生することについて報告されました。このSOIは、キャリアの寿命が0.5ピコ秒にまで短縮されるように、サファイアの上に0.5ミクロンのシリコン膜を堆積させたものであります。

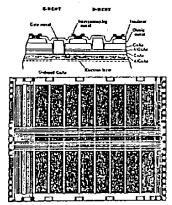

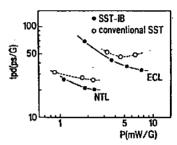

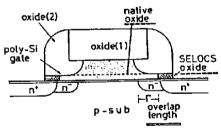

最後のセッションでは、シリコン・デバイスの将来の見通しについて討論しました。1番目の発表は、高速度シリコン・バイポーラトランジスタの分野でよく知られた研究者である日本電信電話の酒井氏です。同氏のお話は超高速度LSIのためのバイポーラ技術に集中されました。

昨日、酒井氏は選択的イオン打ち込みコレクターいわゆるSICを持つスーパー・セルフライン・トランジスタの新しい構造を報告されました。SIC製造を使う事によって $f_T$  は従来のスーパー・セルフライン・トランジスタのほぼ半分に低減できます。またSIC構造を使うことによって高電流密度におけるベースのプッシュ・アウトが避けられました。それで、SIC構造によってスーパー・セルフライン・トランジスタ(SST)は、21ないし26 GHz という高い遮断周波数とゲートあたり25 ピコ秒のスイッチングが達成できることが示されました。

つぎに、Siemens のクローゼ氏も高速度シリコン・デバイス及び回路についての報告をされ、バイポーラ技術について非常に広範囲にわたる議論をされました。同氏の結論は、バイポーラトランジスタが高速度回路の中程度の複雑さに大変適しており、バイポーラ技術の動向は25 GHzより高い遮断周波数を得るため、Bi-CMOS技術が複雑な回路に最適であるということであります。また氏はBi-CMOS技術の現況についても説明されました。256 Kbit SRAMが日立製作所とTIで製作、開発され、また1 メガDRAMが日立製作所で開発されました。

Bi-CMOSの動向とともに、ECRとCMOSの組合せ、そして他のマイクロセルの応用が有効となると期待されています。

次に、日立製作所の武田氏がVLSIを超すULSI、ULSI-MOSデバイスの現状と将来の見通しについて講演され、64メガビットDRAMのための技術革新が0.3ミクロンの技術を使って開始され、IBMは最近、スタティック論理回路

で 0.1 ミクロンゲートのMOSFETを用い10ピコ秒より短いスイッチング遅延の 達成を発表したと説明されました。

現在の時点ではDRAM用MOSFETには0.3ミクロン、論理用には0.1ミクロンが実用的な目標でしょう。博士はまた、0.1ミクロン未満の厚さの極薄のシリコン膜で造られているSOIデバイスが将来のMOSデバイスに非常に有用であることを強調されました。SOI構造を使うと短チャネル効果の抑制が期待されるからであります。武田氏はまた、シリコン・デバイスでの量子効果の可能性を述べられました。そのような量子効果はチャネルの長さが0.1ミクロン未満の小チャネルデバイスで観察されます。

量子効果の例は、ドーパントの不純物の統計的な変動であり、このためMOSF ETのしきい電圧が変動し、チャネル内で電子の速度のオーバーシュートがあり、 またチャネル内でのコンダクタンスの異常な変動が起こります。

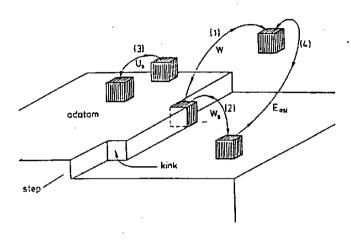

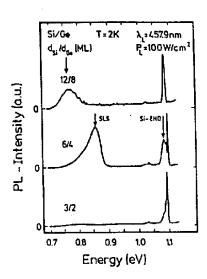

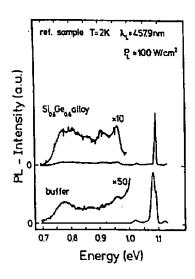

最後の発表は、AEGのカスパー氏のよって行われました。氏は、シリコンの低温分子ビームエピタキシ法の広範な議論ともちろん同氏自身の研究を説明されました。現在(100)シリコン表面で 150ないし 300℃という低い最低エピタキシャル温度が報告されており、もっとも顕著で目ざましい効果は、シリコンゲルマニウムの格子構造の層の中のホール移動度の増加であり、また超薄膜のシリコンゲルマニウムのスーパーラテイス内の直接遷移の著しい増加であります。

この直接遷移の著しい増加は、オプトエレクトロニクスの分野へのシリコンデバイスの利用の新しい可能性を開くものであります。

以上が半導体分科で行われた発表の要約であります。私は各発表者の方々に対して当然申し上げるべき賞賛の言葉に欠けるところがあったかもしれません。お許し下さい。ご協力有難うございました。

|   |     | • |

|---|-----|---|

| , |     |   |

|   |     |   |

|   |     |   |

|   |     |   |

|   |     |   |

|   |     |   |

|   | . * | • |

|   | ·   |   |

|   | ·   |   |

|   |     |   |

|   |     |   |

|   |     |   |

|   |     |   |

# 4. 閉 会 挨 拶

|  |   |  | • |   |

|--|---|--|---|---|

|  |   |  | • |   |

|  |   |  |   |   |

|  |   |  |   |   |

|  |   |  |   |   |

|  |   |  |   |   |

|  |   |  |   |   |

|  |   |  |   |   |

|  |   |  |   |   |

|  |   |  |   |   |

|  |   |  |   |   |

|  |   |  |   |   |

|  |   |  |   | • |

|  |   |  |   |   |

|  |   |  |   |   |

|  | , |  |   |   |

|  |   |  |   |   |

|  |   |  |   |   |

|  |   |  |   |   |

# 4. 閉 会 挨 拶

# 4.1 柳井久義 日本側議長 芝浦工業大学学長

それでは閉会の言葉を述べさせていただきたいと思います。私に続きましてエン グル議長もご挨拶をされますので、重複をさけるため私はおもに日本人の方々に日 本語でご挨拶させていただきたいと思います。

おはようございます。日本の皆様たいへんありがとうございました。お陰様で、 ただ今の各分科会の報告のありましたとおり、たいへん有効なフォーラムが持てま したことをうれしく思っておる次第でございます。今後ともこのフォーラムを発展 させて、日独友好のためにさらにご協力いただきたいと思います。

フォーラムの各分科会は今報告があったとおりでございますが、このフォーラムの間におきまして、次回以降のフォーラムの在り方という問題を、各分科会チェアマン並びにコアメンバーの方々及び研究技術省と通商産業省の方々とご相談してまいりました。その結果といたしまして、従来どおりこのような方式で、少しずつ改良を加えながら発展させて行こうと言うことについては意見が一致しております。すなわち、その場合、相互に有益かつ適切なテーマを選定して行こうではないかということ、また必要によってはセミオープン方式でフォーラムを開催して行くのも良いのではないかということ、あるいは、各分科会ごとに運営方式がある程度違っても良いのではないかというようなことなど、このような改善をしながらさらにフォーラムを発展させて行きたいというふうになっております。

一方におきまして、両国の研究協力あるいは共同研究を導入していくようなことも、フォーラムの成果として挙げていきたいということが話あわれました。これは、このフォーラムの発足時から望まれていたことでございます。お互いの情報交換、あるいは、人的な友好関係の強化という点ではかなり進んでまいりましたので、ぼつばつ両国の研究協力とか共同研究のようなものに発展させることも考えていったらどうだろうかということでございます。そこで取りあえず次のような形で始めてみたらどうかということであります。取り上げる分野は、当然インフォメーション・テクノロジーの範囲に限定する。それから日独を主体とした2国間協力を主体

にする。しかし必ずしもそれにこだわるものでもない。さらに、これは急には行き ませんが、新しく国あるいは産業界からの援助を求める。しかし既存の制度はでき るだけ積極的に利用して行くようにする。ただそういうような形の援助ということ にはあまりとらわれないで、お互いに研究協力、あるいは共同研究を進めてみるこ とを考えてみようではないかということであります。そのためにまず、両国にとっ て協力が望ましいと考えられるような基礎研究分野につきまして,そういう問題が あるかどうかというのを抽出してみる。そして、そういう分野、問題で両国のコア メンバーの方々が、自分の国の中で関心が高くて積極的に研究を進めておられるよ うな機関とか研究者とかを調査してみる。その調査結果をお互いに交換しあい,よ く検討を加え,また,そういう機関あるいは研究者の方の希望もできるだけお聞き した上で、協力できそうな具体的研究を見いだして、研究協力をその当事者、機関 なりにお勧めして行くというようなことを考えてみたらどうだろうかということで ございます。そういうような研究題目がでてきました場合には、それをプロジェク ト研究のような形で推進するため,その当事者同士が研究計画,成果や進行状況な りを時々情報交換しながら研究を進めてゆくこととする。この場合に,研究者が相 互に短期間、すなわち1ないし3カ月くらいの短期間で、相手方の研究の場に出張 して協力の実をあげるというのは望ましいのではないか。また、コアメンバーの方 々は、そういう共同研究あるいは研究協力をしておられる方々に対して、適当なる。 助言を与えるとか、適宜支援をするというような立場をとるべきではないかという ふうに考えられます。さらにそういうものが進行してまいりましたら,それをフォ ーラムの場でご報告していただくというようなことも考えてみたらどうだろうかと いうことになってまいりました。そこで、それらのための準備もございますし、1 年毎というのはちょっと間が短すぎるという点もございましたので、次回のフォー ラムは間を1年半おきまして,1990年の春にしようかということになりました。場 所につきましては、次回はドイツでございますが、後ほどドイツの方でいろいろお 考えいただくということでございます。以上、将来の問題につきまして、現在その ような方向で動いておりますということをご報告申し上げ、皆様のご協力を得たい と思いますのでよろしくお願いします。

最後に、ドイツ側の参加者の皆様方に、今回フォーラムに友好的かつ積極的にご 参加いただき、活発で内容豊かなディスカッションをしていただきましたことを心 よりお礼申し上げます。そして、われわれの活動と友情が、今後のフォーラムに向 けても、より深められることを願うものでございます。どうもありがとうございま した。

# 4.2 ワルター・L・エングル ドイツ側議長 アーヘン工科大学教授

日独情報技術フォーラムもその5年間にわたる第1段階を経過してきました。その実施方法の形態にもある種の連続性が生み出されましたが、その形態は今後とも保たれるべきであり、また他面ではさらに拡大されるべきものでもあります。これまでの形態の中では、自分自身が講演を行うためにフォーラムに参加するわけではない参加者の輪を広げようとする試みを、既に先年、シュツットガルトで行いました。

実施した場所からして当然となりますが、そのシュツットガルトで、諸機関の若い研究者が大勢、講演やディスカッションに参加していただきましたのは、大変素晴らしいことでありました。これは評価を得たものと思いますし、またこれを恒常的な形態とするべきであると思います。

しかし、さらに重要なのは、両国の共同の研究プロジェクトの実施を試みることによって共同作業をさらに拡大しよう、また、この両面からの共同作業を進渉させるにあたっては以下に述べるような形であるべきだと決議したことであります。

まず、研究テーマの選定は、国家や企業からの要請から影響を受けること無くなされるべきであるということ。もちろん、そのような国家や企業からの援助は望ましいものではありますが、それはボトムアップ・アプローチによって、既存のプログラムに左右されることなくテーマの提供が行われるべきであります。そして、そのようなテーマを推奨プログラムとしてとりまとめる努力がなされるべきであります。また、われわれは、その作業を行うに当りBMFT(研究技術省)による支援も希望します。その際、コアメンバーは、これまで以上に義務が課されることになります。

つまり、分野の選択では指揮監修の責任があり、またその都度日本のコアメンバーと協力して、両面からの提案の比較を行い、研究所または個人によって共同で行われるプロジェクトのために作成されるリストから共通点を見つけ出す必要があります。

その場合に、比較的短期に、といいましても1カ月から3カ月ぐらいの期間になるでしょうが、交互に訪問滞在して、進行中のプロジェクトについてアクティブな情報交換を行う、ということが考えられています。そしてコアメンバーは、プロジェクトの実施にあたって全面的な支援の態勢でいる、つまり名付け親、後見人の役割を引き受けていただく事になります。

最後にこのプロジェクト研究の経過や成果については、フォーラムの場で報告が 行われます。このような共同作業から、私達は活動のさらなる強化を、そして何よ りも、若くして新鮮な血によってフォーラムがさらに活性化されることを望みます。

# 付録1 基調講演アブストラクト

「Neurocomputing」

松本元 電子技術総合研究所

「Integrated Optoelectronics for Communications」

クラウス・ワイリッヒ Siemens

# 付録 1. 基調講演アブストラクト

NEUROCOMPUTING ---

NEURONS AS MICROPROCESSORS WITH

A KIND OF MEMORY FUNCTIONS

Gen Matsumoto

Electrotechnical Laboratory Tsukuba City, Ibaraki 305 Japan

#### INTRODUCTION

Studies on neurocomputing (Amari, 1982; Rumelhart et al., 1986a) should be directed in two ways which in turn influence each other (Matsumoto, 1988): In one direction concrete neural-network solutions for specific important problems should be applied to substantiate its practical significance and, at the same time, the theoretical potentialities and limitations for computation should be explored on such network models. The alternative way is to seek a more profound understanding of the algorithms used by the CNS (central nervous system) to process information and to learn more about the molecular and cellular mechanisms underlying specific computations and memory processes in neurons and neural networks.

We will first give a brief review of current research on neurocomputing. The potentialities and limitations of neurocomputing will be discussed. We stress that these limitations primarily originate from the oversimplified model of a neuron (an artificial neuron model). We note that electrical events occurring in a natural neuron are part of the manifestations associated with neural activities and are regulated by the chemical and conformational processes inside the neuron. Neurons could correspond to LSI (large-scale integrated) microprocessors with a kind of memory function in the electronic digital-computing system. A concrete example of the neural information processing at the synaptic sites will be given for the primarily-cultured neurons of both rat hippocampus CA1 pyramidal cells and rabbit superior cervical ganglion cells. information processing performed at the synaptic sites will be discussed from the standpoint of computational science. Finally we will discuss how we should proceed in the neuroscientific study of neurons and neural networks for information science.

NEUROCOMPUTING -COMPUTATIONS PERFORMED ON ARTIFICIAL NEURON NETWORKS-

## The Artificial Neuron Model

The current models of artificial neuron networks are neurally inspired mathematical models that use a large number of simple, homogeneous but highly-interconnected processing elements, "artificial neurons". An artificial neuron collects inputs, using its internal summer after each of them is multiplied by its proper weight, and produces an output only if the

sum of the inputs exceeds an internal threshold value. We shall call the computing performed on these neural networks "neurocomputing". The operation of the current models of the neural network is basically nearest-neighbour search. The efforts of research on neurocomputing have been concentrated on searching the efficiencies of these neural networks in performing this operation (Amari, 1982; Kohonen, 1984; Rumelhart  $et\ al.$ , 1986a) and on applying concrete neural network solutions for specific problems to substantiate the practical significance (Hopfield and Tank, 1985; Sejnowski and Rosenberg, 1986).

### The Error Back-Propagation Model

Recently Hecht-Nielsen (1986a) has shown that a three or more-layer neural network system can generally represent the connection strength that will give the appropriate output for all inputs. In other words any continuous mapping from input to output can be done in a three or morelayer system. The problem now is how to implement a learning procedure for a multi (three or more)-layer system. If the input units are directly connected to the output units, it is relatively easy to find learning rules that iteratively adjust the strengths of the connections so as to progressively reduce the difference between the actual and desired output vectors (Minisky and Papert, 1969). Learning becomes more interesting and more difficult when we introduce a multi-layer network with hidden units whose actual or desired states are not specified by the task. The reason the learning becomes more difficult arises from the requirement that the learning procedure must decide under what circumstances the hidden units should be active in order to help achieve the desired input-output behavior. The reason the learning becomes more interesting is because the learning procedure itself is a means to construct a new representation. Rumelhart, Hinton and Williams (1986b) have constructed a novel algorithm which gives an effective learning procedure for the neural network with hidden units. In the three-layer system, the weights are adjusted for the output layer according to an error function that calculates a weight adjustment based on the difference between the actual and desired outputs. In other words, each error value for each actual output unit is propagated backward to the hidden layer and used to adjust the values of the weights to the hidden units. The procedure repeatedly adjusts the weights of the connections in the network so as to minimize the error function (a measure of the difference between the actual and desired output states). result of the weight adjustments, internal hidden units come to represent important features of the task domain, and the regularities in the task are captured by the interactions of these units. Practical usefulness of the learning procedure of the back-propagation model was demonstrated by Sejnowski and Rosenberg (1986). They constructed a neural network application of NETalk that did text-to-speech conversion of English. The network consists of three layers of artificial neurons; the input, the middle (or hidden) and the output layers contain 203, 80 and 26 neurons, respectively. After the learning, the network captured the text-to-speech rule and successfully operated for the new text that was different from the one used for the learning. The network has achieved 95 % accuracy. The network performance was limited to  $82\ \%$  accuracy without hidden units but was enhanced to 98 % by increasing the number of hidden units to 120. example illustrates the usefulness of the error back-propagation learning algorithm and the value of the hidden units.

However, one of the disadvantages inherent in the error back-propagation learning procedure is that it cannot generally escape from local minimum states characterized by a set of quasi-stable states in the neural network system. The other disadvantage is that the time necessary for the learning becomes tremendously longer for large size problems. According to Hinton (1987), the time of the N-interconnected network necessary for the learning process should be on the order of N $^3$  when the

operation is executed on current serial digital computers. The time is reduced by the order of N when each weight of connection is separately calculated with a parallel computer. Therefore, one solution to overcome the disadvantage is to build a computer which is architecturally suited to handle the neural network system. Because the neural network is massively parallel in nature, a computer built with several ten or hundred thousands of processors, where each processor takes the place of an artificial neuron, would improve the disadvantage. Many attempts are being made at building parallel computers for neural network systems (Hecht-Nielsen, 1986b). The other solution to overcome the difficulty of necessitating tremendously longer time in the learning for large size problems is to improve the learning algorithm of the error back-propagation model or to create a new learning algorithm to reduce the time. Most research efforts in neurocomputing are currently being devoted to the development of improved or new algorithms.

### INFORMATION PROCESSINGS IN A NEURON

A neuron is a basic element for transmitting, processing and storing information in neural systems and the brain. The CNS is not composed of neurons with the homologous characteristics as has been assumed in the aritificial neuron. Rather, the variety is one of the most prominent characteristics of the neurons. Over 50 kinds of functionally different neurons are reported in the cerebrum. This variety may be tremendously increased when the functions possessed in neurons are analyzed in more detail. The versatility is another peculiar characteristic of neurons. Indeed, dynamic molecular transformations within a neuron take place by environmental stimuli and conditions, as shown below. Both the variety and versatility are inherently associated with the neuron. As a result, a neuron could be regarded as a kind of microprocessor with multiple information-processing (synaptic) sites and with a kind of memory function.

Here we will exemplify how the information is processed and stored in a neuron for both rat hippocampus pyramidal CA1 cells and rabbit superior cervical ganglion cells.

## Rat Hippocampus Pyramidal CAl Neurons

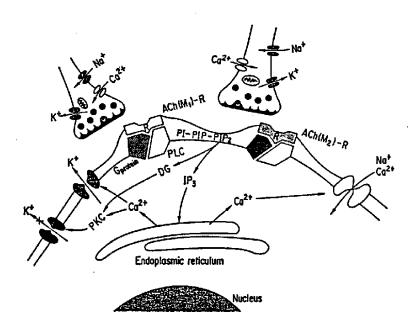

Pyramidal CAl Neurons of the rat hippocampus all contain glutamate receptive sites which respond excitatorily. Besides the glutamate receptors, some of the neurons contain muscarinic acetylcholine (ACh) receptors. In muscarinic responses, ACh usually works excitatorily (Swanson et al., 1982) but in some cases inhibitorily (Brown and Adams, 1980; Egan and North, 1986). These two opposite effects of ACh result from interactions of ACh with two different subtypes of ACh receptors (Egan and North, 1986);  $M_1$  and  $M_2$  subtypes (Fig.1). The subtype is characterized by its dissociation equilibrium with pirenzepine. The dissociation constants of the subtypes,  $M_1$  and  $M_2$ , are ~10 and ~600 nM, respectively, for slices of rat pons containing the nucleus parabrachialis (Egan and North, 1986). ACh bound to the M2 receptor causes membrane hyperpolarization as a consequence to an increase in the membrane conductance to potassium ions. The  $\text{Ca}^{2+}\text{-dependent}$  potassium channel couples to the  $\text{M}_2$  receptor. On the other hand, ACh bound to the  $M_1$  receptor brings about membrane depolarization as a result of a decrease in the potassium conductance. The potassium M channel is coupled to the  $\mathbf{M}_1$  receptor. Thus, presence of multiple receptive sites specific for a neurotransmitter augments the variety of the information processing at the synaptic site. It was recently confirmed that there were three subtypes of glutamate receptors, and that gamma aminobutyric acid (GABA) could specifically bind to two subtypes of its receptor (one with high and another with low affinity).

What kinds of molecular mechanisms regulate the switching between

Fig.1. A schematic drawing of molecular events at the synaptic sites of muscarinic acetylcholine receptors.

depolarization (the pathway from the  $\rm M_1$  receptor to the  $\rm K_M$  channel) and hyperpolarization (the pathway from the  $\rm M_2$  receptor to the  $\rm K_{Ca}$  channel) on ACh application? The pathway to the  $\rm K_{Ca}$  channel is delineated by the following molecular events which take place sequentially (Fig.1); binding of ACh to the  $\rm M_2$  receptor + release of inositol-1, 4, 5-triphosphate (IP $_3$ ), a hydrolysis product of the membrane lipid phosphatidylinositol biphosphate, into the cytoplasm from the plasma membrane + IP $_3$ -induced release of  $\rm Ca^{2+}$  from endoplasmic reticulum + opening of  $\rm Ca^{2+}$ -dependent potassium channels. In the pathway from the  $\rm M_1$  receptor to the  $\rm K_M$  channel, an enzyme termed protein kinase C (Takai et al., 1982) is involved. Protein kinase C (PKC) is in the activated state only when sufficient levels of  $\rm Ca^{2+}$  ions, phospholipid and diacylglycerol are present. Activated PKC phosphorylates and closes the  $\rm K_M$  channel, resulting in the membrane depolarization.

In cultured CA1 pyramidal neurons of the rat hippocampus, we have found that some neurons are depolarized and some are hyperpolarized when we expose them to the same concentration of ACh extracellularly (Iijima and Matsumoto, 1988). This cannot be explained by the above-mentioned difference of the ACh dissociation between the  $\rm M_1$  and  $\rm M_2$  receptors and of the fixed circuits between  $\rm M_1$  and  $\rm K_M$  or between  $\rm M_2$  and  $\rm K_{Ca}$ , since all the neurons tested are stimulated with the same amount (10  $\rm \mu M$ ) of ACh. We have concluded that there are three types of connections between the ACh receptive site and the ionic channel in the cultured CAl pyramidal neuron, resulting in three types of differentiated neurons; the first type is the M-to-K\_M type of the neuron, the second type is the M-to-K\_Ca type, and the third type is the M-to-cation selective channel type of neuron. In the last type of neuron, ACh causes the membrane depolarization by opening the (Ca  $^{2+}$ -dependent) cation-selective channel (Fig.1).

Opening and closing of the ionic channels are regulated, directly or indirectly, by intracellular  $Ca^{2+}$  ion concentration (Fig.1). Therefore,

measurement of the regional change in  $Ca^{2+}$  ion concentration within a neuron is crucial for understanding neural information processing. This can be realized for the neuron loaded with Fura-2 (a fluorescent  $Ca^{2+}$  sensitive dye developed by Tsien et al., 1985) with a SIT (siliconintensified target) camera. The cultured CAl pyramidal cell of the rat hippocampus is stimulated with ACh homogeneously for a period of time after it is loaded with 50  $\mu$ M Fura-2 (Iijima and Matsumoto, 1988).

# Rabbit Superior Cervical Ganglion Cells

Rabbit superior cervical ganglion cells all possess both nicotinic and muscarinic ACh receptors. In these cultured cells, muscarinic ACh responses are found to be dose-dependent (lijima et al., 1988). In the low concentration range (<10  $\mu\text{M}$ ), ACh interacts specifically with the M<sub>1</sub> receptor and causes Ca²+ release from endoplasmic reticulum. Calcium ions then activate the K<sub>Ca</sub> channel and cause membrane hyperpolarization (activation of the outward K current). On the other hand, in the high concentration range (>10  $\mu\text{M}$ ), ACh also interacts with the M<sub>2</sub> receptor and activates the cation selective channel, which causes membrane depolarization (or the inwardly-flowing Na/Ca current). In other words, the muscranic ACh receptors respond to ACh bimodally; first excitatorily and then inhibitorily. These suggest that the sympathetic neuron becomes inactivated for a while after the neuron is exposed to high concentrations of ACh.

In the sympathetic ganglion cells intracellular  ${\rm Ca^{2}}^{+}$  ions are again crucial in regulating the ionic channel activities. In these cells intracellular  ${\rm Ca^{2}}^{+}$  ions are released from endoplasmic reticulum on exposure to ACh. Very recently, it has been observed that the calcium releasing sites are not homogeneously distributed but localized (Iijima et al., 1988), as shown in SIT imaging of a Fura-2 loaded neuron. On the contrary, the intracellular  ${\rm Ca^{2}}^{+}$  ions homogeneously increase over the neuron on caffein application. Electron microscopic observation has indicated that the spatial distribution of rough endoplastic reticulum in a neuron is well correlated to the local sites where the  ${\rm Ca^{2}}^{+}$  ion concentration augments on exposure to ACh (Iijima et al., 1988). Calcium ions may be released from rough endoplasmic reticulum on which membrane surface  ${\rm IP_3}$  receptors are concentrated.

### INFORMATION STORAGE IN A NEURON

# Synaptic Plasticity

Synaptic information processing undergoes constant modification by the events which take place in neighbouring synapses (heterosynaptic potentiation and potentiation induced by associative inputs; associative learning) or by the events which have taken place previously in the identical synaptic site (homosynaptic potentiation; non-associative learning). How long the effect persists is synapse-dependent; it can last for several bundred milli-seconds to several months. The synaptic modulations are shown to be temporally divided into two kinds; (1) when the effect persists for relatively short periods of time (several 100 msec - several min) and (2) when it persists for long periods of time (several 10 min - several 10 months). The short-term modulation (plasticity) takes place in all synapses by a common mechanism characterized by an increase of transmitters released from the pre-synaptic side. It can be phenomenologically classified into three classes; facilitation, augmentation and potentiation. Long-term modulation, on the other hand, has been so far observed in limited cases in cells such as the hippocampal pyramidal cells (LTP; long-term potentiation), cerebellar purkinje cells (LTD; long-term depression) (Ito, 1984) and Aplysia neurons (Goelet et al., 1986).

# Long-term Modifications

What molecular mechanisms govern the translation of the effect of brief stimuli into relatively long-lasting molecular changes of high specificity? Recently it has been clarified that environmental stimuli can alter steady state levels of messenger RNA species encoding neurotransmitters by altering gene transcription, thereby altering synaptic, neuronal, and network function over time (Black et al., 1987). Thus, brief external events can elicit long-term modifications in neuronal function. Information about the external environment is stored through the very mechanism that serves neuronal intercommunication. Multiple molecular species are available in the neuron to code for environmental events over time. As a result, the basic elements for the information storage and retrieval in a neuron are proteins, RNA and DNA while those for the processing are proteins and ions. Current opinion suggests that protooncogenes in the brain may represent genetic elements mediating both shortand long-term modulations in neuronal function (Hanley, 1988). Protooncogenes are the cellular counterparts of viral transforming genes. Therefore, we can expect that the study of carinogenesis, a process related to proliferation and tumor formation, would provide insights into the functions of neurons.

### CONCLUSIONS

Neurocomputing exploits the algorithm and architecture for the information processing of neurons and neural networks to construct a computer. The basic assumption of artificial neurons on which the artificial neural networks are modelled are currently studied. We have pointed out that the assumption is oversimplified in view of the function of a real neuron. We have exemplified that the recent application of molecular and genetic approaches to the study of neural function has yielded a number of notable advances. For example, a synaptic site is a molecular processing unit that can possess a kind of memory function. The characteristics of the information processing are versatile and variable through the molecular and/or structural changes at the site. contrary to traditional views, it is now well understood that single neurons use multiple transmitter signals, that different transmitters are independently expressed and regulated in the same neuron, and that experience alters gene expression in the nervous system (Black et al., 1987).

These and related insights suggest that neurons should be regarded as LSI miroprocessors with a kind of memory function similar to a digital computing system. Therefore, studies on the neurocomputing should be ideally performed to address the problems as to what kind of characteristic processors are used in the brain and what kind of molecules and structures support the functioning. Then, it will become essential to determine quantitatively what the neural circuits are and what their associated neurobiological processes can do.

## REFERENCES

Amari, S., 1982, Competitive and cooperative aspects in dynamics of neural excitation and self-organization, in: "Competition and Cooperation in Neural Nets", S. Amari and M.A. Arbib, eds., Springer Lecture Notes in Biomath. 45: 1.

Black, I.B., Adler, J.E., Dreyfus, C.F., Friedman, W.F., LaGamma, E.F. and Roach, A.H., 1987, Science 236: 1263.

Brown, D.A. and Adams, P.R., 1980, Nature (London) 283: 673. Egan, T.M. and North, R.A., 1986, Nature (London) 319: 405.

- Goelet, P., Castellucci, V.F., Schacher, S. and Kandel, E.R., 1986, Nature (London) 322: 419.

- Hanley, M.R., 1988, Neuron 1: 175-182.

- Hecht-Nielsen, R., 1986a, UCSD Extention Class Notes.

- Hecht-Nielsen, R., 1986b, TRW Rancho Carmel Artificial Intelligence Center Technical Report.

- Hinton, G.E., 1987, Science (Tokyo) 57: 228 (Translated into Japanese by T. Ohmori and S. Amari).

- Hopfield, J.J. and Tank, D.W., 1985, Biol. Cybern. 52: 141.

- Iijima, T. and Matsumoto, G., 1988, in preparation.

- Iijima, T., Sekiguchi, T. and Matsumoto, G., 1988, in preparation.

- Ito, M., 1984, "The Cerebellum and Neural Control", Raven Press, N.Y.

- Kohonen, T., 1984, "Self-Organization and Associative Memory", Springer-Verlag, Berlin.

- Matsumoto, G., 1988, Future Generations Computer Systems (in press).

- Minsky, M.L. and Papert, S., 1969, "Perceptrons", MIT Press, Cambridge.

- Rumelhart, D., Hinton, G. and Williams, R., 1986a, "Parallel Distributed Processing: Explorations in Microstructure of Cognition, Vol. 1: Foundations", Bradford Books/MIT Press, Cambridge.

- Rumelhart, D.E., Hinton, G.E. and Williams, F.J., 1986b, Nature (London) 323: 533.

- Sejnowski, T.J. and Rosenberg, C.R., 1986, Johns Hopkins Univ. Elect. Eng. and Comp. Sci. Tech. Rep. 86: 1.

- Swanson, L.W., Teyler, T.J. and Thompson, R.F., 1982, Neurosci.Res.Prog. Bull. 26: 611.

- Takai, Y., Kishimoto, A. and Nishizuka, Y., 1982, Calcium and phospholipid turnover as transmembrane signaling for protein phosphorylation, in: "Calcium and Cell Function, Vol. 2", W.T. Cheung, ed., Academic Press, NY, p.385.

- Tsien, R.Y., Rink, T.J. and Poenie, M., 1985, Cell Calcium 6: 145.

### Integrated Optoelectronics for Communications

C. Weyrich, Siemens Research Laboratories, Munich, FRG

The striking advantages of optical fiber communications systems like low loss, large bandwidth and minimum crosstalk have made fiber-optic transmission the technology of choice for long-haul communications in recent years. Systems operating at gigabit per second data rates and featuring field lengths of more than 100 km are under development or have even been implemented in the field.

Much progress in terms of performance increase and cost reduction has been made during the last ten years. Highly sophisticated and new structures for discrete devices, especially for laser diodes, have been developed together with new packaging concepts which, because of the different material technologies involved, have to be hybride. The transmitters and receivers devices, the various optical components as lenses, filters, gratings or fiber pig-tails, and electrooptic devices like modulators or switches have to be assemmbled using micro-mechanical submounts and sophisticated engineering tools. However, the required accuracy of geometrical alignements of the different components as well as the severe reliability demands limit for the cost reduction potential.

The big challenge at present is to make fiber optics efficient and cost effective for short-haul systems e.g. for future broad band customer access connections which will be based on bidirectional transmitter-receiver-modules or multichannel coherent detection modules. Monolithic integration technologies can be regarded to be the most promising way for cost reduction and hence could be decisive for the ultimate realization of customer access systems.

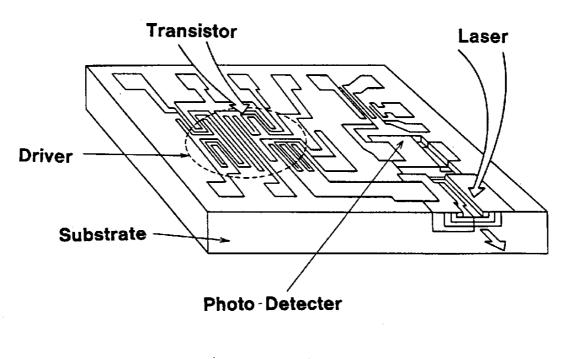

The monolithic integration e.g. of a bidirectional transmitter-receiver-module will require the integration not

only of electronic components like transistors, capacitors,

and resistors but also of optoelectronic and optical components like laser diodes, photodiodes, wave guides, filters or lenses. The integration of this much higher number

of functions - in comparison to purely electronic systems is one striking feature of integrated optoelectronic

systems.

The only materials which allow this multifunctional integration are III-V compound semiconductors like GaAlAs/GaAs or (Ga,In)(As,P)/InP which already are base materials for todays discrete heterostructure optoelectronic devices.

However, the basic technologies for the monolithic optoelectronic integration of III-V-devices are not yet sufficiently developed. Improvements of existing technologies by extensive basic reasearch is needed or even new technologies must be developed. This concerns the fields

- large diameter and low defect density semiinsulating substrates

- flexible and selective epitaxial growth methods

- ion implantation and diffusion processes

- structuring processes which have to be materialselective and which have to fulfil "optical" requirements

# and last but not least

design and simulation of processes, devices and circuits.

Today monolithically integrated substructures like laser-diode-transistor-driver, photodiode-FET, or wavelength division multiplexer have been realized. Their properties already reach those of hybridely integrated optimized devices. It can be expected that in the near future such devices will be used in larger quantities in optical fiber communication systems. The technological experience resulting from their production will help to further improvement of the respective technologies.

In conclusion, the successfull realisation of fully monolithically integrated bidirectional transceiver modules or coherent multichannel detection modules may possibly be a prerequisite for the introduction of optical fiber communication in the field of customer access. This should be a challenge for all researchers and engineers which are active in this field.

付録 2 ニューメディア分科会アブストラクト

# 付録 2. ニューメディア分科会アブストラクト

# CONCEPT OF PACKETIZED VIDEO TRANSMISSION OVER ATM NETWORKS

# Yasuhiko Yasuda Institute of Industrial Science University of Tokyo

### INTRODUCTION

Although ISDN has just been put into service in some countries including Japan, the next generation integrated services digital network called broadband ISDN has already intensively been studied in CCITT SG X V III as a leading body. The broadband ISDN is intended to provide us with truly integrated services including high quality videophone, HDTV, high speed data transmission, as well as services provided by the existing narrowband ISDN.

For this purpose a single transmission and switching mode i.e. ATM (Asynchronous Transfer Mode) is to be introduced in the broadband ISDN, different from the existing narrowband ISDN which employs both circuit and packet switching modes. In the ATM network every kind of information is decomposed into constant length blocks with header called cell and these cells are statistically multiplexed and transferred at very high speed throughout the network. Since the occurrence rate of cells is permitted to be freely controlled, the ATM network can be considered to be a rate-free network from each subscriber's viewpoint.

The above mentioned property of the ATM networks is favorable in multimedia environments where the network has to deal with information sources with a variety of bitrates ranging from a few bit per second to more than 100 M bit per second and various burstiness. On the other hand it brings about a new problem especially to the field of image coding and transmission, because image transmission techniques over constant rate networks have exclusively been studied and developed so far. This problem, packetized video, is the main subject to be discussed in this paper.

### FEATURES OF PACKETIZED VIDEO COMMUNICATIONS

The features of packetized video communications are as follows:

- (1) Improvement of coded image quality by variable rate coding: The variable rate coding can achieve higher coded image quality than the constant rate coding, when the average output bitrates are the same.

- (2) Rate-free quality control: The variable rate coding is capable of keeping coded image quality constant, while the constant rate coding is not. The coded image quality can also be controllable according to the user's requirement in the former coding scheme.

- (3) Simplification of image terminals: Simplified and lower cost terminals will be available by the variable rate coding, because it requires no large-scale memory and complicated feedback control.

- (4) Possibility of new image communications: The broadband ISDN will have the capability of multi-point communication. Using this capability, it will be easy to introduce new image communications such as a kind of multi-point video conference in which each terminal has a function of editing and composing display image.

# PROBLEMS OF PACKETIZED VIDEO COMMUNICATIONS

Since the concept of packetized video communications has just appeared on the stage, a lot of problems to be solved are left for their realization. Some of these are described below.

(1) Countermeasure against possible packet loss: In the ATM network it is considered that no link by link error and flow control will be

introduced. There may, therefore, occur such a case that some packets are lost due to transmission errors, overflow of common buffers, and excessive delay in buffers, even if their probability is very low. Since such packet loss causes seriously bad effect on highly compressed video signal, it is important to build in some countermeasures against packet loss. Some kinds of hierarchical coding schemes have been proposed for this purpose.

- (2) To make the burstiness of coded video signals clear: In order to know the performance of statistical multiplexing in the ATM network, it is needed to make clear the burstiness property of coded video signals. Some work has been done on this matter.

- (3) Rate-free quality control coding: To fully utilize the rate-free property of the ATM subscriber's channel, it is required to develop such image coding schemes that they can keep the instantaneous image quality constant and can control it to an arbitrary level. Some work has been carried out on this subject. But further study is needed, including that on evaluation criterion of image quality.

### CONCLUSION

When the broadband ISDN is realized, the major information carried by it is anticipated to be video information. In other words, if image media do not become the main traffic in it, the broadband ISDN won't be realized.

The packetized video technique has recently attracted notice in relation to the broadband ISDN. However, its application is also useful to local area networks, metropolitan area networks, and private networks constructed by employing high speed digital leased lines or satellite links.

# Switching Concepts for Broadband ISDN Bernhard Schaffer Siemens AG, Munich

### Abstract

# 1. Network evolution

In the international discussions about Broadband ISDN it is widely agreed that the target network should be based on switching and transmission principles called "Asynchronous Transfer Modes" (ATM). This technology would allow to handle all types of information uniformly in a bitrate independent network. The long-term goal for Broadband ISDN is therefore a univeral network for all telecommunication services.

But the vision of the universal network cannot be realized in the medium term furture:

- The demand for broadband dialog services is, in the short term, for business communications e.g. LAN interconnection and this would not require a universal network.

- The existing networks will be in operation for a very long time and cannot be converted easily into a universal network.

- The idea of a universal network relies more or less on the assumption of a single network operator, but this is very questionable in a deregulated environment.

- A pure ATM network would also require a pure ATM next generation switch. Such a universal switching system would be extremely costly to develope and is very difficult to justify economically.

For these reasons an introduction scenario for Broadband ISDN is more realistic which relies on enhancements and adjuncts of existing narrowband ISDN switches and networks:

- ATM technology can be used as a flexible multiplex method to offer subscribers access to existing narrowband and future broadband networks. This is for the first step a "minimum integration" concept.

- ATM switching fabrics can be used to enhance STM (synchronous transfer mode) switches to offer ATM-connections for all broadband dialog services and access to existing networks.

# 2. ATM switches and hybrid switches

A pure ATM switch has its merits in a pure ATM environment: all information is transported by means of cells and no adaption is required to STM. But the use in an existing STM environment would require adaption functions for cell assembly/disassembly and these are not only costly but also introduce delay in the network, which is a problem for instance with telephony.

Another question is how to handle distributive services like TV or HDTV:

- ATM switching for high user bitrates is quite costly and

- the merits of ATM, such as flexibility, do not play a major role for TV distribution.

It seems therefore very probable for the nearer future that ATM switching will not be utilized for this purpose.

A hybrid switch could employ ATM-switching for all broadband dialog services and STM switching for TV-distribution. For narrowband services the existing STM switches can be used but interworking with the ATM subscriber access has to be provided. A possible architecture for such a hybrid arrangement is described in the presentation.

3. Examples for STM and ATM switches STM switching for broadband channels has achieved a good technical performance. At Siemens, two lines of components were developed:

- SDM switching components in bipolar technology for  $32 \times 16$  ports are available; a device with reduced power consumption for  $32 \times 32$  ports is under development.

- TDM switching components in l $\mu$  CMOS for 128 x 128 channels each 34 Mbit/s or 32 x 32 channels each 140 Mbit/s are under test.

In the field of ATM switching we concentrate on buffered components. Three types of architectures were evaluated:

- Output buffers

- Centralized buffers

- Input buffers with output-oriented queue organization.

It was found out that a central buffer is advantageous if the cell length is long (> 36 octets) whereas the input buffer organization is preferable for short cells. In the range of 36 octets per cell both architectures show about the same data for chip area and power consumption.

A switching matrix with input for  $8 \times 8$  ports each carrying 140 Mbit/s buffers was developed which consists mainly of three ECL gate arrays. A two stage array was used to built an ATM fabric with  $32 \times 32$  ports.

### 4. Field trials

A first ATM trial with the above mentioned ATM switch is planned for the mid of 89 in the BERKOM-Project of the German Bundespost. Here an experimental fiber network is used to gain experience with applications of broadband communications.

Another milestone for the emerging brandband ISDN is the RACE program of the European Community. Here Siemens cooperates with Plessey and Italtel in a project for developing technologies for the broadband local network (BLNT):

- A subscriber loop technology is being developed using OEIC's for bidirectional transmission of 155 and 622 Mbit/s.

An ATM switch is being developed using CMOS and BICMOS for implementing a large fabric for transport bitrates of 155 Mhit/s.

Further activities are planned to create a pan-European ATM testbed for broadband services.

# 5. Conclusion

The universal ATM network cannot be achieved in a single step, evolution scenarios must be taken into account which employ hybrid approaches. The ATM network is a great challenge for system development and for technology, but promises a flexible and future proof solution for the realization of Broadband ISDN.

# ISDN IN JAPAN

### Tetsuaki EGAWA

NTT Network Systems Development Center Shinjuku 5-7-20, Shinjuku-ku, Tokyo 160, Japan

Separate public telecommunication networks have been constructed for each type of service, i.e., telex, telephone, and data services. Each network has also grown independently. Now, development of digital technologies has made the integration of these networks possible. Service integration will not only prove convenient for the telecommunications operating companies but also for subscribers who use more than one telecommunication service. A simple, low-price, global interface will soon allow subscribers to use any of several telecommunication services. With this kind of utility in mind, R&D has been carried out on the ISDN (Integrated Services Digital Network) over the last ten years.

The first stage of ISDN in Japan was between 1980 to 1985. During this preliminary ISDN stage, digital switching systems were introduced in Japan, and an INS Model System was constructed as an ISDN pilot project. INS stands for Information Network System. Japan has actively contributed information derived from this field trial to ISDN studies being carried out at CCITT. In 1984, Iseries Recommendations were partially prepared in CCITT. The second stage of ISDN in Japan was from 1986 to 1987. Main part of the ISDN Recommendations was completed in CCITT during this period. NTT developed its commercial D70 ISDN version with a user-network interface based on the CCITT Recommendations. The third stage began from 1988. In this year, ISDN commercial services were started in the main cities of Japan. Therefore, 1988 marks the first year of actual ISDN services in Japan. Some 500 subscribers in 26 cities across the

country had entered the ISDN network by the end of September 1988.

A BRI (Basic Rate Interface) of 28+D and a PRI (Primary Rate Interface) of 238+D have been recommended by TTC (Telecommunication Technology Committee) in Japan based on CCITT Recommendations. A circuit switching service of 64kb/s and a packet switching service of 64kb/s or 16kb/s are supported using BRI and PRI. High speed circuit switching services of Ho (384kb/s) and H<sub>II</sub> (1536kb/s) are provided using PRI. A 64kb/s circuit switching service, the first of NTT's commercial ISDN services, was provided through BRI starting in April 1988. Other services will be offered in Japan from the spring of 1989.

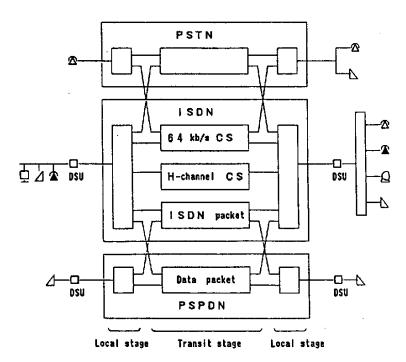

Figure 1 shows the configuration of the bearer network which NIT is planning. The ISDN is connected to the PSTN (Public Switched Telephone Network) and the PSPDN (Public Switched Packet Data Network). A system of local nodes will connect subscribers to integrated i-interface services. On the other hand, an individual transit network is planned for each service in order to improve efficiency. The transit network is, therefore, composed of a B-channel circuit-switched network, an H-channel circuit-switched network, and a packet-switched network. The routing operation is controlled by the local switching system.

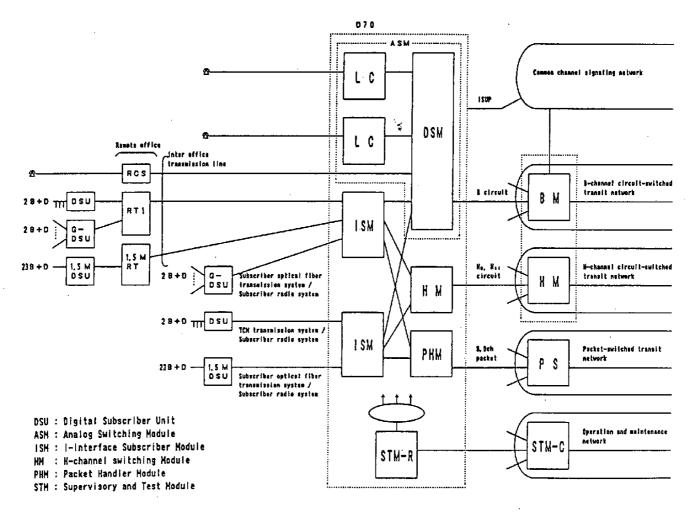

Figure 2 shows the system configuration. A Digital Subscriber Unit (DSU) is placed in the subscriber premises. A Time Compression Multiplex (TCM) digital transmission system provides BRI through existing metallic pairs, and the optical fiber transmission system provides the PRI. The D70 ISDN version system is composed of a basic Analog Switching Module (ASM) and 1-interface Subscriber Module (ISM). The newly-developed ISM performs the autonomous switching functions related to 1-interface services. Packet calls are routed to the Packet Handler Module (PHM), and H-channel calls are routed to the K-channel switching Module (HM).

ISDN supplementary services are divided into three categories: special ISDN services, enhanced existing services, and existing services. Utilizing the

signals on the D-channel, the special ISDN services and the enhanced existing services can be given a variety of new features. Take call deflection, for example, under ISDN, a terminal will be able to change the telephone number to which a call is deflected based on the telephone number of the originating call. It will be possible to deflect a call to several telephone numbers one after another. It is not possible to provide this service through POTS because its lacks the signals containing originating telephone numbers.

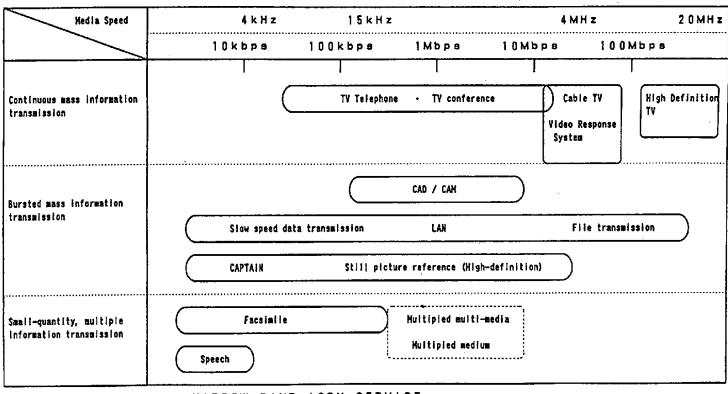

Various kind of communication services will be expected through ISDN. Table 1 shows an example of these services. Narrow-band ISDN above mentioned provides digital bearer services of from 64kb/s to primary rate. Many new digital services will also emerge along with the implementation of this narrow-band ISDN. This growth will, in turn, increase the requirement for broad-band ISDN, which will provide various kinds of services up to hundreds megabits digital information. The broad-band ISDN is currently under study and is expected to be introduced in the near future.

Fig. 1 INS NETWORK ARCHITECTURE

FIG. 2 BLOCK DIAGRAM OF ISDN SYSTEM STRUCTURE

TABLE 1 MULTI-MEDIA COMMUNICATION SERVICES IN NARROW-BAND AND BROAD-BAND

NARROW-BAND ISDN SERVICE

BROAD-BAND ISDN SERVICE

# Concept of Introduction of Broadband Communication

# Voiker Steiner Federal Ministry of Posts and Telecommunications

### Abstract

in the Federal Republic of Germany, a highly industrialized country, broadband communications will certainly play an easential future role in many economical sectors. Yet adequate planning of networks and services is very difficult because of rether unknown demand development. Therefore the concept of introduction of broadband communications of the Deutsche Bundespost is characterized by minimizing the risk of large advance network investment whilst providing the necessary means for early usage and service development.

The main elements of this concept as part of a general longerterm strategy to achieve integrated Broadband Communication Network are

- phased network evolution in applying demand- and service-flexible system concepts

- strong and broad development of services and endaystemsthrough joint user manufacturers - PTT - activities.

Important milestones in the concept implementation are the realization of the Broadband-forerunner-network (VBN), the introduction of the "Asynchronous Transfer Mode" - switching and transmission principle and low cost local area fiber systems.

The BERKOM-Project plays a major role in creating a broad range of application pilots and terminal equipments with strong inputs to standardization as a prerequisite for large scale introduction of broadband communications.

The RACE-Program of the European Community and the newly created European Telecommunications Standards Institute will contribute on an european level to spead up the process of Technology- and Systemdevelopment as well as Standardization.

An intensive dialogue with leading countries like Japan will be necessary on all fields of broadband communications to ease the national and international introduction.

# Coherent Optical Techniques for TV Distribution in Broadband Networks

### Günter Heydt

Heinrich-Hertz-Institut für Nachrichtentechnik Berlin GmbH

Broadband distribution services such as entertainment TV or HDTV for residential customers are very important for the B-ISDN. However, this fact leads to two rather different issues. On the one hand the broadband customer access has to provide for at least three TV/HDTV channels simultaneously out of a very high number of channels. Thus distribution services, which must be implemented at low costs, have a considerable influence on the complexity of the access system. On the other hand, distribution services may be a source of revenues which would allow local copper wire pair lines to be gradually replaced by optical fiber lines.

Two main technical options are currently discussed for B-ISDN implementation of TV/HDTV-distribution namely switched and unswitched broadcast.

The switched broadcast access requires only a transmission capacity which is sufficient for at least three TV/HDTV channels. The program selection is performed by a broadband switching facility in the Local Exchange which is controlled by means of signalling data sent by each TV/HDTV set and originated by the customer via his remote control device.

Unswitched broadcast systems transmit not just a few but all distributive signals simultaneously to the customers premises. The

program selection is performed by tuners located in the TV/HDTV sets. No signalling to the Local Exchange or to a Remote Unit is required.

Synchronous and Asynchronous Transfer Mode (STM, ATM) customer access systems have to employ switched broadcast whereas electrical frequency multiplex systems (Subcarrier Multiplex, SCM) and optical frequency multiplex systems (Coherent Multichannel, CMC) enable unswitched broadcast.

In the Federal Republic of Germany work on CMC systems was started in 1981 by the Heinrich-Hertz-Institute. In 1984, a first two channel system was developed and 1985 a laboratory set up of a four channel (three downstream channels and one upstream channel) customer access system was demonstrated. A ten channel TV/HDTV distribution system with nine TV channels (70 Mbit/s) and one HDTV channel (1.12 Gbit/s) was developed in 1986. This system was rather sturdily built and was demonstrated at several exhibitions such as at the German-Chinese Electronic Week 1987 in Peking.

All the aforementioned systems were operating in the optical short-wavelength region at 0.83  $\mu m$  since lasers suitable for coherent communication systems were not available for the 1.3  $\mu$  m or 1.55  $\mu m$  range.

Meanwhile, efforts to develop CMC systems for the optical longwavelength region have been started. This holds for the Heinrich-Hertz-Institute, where a ten channel TV/HDTV distribution system is under development and also for Europe, where the RACE program of the European Community aims at the Integrated Broadband Communication Network IBCN. One of the more than fifty projects of RACE is dedicated to the development of a CMC customer access system and to the development of specific components for CMC systems. Partners of this CMC project are Philips, Siemens, HHI, Plessey, LEP and IMEC. HHI is responsible for the frequency stabilization of the Multi-Carrier Transmitter Unit. A CMC demonstrator system is planned to be set up at Plessey for the year 1991.

### RECENT PROGRESS IN OPTICAL SWITCHING

# Ikutaro KOBAYASHI NTT Communication Switching Laboratories

Many promising technologies are leading to a new generation of communication networks. Among them, optical switching has the easiest development target to describe, as its purpose is clear and its functions are relatively well defined: message signal switching in the future multimedia broadband communication network.

The history of communication switching started with electrically controlled mechanical switches. It has since experienced many structural changes. For example, first wired logic control and then stored program control were introduced to make alternate paths possible when the shortest path is busy. (In mechanical age, it was only one path uniquely determined by the dialed number.) These changes also allow more flexibility in the network design. Recent progress in switching technology has replaced the sophisticated mechanical cross-bar switches with electronic time-division switches, which deal directly with the high-speed multiplexed signals without demultiplexing.

Each new requirement stimulated the structural change, and new technologies, which timely came up, supported them. Modern requirements which drive new structural change have not yet appeared in clear form, so how should we respond to requirements for a broadband multimedia network? How should we introduce random access methods or distributed-processing into the network? It takes time to analyze these questions into technical, research, or development subjects. In any case, optical techniques(switching, frequency multiplexing, signal processing, etc.) are sure to be among the new technologies which support the change.

Optical switches have many excellent features (Fig.1). They are spread widely over the range of practicality from proven immunity to electrical induction, through the potential advantages of super-wideband optical frequency domain, which has already been demonstrated experimentally(1), to the expected high switching speeds superior to electrical switches that is still under discussion(2).

High speed channels(Gigabits per second) with immunity to electrical induction have been proved by demonstrations with optical matrix switches to be effective for small high-speed/broadband switching systems(3)(4). Before commercial

Figure 1 OPTICAL SWITCHING TECHNOLOGY

use, however, the optical matrix switches have to overcome the problems of scaling up the matrix size, removal of accidental defects, suppression of variance in characteristics, and most importantly, improvement of manufacturing efficiency(Fig. 2).

Optical time-division switching is also expected to have a big advantage in direct switching of time-division-multiplexed happened in signals, similar to what electrical time-division switching systems. This type of switch experimentally(5)(4) and demonstrated also been reached the Gigahertz speed has almost switching although the number of multiplexed channels is less than ten, and the indispensable optical memory and high speed optical switch components are not mature yet. For a switching speed superior to ordinary electrical switches, the optical-driven photonic switch is promising; it requires no electrical driving circuit which limits speed.

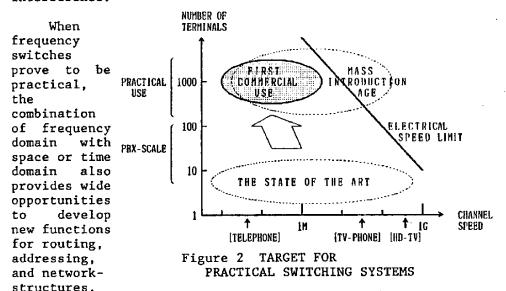

The optical frequency domain provides another dimension in addition to the space and time dimensions. Frequency-division-multiplexed signals will be efficiently switched by frequency convertors, without need for multiplexers

and demultiplexers. Switching in the frequency domain, however, implies some difficulties or complications. Some of them would be shared by electrical switches in the frequency domain, and they were the main reasons that frequency-division switching was not applied to practical systems. For optical signals, however, there are the advantages of super-wideband and immunity to many non-linear effects like higher-order harmonics interference.

Especially, a combination of time and frequency domains promises to realize multiplexing of a large number of high-speed channels.

Although optical switches open new fields in switching system design, intrinsic superiority to ordinary electrical switches is not clear. To obtain the distinctive superiority, many techniques must be proved effective, such as parallel processing, high-speed photonic correlation, optical interconnection, and optically-controlled photonic switches.

Communication switching systems started with mechanical switches. With the change of needs and technologies, the switching circuit, including its controller, has become fully electronic. Now, the switching system seems to be on a trend toward a new structure. From the view point of promoting optical technologies(Fig.3), first, the switching circuit should be replaced by optical switches for small broadband systems, and then refined for practical use a few years later. Several years after the small-scale use, second generation optical switching systems will be designed, aiming at mass-introduction and well matched with the future network

Figure 3 FUTURE TRENDS OF OPTICAL SWITCHING