## 第4回日独情報技術フォーラム 会 議 録

期 間: 昭和62年10月28日~30日

会 場: マックス・プランク研究所

シュツットガルト

昭和63年3月

社団法人 日本電子機械工業会 社団法人 日本電子工業振興協会 日 本 貿 易 振 興 会 財団法人 日本情報処理開発協会

この資料は、日本自転車振興会から競輪収益の一部である機械工業振 興資金の補助を受けて昭和62年度に実施した「日・独フォーラム」の 一環としてとりまとめたものであります。

|  | · |   |  |

|--|---|---|--|

|  |   |   |  |

|  |   |   |  |

|  |   | • |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

| 1. 日独情報技術フォーニ  | ラム趣旨                  |

|----------------|-----------------------|

| 2. 歓迎挨拶ならびに開会  | 会挨拶                   |

| 2.1 ロンメル       | シュツットガルト市長            |

| 2.2 宮 沢 泰      | 在ドイツ連邦共和国大使           |

| 2.3 ツィラー       | 研究技術省事務次官 6           |

| 2.4 W. L. エングル | ドイツ側議長 アーヘン工科大学教授 9   |

| 2.5 柳 井 久 義    | 日本側議長 芝浦工業大学学長10      |

| 2.6 U.トーマス     | 研究技術省第4局次長10          |

| 2.7 新 欣 樹      | 通商産業省機械情報産業局電子政策課長 12 |

| 3. 各分科会サマリー …  |                       |

| 3.1 ニューメディア分   | }科会15                 |

| 3.2 コンピュータ分科   | ⊁会18                  |

| 3.3 半導体分科会 …   | 24                    |

| 4. 閉会挨拶        | 33                    |

| 4.1 新 欣樹       | 通商産業省機械情報産業局電子政策課長 33 |

| 4.2 U.トーマス     | 研究技術省第4局次長33          |

| 4.3 W. L. エングル | ドイツ側議長 アーヘン工科大学教授 35  |

| (4 63)         | •                     |

| 〔付録〕           |                       |

| 5. ニューメディア分科会  | :アブストラクト37            |

| 6. コンピュータ分科会ア  | ブストラクト67              |

| 7. 半導体分科会アブスト  | ラクト105                |

| 8. 第4回 日独情報技術  | フォーラム・プログラム135        |

| 9. 参加者名簿       |                       |

| 10. 企業訪問       | 159                   |

1. 日独情報技術フォーラム趣旨

## 1. 日独情報技術フォーラム趣旨

日独情報技術フォーラムは、高い技術レベルと経済力を有するドイツ連邦共和国とわが国が、情報技術分野における両国の相互理解と交流を一層深め、活発な産業、技術協力の展開を通じて世界の情報化に寄与していくことを目的に1983年8月ドイツ連邦共和国研究技術省のリーゼン・フーバー大臣と当時の宇野通商産業大臣との間で、その設置が合意されたものである。当該フォーラムは、両国の情報技術に関わる産業分野、学術分野、および行政分野の指導的立場にある人々が一堂に会し、両国の研究開発のあり方、協力のあり方等について幅広い意見交換を行うと同時に、人的交流を深めることをねらいとしている。

当フォーラムは、毎年一回両国で交互に開かれることになっており、84年4月には第1回が東京で、85年4月には第2回がベルリンで、86年10月には第3回が東京で、それぞれ開催されている。

2. 歓迎挨拶ならびに開会挨拶

## 2. 歓迎挨拶ならびに開会挨拶

#### 2.1 ロンメル シュツットガルト市長

〔歓迎挨拶〕

私は、本日、英語で皆様に御挨拶するつもりでしたが、クワイサー博士が、"それはこの町シュツットガルトおよびマックス・プランク研究所の体面上好ましくない"と考えておりまして、私も彼の考えと同じなのです。彼は私の英語のほどを知っておりますし、私も自分の話す英語をわきまえています。私にとっては、英語を使わないですむことは皆様に不快な思いを与えずにすむことで、気が安まるところです。

当研究所の理事会で私は理事長に就任しております。私の場合,専門知識がないがゆえに,皆様方の議論に何らかの邪魔をするご心配はご無用で,会議が静かにきちんと進行することを保証いたします。ある上水道事業で水槽の中の魚がもっている役目に似ている働きを,私は担っているのであります。つまり,上水道事業では魚の助けをかりて,水が健全であるかどうかのチェックをしております。研究所の教授達は,自分達のでき具合のレベルについて,私の協力によるチェックを必要としているのです。もし私が,そのでき具合を理解したと思えば,非科学的なアプローチでその出来具合が証明されたと教授達は感じるでしょう。

第4回日独情報技術フォーラムが、当地シュツットガルトで開催されますことは私共にとって真に栄養なことであると思います。ドイツと日本の科学者達の間に緊密な協力が存続しているということを心からお慶び申し上げます。情報技術の分野で、創造性、論理的正確さ、訓練および忍耐の結合のゆえに、私共の友人である日本の皆様は、われわれにとって何か無気味な存在です。もし、皆様の日本の文字がそれほどやっかいなものでなければ、私にも皆様方がこの分野において、私共よりも数段上に位置することがわかると思います。

シュツットガルト市は、市自体で1万7千人、協力事業で8千人の職員 を擁するドイツでも比較的大きな地方自治体であります。ドイツにおいて も大きな組織になればなるほど、情報処理システムを導入している部門が

増加する傾向にあります。私共でも、もちろん多くの領域において情報処 埋システムを導入しておりますが、情報技術を含めて、多くのことが分か っていないと知られている人が先頭に立つ時、組織にとっては本質的に都 合の良い場合が多いのです。それは,あたかも何でも分かっているかのよ うに行動する人が先頭に立つよりもはるかにましなのです。しかし,何が **…正しいのでしょうか。人間というのは、正しいことよりも間違っているこ** - とが分かる能力を持っているものです。自然科学および工学は,この知識 を利用して現在に至るまで注目すべき成功を収めてきております。われわ れ政治家は、今までこの知識を十分に利用してこなかったのです。ご存知 のように、真実を求める政治家は極めて少い。なぜなら、すでに真実を発 見してしまったと考えているからです。彼らは、何が正しいのか理解せず、 また自分のプログラムに無関係なものはすべて誤りとみなす点で、常にプ ログラムどおり処理しているコンピュータに似ております。世界は情報技 術によって今後一層激しく変化するでしょう。人類が過去において成し遂 げてきたことを,コンピュータはほとんど理解できないような速さで行い - ます。今や,10億分の1秒がコンピュータにとりあたりまえの時間単位 です。10億分の1秒と1秒の比較は1秒対32年です。コンピュータは、 - このように1秒の中に、私が、公務員、および地方政治家としての全勤務 年限の間にできるのと同じ量の仕事を処理することができるのです。私は 門外漢ではありますが、今回の会議を目前にして、この学問が人類にとっ てきわめて責任のあることを自覚している学識経験豊かな研究者・技術者 である皆様によって具体的な議論が展開されようとしており,私にとって 非常に喜ばしいことであります。私はこの会議においてすばらしい進展が 成され、すべての皆様がシュツットガルトで快適な滞在をされることを望 みます。

## 2.2 宮 沢 泰 在ドイツ連邦共和国大使

〔開会挨拶〕

市長,事務次官,およびフォーラム参加の皆様! 私がシュツットガルトに来ますと,いつも私は少しふるさと日本にいるような感じになるので

す。私共日本人の仕事への取組みが、ドイツの地方住民の中ではシューヴ ァーベン地方住民が特に勤勉であると評価されているのに似ているという 関係からかも知れません。私は、第4回日独情報技術フォーラムに参加し、 開会に際して皆様に挨拶を申し上げる機会を得られたことをうれしく思 います。日独両国は、第2次世界大戦後の急速な経済復興を経験し、数十 年来再び先進工業国に数えられるようになりました。1.974年に両国は、 相互の交流とより一層の協力のための基盤を、政府、学問研究、および民 間企業のレベルで組織するという、科学技術協力についての協定に調印い たしました。両国の経済についての相互の影響に関する研究、および工業 の分野での過去数年間の私共両国の協力関係の拡大、集約化、および凝縮 化が行われてきました。具体的な例の一つは、いうまでもなくこの情報技 術のフォーラムであります。すなわち,約4年前,リーゼンプーバー連邦 研究技術大臣と当時の宇野通商産業大臣の協議で設立されたものでありま す。私共は,当初フォーラムを十分に評価できなかったというのが,私の 率直な見解であります。ドイツ連邦共和国も日本も、情報技術が先端とな ている国の一つでありますが,それゆえに新しく獲得された知識について 相互に討論することには大きな意義があり、常に新しい方向を目ざす研究 作業に大いなる影響を及ぼすものです。

皆様が、このフォーラムで議論されることは、私にとっては全く分からないことだということを私は申し上げなければなりません。私は全くの門外漢であります。しかし、もし私が日々の生活やその行動から一つの判断をなすことをおゆるし頂けるならば、情報技術の分野で実現する発展進歩はまさに、驚嘆に値するものです。もちろん開発は留るものではないし、どのようにそれは進展し、私共に将来成果として何を提供することができるのか、私共は興味をそそられているといってよいでしょう。このような理由から私は、われわれ両国の間に特別に緊密な協力関係が成立していることを歓迎したいと思います。その協力が、日独の科学者や技術者達に意見交換の機会を与えるフォーラムによって、さらに強固にされるであろうことを信じて疑いません。情報技術の領域は、例えば半導体チップの開発のような基礎研究から始められ、応用研究および商品化までの、多面的な

研究および開発作業を包括しています。それゆえ、このフォーラムには様々の専門分野の専門家 "研究計画を担当する専門家から著名な大学の研究者または民間企業の人々まで"が参加しています。われわれはこのシュットガルトでのフォーラムから貴重な成果が得られることを期待しております。

終わりに、約2週間ほど前に知らされた今年のノーベル賞受賞者に対して一言申し上げさせて下さい。ノーベル物理学賞を受賞された、ベトノルッ博士に心からお祝いを申し上げます。超電導物質についての彼の発見は、情報技術の分野でも影響を与えるにちがいありません。一方、日本人の生理学者である利根川博士が、今年ノーベル医学賞を受賞されたことについても喜びを申し上げたいと思います。しかし、このフォーラムの最も重要な参加者の一人である田中昭二博士の研究にも言及しなければなりますまい。今年のベトノルッ博士受賞の前提条件を、田中昭二博士の研究が成し遂げたのであります。私の挨拶を次のような期待をもちつつ終えたいと思います。すなわち、このフォーラムが多くの成功を遂げ、情報技術の分野での業績が持続して実り豊かであるように。ご清聴を感謝します。

#### 2.3 ツィラー 研究技術省事務次官

〔開会挨拶〕

敬愛なる大使、市長、皆様/ この日独情報技術フォーラムが、今日この地、固体研究のためのマックス・プランク研究所で開催される運びとなったことは、私にとって特別な喜びであります。また、情報技術の専門家でもない私が、この演壇に立つことに配慮をして下さり大変感謝しております。私は、この会議の準備に際して示された研究所の全職員のご支援に対して、また、この研究所のわれわれへのもてなしの素晴しさに対して、心から感謝を申し上げます。この固体研究を中心としたマックス・プランク研究所は、1969年の創立以来、内外の科学者の出会いの場所として発展してきました。日本からの客員研究者は、ご存知のように、この研究所ではよく見受けられます。そのことに対し、政府は所長に深く感謝するものであります。私は、当地シュッットガルトでこのフォーラム

が行われるような,自由な意見の交換の特別の意義について考えてみたい と思います。学問というものは,少し古風な表現を用いるならば,第一に 静かで小さな研究室での研究によって生きるものであり,第二にそれは, 固有の成果を吟味することおよび実り豊かにするために、他の研究者との 討論および意見の交換を必要不可欠なものとしております。孤立は害にな ります。なぜなら,孤立は学問の分野を複雑なまま把握することにより, 難しくするからです。情報技術を専門に扱う皆様方は,そのことをご存知 でありましょう。このように、基礎研究での国際的な協力が自明のことに なっているにもかかわらず、私共は、時々産業面での研究および開発にお ける国際的な協力を,とても難しく扱っている場合があると思います。確 かに、これは理解できる面もあります。すなわち、産業的な研究および開 発は,新しい知識によって世界市場における競争力の優位性を獲得すると いう目標をもっているからです。将来のために企業は投資するものです。 そして、この点から特別の研究成果についての秘密保持、および外国のパ トナーとの協力によって、相互の利益を最大限に増やすという期待が結 果として生まれてきます。こうした点を解決することが重要であります。 電界の両極と同様こうした利害の衝突が,国際的な分野にもあり,この衝 突は国内と同じように国境を越えようとするのです。ご承知のとおり、安 定した世界経済はオープンな経済関係に依存しております。このことは、 国際的な分業と国際間の知的伝達にも依存しているのです。閉ざされた門 戸の中では,進歩も発展もないでしょう。ドイツ連邦共和国と日本は,輸 出経済の大国,高度な技術を所有した国であり,開かれた世界市場と自由 な知的伝達に寄与するためにも、政府としては垣根を取り払い、研究者同 士また、経済上の競争者同士の対話を国家の枠を超えて促進する事が重要 だと思っています。この精神にのっとって,1974年以来,大使が既に 言及された日独政府間の協定があるのです。連邦政府もまた、この協定に そって発展してきた協力は非常に成功したと考えており,さらにこの協定 は今後の進展のための良き契機となるものと考えております。例えば,喜 ばしいことに,1988年には日本にドイッ研究所が設立されるのは間違 いないということです。しかし,この研究所は情報技術に携るのではなく, 精神科学と社会科学の非常に重要な領域の仕事を致します。有難いことに, この研究所設立にあたっては,マックス・プランク協会のご協力を頂きま した。

情報技術は研究だけでなく経済面にも関わる、難しく微妙な領域です。 それというのは、今日では純粋に科学技術的な問題だとは見なされなくな っているからです。非常に顕著な経済的な利害がからみ、かつ私共の生活 と仕事の世界に重要で決定的な影響を与えております。実際、政治のほと んどすべての分野にも入り込んでいます。この情報技術については、連邦 政府がすでに1984年3月、政府報告で、この技術の挑戦を受けるべき だという決着をまとめております。さて私は、昨晩の会話を取り上げるこ - とにしましょう。今われわれが議論しているのは,宇宙空間の研究におけ る実行と予算の諸問題です。しかし、連邦政府がそういった種類のプロジ ェクトだからという理由で、情報技術促進のための支出を、差し控えるの ではないかと心配する必要はありません。宇宙空間についての研究テーマ の分類方法が難しいために、研究技術大臣は、基礎研究、予備研究とその 他の重要な領域(情報技術もその1つなのですが)に、区分けをするよう な事になってはいけないと強調しておきたいわけです。連邦政府首相は、 その所信表明演説の中で、さらに歩をすすめた情報技術のコンセプトを公 けにしました。このコンセプトが現在のところ、検討されております。こ のコンセプトは、ドイツ連邦共和国内の状況、西暦2000年までの情報 技術の将来の発展、ドイツ連邦共和国によって準備された、より良き枠組 のための条件を創り出す基準を明らかにし、さらにドイッ人の研究とドイ ツ人の経済のために新しい刺激を与えることになるでしょう。そして、こ の関係では当然のことながら、科学技術の分野における協力の問題が、 ョ ーロッパの枠内のみならず大陸間という枠内でも重要な役割を演ずること になるでしょう。他方、私共が既に地球的な共同体の使命だと考えた様々 なテーマ,例えば,環境,癌,エイズ,原子炉の安全性,地球自身の研究, 気象,天文学,第三世界に対する農業研究等々については,世界市場でお たがいが競争している領域については困難であるとしても,このフォーラ ムの終りに将来の協力のための基準目録ができれば幸いだと思います。し

かし、もしこれが不可能としてもこのシュツットガルトでのフォーラムにおいて、一緒になってただ本音を吐くというにとどまらず、相互信頼を打ち建て、基礎的領域でもあるいは産業の領域でももっと集中的な科学技術上の協力のための関係を1つでも2つでも創り出すべく寄与できるのではないかと思います。そして、もし、これがうまく行ったら、このフォーラムに両者が参加したかいがあったというものです。それゆえ、主催者、この会議の議長、産業界とか学術分野から来ていただいた方々によろしくお願い申し上げます。こうした方々のご努力があって、ようやくただいま始まりました行事が意義あるものになると思います。どうかこの3日間、同フォーラムの参加各位は、できるだけ多くの有意義な印象を得られ、ここで得た友好関係をフォーラム終了後も両国のために継続することをお願い致します。この行事が成功裏に幕を閉じることを祈り、…私は、シュツットガルトの古い人間として、実際本日の役目柄、申し上げてよいかと思いますが…土地の守護神が、必ずや多大な力を貸して下さる事と存じます。ご清聴ありがとうございました。

## 2.4 W. L. エングル ドイツ側議長 アーヘン工科大学教授 〔開会挨拶〕

大使閣下、皆様/ 第4回日独フォーラムの開催にあたり、皆様をお迎えできたいへんうれしく思います。今回、日本とドイツ両国の科学関係において長い歴史を持つ都市でお会いできました。私たちのためにご協力を賜わったマックス・プランク研究所、とくにこの催しを企画するに当たり、たいへんご努力なさったクワイサー博士とそのスタッフの方々に感謝いたします。

世界情勢は、経済上の成功や失敗によるばかりではなく、緊迫が増しているのが特徴になってきています。このようなときに、ここに科学のアイデアを交換できる機会をつくってくださった政府に尊敬の念を払いつつ感謝いたします。

今朝、ここで皆様ご存じの田中昭二博士とクラウス・フォン・クリッツィング博士のお話しをいただけることはたいへん光栄です。

皆様方が共通の理解の下にディスカッションなさることを期待いたします。「友,遠方より来る,また楽しからずや」の言葉のように,ご一緒に楽しんでください。

ありがとうございました。

#### 2.5 柳 井 久 義 日本側議長 芝浦工業大学学長

#### 〔 開会挨拶〕

ただいまドイツ側の議長のエングル先生から日本語でごあいさつがございました。私は本当はドイツ語でやるべきかもしれませんが、昨晩、つたないドイツ語でやりましたので、本日は日本語でやらせていただきます。

ただいまエングル先生から、素晴らしいイントロダクションのお話がございました。私といたしましても同様の感じでございまして、今回、このシュツットガルトの地で第4回フォーラムを開催できたことをたいへんうれしく存じております。

このフォーラムは、いままでもそうでございましたが、今後の日独情報技術関係における友情と交流を深め合うためのものでございまして、今回のフォーラムそのものが、おそらく皆様の積極的なご参加によりまして成功裏にその実が上がるものだろうと思っております。今回の成果をさらに将来とも発展させていきたいと思いますので、皆様のご協力を深くお願い申し上げるところでございます。

簡単でございますが、開会のごあいさつに代えさせていただきます。あ りがとうございました。

## 2.6 U.トーマス 研究技術省第4局次長

#### 〔開会挨拶〕

大使様,市長様,州政府事務次官様,議長様,日本のゲストの皆様,そして本日お越しの皆様! 私共は,昨年このフォーラムのドイツ側のコアメンバーの皆様と検討した結果,今回のフォーラム開催を当地に決定しました。私共の日本からの友人の皆さんは,すぐにシュヴァーベン人は日本人によく似ていると思われることでしょう。非常に愛すべき人達ですし,

かつまた非常に危険な競争相手でもあるのです。私共連邦政府内では自ら 経験した事ですから、これについては良く存じているのです。といいます のは、州政府と連邦政府は、実際非常に手強い競争相手であります。この 美しい研究所を第4回のフォーラムに供して頂き、まことに有難く存じま す。

ここでは、将来のためにただ2つのことを申し上げたいと思います。一つは、昨日、一昨日と、通商産業省の新電子政策課長と私共とで話を致しまして、意見が一致した点があります。それは情報技術の分野で、独日の科学者の協力が、年々非常に良くなってきたという事です。また、こう言ってよければ、この分野で問題が起こっても、両国の関係官庁はいつでも、力を貸せる所では力を貸し、問題を解決する用意があるという点でも意見が一致しました。といいますのは、大学の付属機関と専門の研究機関の間のコンタクトを深めるのが私共の目標だからですし、これができるのは、定期的に会い、若い人達にもその都度色々な州に来てそこで一緒に仕事ができ、新しい事に触れ、友情を結び、それが将来も続く、といったことからです。そういう訳で、できるだけこれらの出会いの場があればと思っています。

第二は、このフォーラムは3年前に、リーゼンフーバー大臣と宇野大臣によって決定されたものですが、両国の産業分野、技術分野からの著名な代表者同士の非公式の出会いの場であるという意義があります。この与えられた機会の真価をよく理解される事を切に願う次第です。そして、両国のためにつまり科学者・技術者同士の出会いとまた産業分野・学術分野の代表者同士の出会いのために、私共は自ら音頭をとらせていただきます。私共は場所を提供すると同時に、皆様方に様々な可能性を提供したいと思っていますが、これを生かすのは皆様方にかかっています。この意味で、私自身がこのフォーラムの将来のためにも様々な準備をしなければならないと思います。ありがとうございました。

#### 2.7 新 欣 樹 通商産業省機械情報産業局電子政策課長

〔 開会挨拶 〕

市長閣下,大使閣下,次官そしてご列席の皆様/ 本日,ここに第4回日独フォーラムが開催されるに当たりまして,通商産業省を代表いたしまして,一言ごあいさつ申し上げます。

まず、エングル先生、柳井先生の両議長をはじめ西ドイツ研究技術省、GMD、また日本側のJETRO、JIPDEC、さらには開催地でございますバーデンビュルテンベルク州シュツットガルト市、マックス・プランク研究所等の各位が、当フォーラムの開催に向け寄せられましたご努力に対し、深甚なる敬意を表するしだいであります。

日独情報技術フォーラムは、高い技術レベルと経済力を有するドイツ連邦共和国とわが国が、情報技術分野における両国の相互理解と交流を一層深め、活発な産業技術協力の展開を通じて世界の情報化に寄与していくことを目的に、1983年に研究技術省と当省との間の合意に基づき設置されたものであります。

以来,両国の情報技術にかかわる産業分野,学術分野および行政分野の 指導的立場にある人々が年1回,一堂に会し,幅広い意見交換を行うとと 。もに,人的交流が深められてまいりました。

今回はHDTV,ソフトウェアエンジニアリング,超電導などといった ニューメディア,コンピュータ,半導体の各分野におけるホットなテーマ に関し,両国の第一線の研究者から研究成果の発表が予定されております。 日独両国に,世界の繁栄に対する創造的な貢献がいままで以上に期待 されている今日,創造的科学技術の分野で世界に冠たるマックス・プラン ク研究所においてこのようなフォーラムを開催できることは,まことに時 と所を得たものと考えるしだいであります。

1週間ほど前に起こった株価の大暴落は、世界を震憾させましたけれども、 同時に世界の経済活動がいかに密接に関連し合っているかということを改め て思い起こさせました。

情報技術の目覚ましい発展を背景に、現在、地球的な規模で情報化が着実に進みつつあります。また、情報化は国境を超えた情報の流通を促し、

各国経済社会の国際化にも重要な役割を果たすものと期待されております。 そのようななかにあって、日独両国が情報技術分野における交流を通じ、 世界の情報化、ひいては世界経済の活性化に貢献できることを期待してや みません。

最後に、本フォーラムが、皆様方の活発な意見交換を通じて成功裏に進められますこと、および本フォーラムが今後とも一層発展いたしますことを祈念いたしまして、私のごあいさつとさせていただきます。ありがとうございました。

# 3. 各分科会サマリー

|  | <br> |   | _ |  |   |

|--|------|---|---|--|---|

|  |      |   |   |  |   |

|  |      | • |   |  |   |

|  |      |   |   |  |   |

|  |      |   |   |  |   |

|  |      |   |   |  |   |

|  |      |   |   |  | İ |

|  |      |   |   |  |   |

|  |      |   |   |  |   |

|  |      |   |   |  | ļ |

|  |      |   |   |  |   |

|  |      |   |   |  |   |

|  |      |   |   |  |   |

|  |      |   |   |  |   |

|  |      |   |   |  |   |

|  |      |   | · |  |   |

|  |      |   |   |  |   |

|  |      |   |   |  |   |

|  |      |   |   |  |   |

|  |      |   |   |  |   |

|  |      |   |   |  |   |

|  |      |   |   |  |   |

|  |      |   |   |  |   |

|  |      |   |   |  |   |

|  |      |   |   |  |   |

#### 3. 各分科会サマリー・

#### 3.1 ニューメディア分科会

〔ニューメディア分科会ドイツ側主査 C. Baack 〕

お早うございます。ニューメディア分科会で話し合った内容のサマリー を発表したいと思います。

ニューメディア分科会は、2日間にわたり高品位テレビ(HDTV)についての様々な問題について話し合いました。HDTVは、視聴者に、できるだけ本物に近い自然な映像を提供することを目的としています。日本では、HDTV技術は20年前から研究されてきました。ドイツのHDTV研究は、研究技術省の奨励下で70年代後半に始まりました。

日本以外では、HDTVの研究活動は、そのほとんどがドイッで実施されていると言わなければなりません。将来家庭で利用されるHDTVディスプレイがHDTVの主要機器であるため、最初のセッションではHDTVディスプレイ技術、フラットパネル、プロジェクション型デスプレイに焦点をあて、関連テーマについて話し合いました。

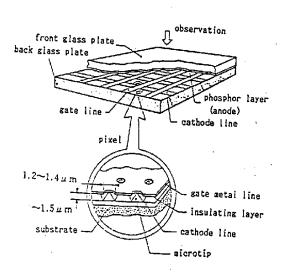

シュツットガルト大学の Liider 教授が、薄膜トランシスタを採用したアクティブ・マトリックス技術の研究結果を発表しました。彼は、シュツットガルトで考案されたセレン化カドミウムプロセスに利用されている TFT技術について詳しく説明しました。

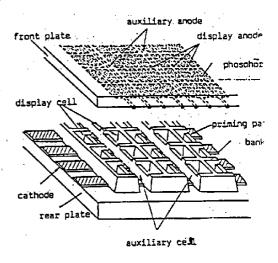

NHKの平島氏が現在最高のフラットパネル技術の研究および比較結果を発表しました。NHKのプラズマ・ディスプレイ・パネルと、20インチ・ディスプレイの最近の成果が報告されました。

ヘキスト社(フランクフルト)のFelcht博士も、強誘電体LTDに重点 を置きながら、液晶材料の諸問題について発表しました。

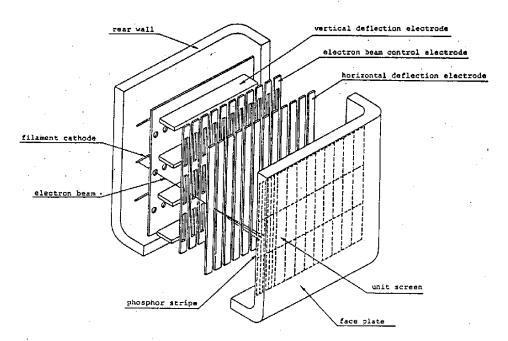

松下電器の野々村氏は、フラット・カソードレイチューブ・パネルに対する様々な既知のアプローチに関する研究結果を紹介しました。松下電器が開発した自給構造を持つマトリックス駆動フラットCRTが詳しく説明されました。

最後に、HHIのGerhard Multhaupt 博士が、ソリットステートのライ

トバルブについて詳しい紹介しながら、ハイライト出力大型スクリーン・ プロジェクションを行うためのライトバルブ・アプローチの研究内容を発 表しました。

総合的に、CRTとソリッドステートのライトバルブのプロジェクションが、将来2メートルのデスプレイを実現するためのコンパクト・プロジェクターとして有力候補であると考えられることが明らかになりました。ずっと先の将来には、プラズマ・ディスプレイとフラットCRTが、大型HDTVディスプレイのための最有力候補と考えられます。

ニューメディア分科会の第二セッションでは、HDTVスタジオと消費者の間に必要となるトランスミッション・リンクについて論じられました。NTTの三木氏が、現在日本で開発中のHDTV帯域圧縮コーディング技術と広域通信システム技術について紹介しました。帯域圧縮コーディングとして、彼は、2種類のアナログ・フォーマット・コーディング・スキームと、ビット速度が140メガビット/秒以下のデジタル・コーディングを紹介しました。

広域通信システムについては、ファイバーオプティック技術を使ったコスト効果の高いローカル・ディストリビューション・ネットワーク・アーキテクチャの重要性が強調されました。光周波数分割マルチプレックス・リンクへの好調な傾向が有力であることも紹介されました。ドイツ郵政省の研究所のStenger博士は、より一般的なHDTV通信の問題について話されました。

例えば、衛星、CATV、広域ISDNおよびユニバーサル広域ネットワークなどの通信メディアについて紹介しました。また、VIWES、高解像度MAC、デジタル広域通信フォーマットなどの通信フォーマットについても説明されました。さらに、互換性、非互換性に関する今後の戦略についても説明しました。近い将来のHDTV通信の可能性については、ヨーロッパでは衛星通信ですが、ベルリンのHHIが行っているコヒーレント光通信システムの優れた研究から、大いに有望視されています。

全般的に,このような長期展望の分野では,日本とドイツの見解は非常 に似ていると思われます。これは,将来の対話と協力関係にとって非常に 望ましい基盤となります。

ニューメディア・グループの第三セッションでは、HDTVレコーダーやHDTVカメラなどのスタジオ設備が話し合われました。ソニーの橋本氏が、ソニーのデジタルHDTVレコーダーについて、設計上の重要な問題やこれまでに達成された成果をまじえながら、詳しく説明しました。テープ・ヘッド・コンタクトとイコライジング・シミュレーションが紹介されました。Broadcast Television SystemsのHausdörter博士が、ピックアップ・チューブとソリッドステート・イメージャーの長所、短所を考察しました。現在のソリッドステート・イメージャーは、低感度という欠点がありますが、ノイズ比の向上を導きます。これは、将来のHDTVのアプリケーションにとって好都合であると思われます。

会議では、値段はチューブとは比べられないだろうというコメントが出 されました。

池上通信機の堀氏が、30 mmの planned ikonを採用した池上通信機の新しいHDTVカメラのコンセプトについて説明しました。従来の satikonを使ったカメラとの性能比較を行い、周期ノイズ比は高いが、lack が低いことを発表しました。このカメラは非常にコンパクトで、間もなく市場に出ると思われます。

さて、高品位テレビは、本当の情景を自然な映像として映す試みへの非常に重要な一歩です。しかし、自然に近い映像を映すという試みの最終段階は、当然、三次元テレビでなければなりません。ですから、私たちのシンポジウムの最後のセッションでは、三次元テレビについての討論が行われました。

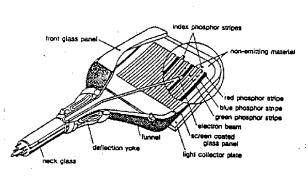

東京大学の浜崎教授が、レンズ・プレートと特殊なビーム・インデックスCRTを組み合わせて作った自動立体三次元画像を紹介しました。利用された方法と、インデックス回路構造が詳しく説明されました。ここでは、デスプレイ面積22センチ×28センチが紹介されました。

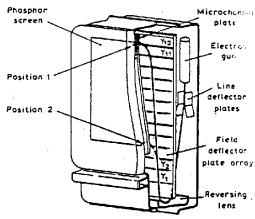

HHIの Börner 氏が、レンズ状のスクリーンを使った大型デスプレイの 三次元テレビについて説明しました。対角線の長さ2.5メートルの三次元 画面は、眼鏡を使わなくても見ることができます。この原理が詳しく説明 された後で、スクリーンの設計について討論が行われました。また、6台のTVカメラと6つのCRTプロジェクター装置の説明も行われました。 紹介された2つの方法は、アプリケーション分野が全く異なることが、討論で指摘されました。娯楽用として、大型画面が必要とされていると考えられました。

以上, 4つのセッションで詳しく討議されましたテーマをまとめて報告 しました。最後に,各講演は素晴らしく,非常に優れた研究結果が紹介さ れ,実り多く率直な討論が行われたということを申し上げたいと思います。 どうもありがとうございました。

#### 3.2 コンピュータ分科会

〔コンピュータ分科会ドイツ側主査 G. Goos〕

コンピュータ分科会からご報告します。後半は相磯教授から報告していただきます。

コンピュータ分科会には、日本から9人、ドイッから13人の計22人が出席しました。日独の大学から2件、公的研究機関から5件、産業界から7件の計14の論文発表が行われました。

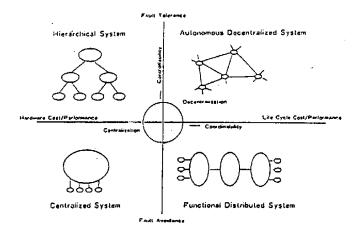

3つのセッションでは、「フォールトレランス・システム」「ソフトウェア・エンジニアリングの方法論」および「ソフトウェア・エンジニアリング環境」のテーマが取り上げられました。これらのテーマは、日独が何回かのやりとりの上で合意したものです。まとめますと、フォールトレランス・システムの発表では、研究開発段階から実際のアプリケーションまでの推移が詳しく説明されました。

このセッションは、生物システムに類似するアプローチを紹介した井原 氏の講演が目を引きました。ソフトウェア・エンジニアリングの方法論と環 境についてのセッションでは、産業界と学術界の両方の視点でこれらのテ ーマが論じられました。実用化が間近のものもありましたが、これから 10年間に解決しなければならない問題も多く残されていると思われます。 ここで、ドイツ側の論文発表について報告します。日本側の分について は、相機教授から紹介されます。 フォールトレランス・システムのセッションでは、Braunschweig 大学の Leilich 教授によるデータベース・マシーンと宇宙実験のハードウェアの紹 介から始まり、全般的には、特殊ハードウェアは、汎用システムと競合で きないことが多いということが指摘されました。特殊ハードウェアは、余 りにも特殊すぎてフレキシビリティに欠け、値段が高く複雑すぎるという 欠点があります。技術進歩が急激で、次世代の汎用システムが余りにも早 く出現してしまうので、経済的に生き残れる製品を開発する時間的余裕が ありません。

Leilich 教授は、コンポーネントやシステム・レベルでのフォールトレランスの要件について説明しました。これは、彼のグループが、衛星や惑星間ロケットに組み込まれた計算装置の設計時の実際に満たした要件です。非常に厳しい要件ですが、決して適合不可能なものではなく、基本的にはハードウェア・アプローチです。この点については、ソフトウェアの問題はそれほど重要ではありません。

Krupp Atlas Elektronik の Meyerhoff 博士は、デュブリケート・マルチプロセッサ・システムに基づくフォールトレランス・プロセス制御システムを紹介しました。この2つのシステムは、完全に同期化して並行に作動します。使用中のシステムに故障が発見されると、ただちにスタンバイ・システムが代わって作動します。同期化機能と比較機能は、マイクロ・コード化された命令によって実行されます。このシステムは、オペレーショナル・システムで、多くの装置で完全なトレランスを持つことが試験で立証されています。

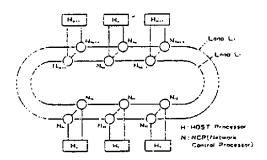

第一セッションの最後は、GMDベルリンのBehr 博士の発表が行われました。オープン従属型分散型コンピュータ・システムのアーキテクチャについて、欧州の研究プロジェクトDELTA4を紹介しました。このプロジェクトの目的は、日立の井原氏が発表した自動分散型システムと非常によく似ています。最大の違いは、欧州が異質のホストを持つオープン環境に向かっているのに対し、日本は、閉鎖型コミュニケーション・システムをもつ同質ステーションを目標に開発しています。

DELTA4システムは,複製ソフトウェア・コンポーネント間でメッ

セージの伝送を行う信頼性の高い通信システムを基礎にして、さらに開発 が進められています。この通信システムは完全な分散型です。ソフトウェ ア環境のアプリケーションは、オブジェクト指向の機構に基づいています。

ソフトウェア・エンジニアリングの方法論に関するセッションでは、ドイツ側が2人、日本側が2人の論文発表が行われ、アプローチごとに2つ に分けて発表しました。

SiemensのHowein氏が、産業用オートメーション・ソフトウェア専用のソフトウェア・ファクトリーへのアプローチについて発表し、方法、ツール、組織が成功を導く3つの鍵であると述べました。また、強力なワークステーション・ネットワークの上に築かれたワークベンチ、要件分析を設計するための総合的ツール、グラフィック・ユーザー・インタフェースに基づくユーザー・フレンドリ性、基準および品質保証の尺度を、より方法論的な観点から考察しました。井原氏は、新たな開発では年間8%、コンポーネントの再利用では16%も生産性が伸びたと述べました。これは、非常に驚異的な成果であり、これまで、このような高い数字を達成した例はほとんどありません。ですから、これは非常に興味深い発表であると同時に、あとでかなりの論議も呼びました。最後の発表者のHowein氏から、今後は、情報をベースにしたツールから発展が見られるであろうという予測が述べられました。

カールスルーエのFraunhofer Gesellshaft の Steusloff 教授は、ソフトウェア・エンジニアリングのための集積ツール・セットへの総合的なアプローチに関する講演を行い、ツール集積化の一般的な問題について論じ、ユーザー・インタフェース、ツール、データ操作およびデータベース間のインターフェースを標準化することの重要性を強調しました。BMFTが後援するユニバーサル・プロジェクトについて説明しました。

全体を要約すると、ソフトウェア・エンジニアリングの問題を解決する ための、ユニークかつ明快で一般に認められる総合的方法論が生まれる兆 しはみえていません。現実的には、これから実現される理想のものではな く、現在すでに利用できるものを使わなければなりません。これによって、 ある程度の生産性の向上はもたらされましたが、問題の最終解決はまだ先 です。しかしながら、ほとんどの参加者は、1990年代にはいくつかの新しい方法論が導入され、最終的に、ソフトウェア構築のための非常に有用な数学的アプローチとして結実するであろうという松本氏の意見に同意しました。このようなアプローチについては、多くの重要な点について、まだ基礎研究すら行われていません。また、実際に利用した段階で、さらに深刻な教育的問題が提起されると思われます。

ソフトウェア環境に関する最終セッションは、Hruschka 博士の論文で始まりました。博士は、コンピュータを利用した総合ツール・システムについて発表しましたが、これは、所属しているGEIの社内要件から導いたもので、基本的にはリアルタイム・アプリケーション向けのものです。フレームワークの側面も広く利用されて、他の外部のツールに対するオープン・インタフェースも利用できます。各国では、市場に出ている製品を利用することができます。

カールスルーエの情報研究センターの Dittrich 博士は、ボトム・アップ・アプローチとして、集積ツール・セットのニーズを満たし、ユーザが必要とする効率を満足する目的指向型データベース・システムについて発表しました。これは、現在建設中であり、実用性についての試験が行われています。

このセッションの最後に、ミュンヘンの Soft lab 社の Abbenhardt 氏が発表しました。彼は、産業化されたアプローチに近いソフトウェア開発プロセスを生み出す遠大なコンセプトであるとして、欧州の Eureka Project を紹介しました。現在は目標と戦略を定義するための定義段階で、あまり詳細には進んでいません。

総合的に、ツールのブラックボックス・インテグレーションとオープン 総合ツール・セットに関するフレームワーク・アプローチは、現時点では、 特殊な性質と利点があるという結論に達しました。ブラックボックス・シ ステムは製品として入手できますが、特定の環境だけに限定されています。 オープン・システムは、今でも、多くの問題を抱えていますが、ユーザの ニーズに合わせた特殊なシステムを作る機会があれば、より一層利用機会 が増えるでしょう。ソフトウェア・ファクトリーのアプローチは、将来的 には、オープン・インテグレーテッド・ツール・セットの能力を強化する ことになるでしょう。これで、私の担当するサマリーの発表を終わります。 相磯教授お願いします。

#### 〔コンピュータ分科会日本側主査 相磯秀夫〕

皆様お早うございます。日本側のコンピュータ分科会による発表をまとめたいと思います。フォールトレランス・システムと題した第一セッションでは、東京工業大学教授であり、日本のフォールトレランス・コンピューティングに関する研究グループの会長をつとめる当麻教授が、最近、大学や研究所を中心に進められているフォールトレランス・コンピューティングについてのいくつかの研究テーマを紹介しました。

セルフチェック回路,テスト可能な設計,人工知能,または論理的言語 PROLOGを使ったテスト生成プログラムへの知識アプローチ,マショリティ・ボードなどのフェイル・ソフト・システムの理論を紹介しました。ソフトウェア・エンジニアリングに関係するフォールトレランス・コンピューティングや,フォールトレランス・システムの実用化や産業開発については、発表時間が短かったためにあまり詳しく触れませんでした。

日立の井原氏は、フォールトレランス計算技術を大規模なリアルタイム・システムに応用したケース・スタディについて発表しました。このシステムは、多くの例で、フォールトレランスの拡張性と保全性が要求されます。システムが上記の条件を満たせるように、生物的アナロジーに基づく自動分散型制御システムに対する新しい設計コンセプトが提案されました。

その他にも、このようなフォールトレランスの自動分散型システムを実現する上で重要な技術的問題についても発表しました。設計コンセプトの効果が正しいことを立証するために、ファクトリー・オートメーションの制御や鉄鋼生産工程制御システムへのアプリケーション・システムの可能性についても説明しました。

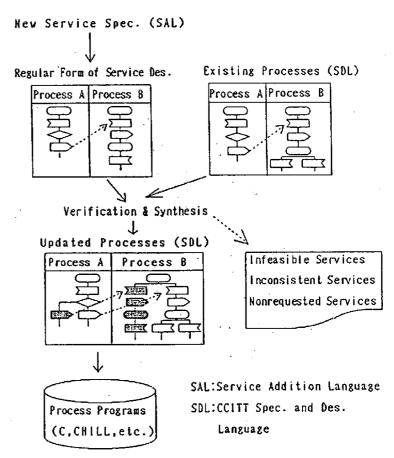

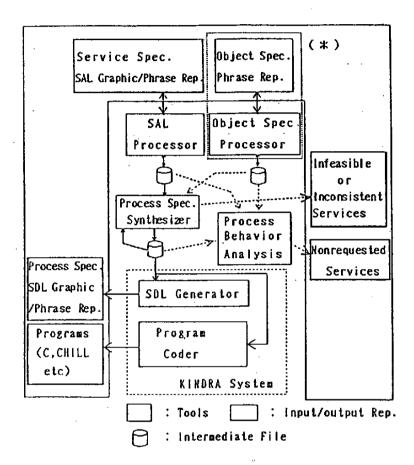

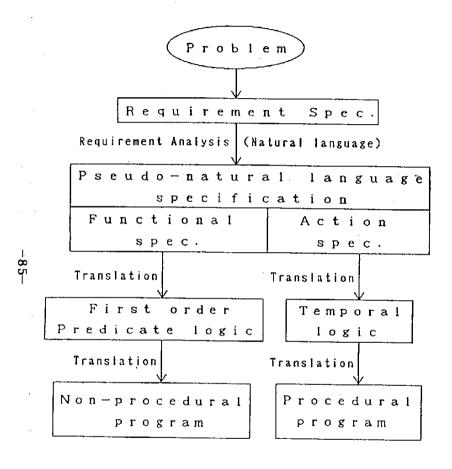

ソフトウェアの方法論と題した第二セッションでは, NTTの花田氏が, ソフトウェア生産自動化の研究についてその概要を紹介しました。彼は, この研究を「定理の証明」「事例からの合成」「高水準記述からの合成」 および「プログラム要素の再利用」の4種類に分類しています。また,2 種類の合成方法を例にとって説明しました。ひとつは,自然言語に基づく ソフトウェア開発システムで,もうひとつは,システム記述環境です。後 者は,サービス要求の高まりに対処するために通信ソフトウェアを効果的 に実行するための環境です。

ソフトウェア需要の拡張,低いソフトウェア生産性および専門のソフトウェア・エンジニア不足などが原因で,現在の情報技術のあらゆる層で発生しているようにみえる重大なソフトウェア危機を回避するために,日本電気の松本氏は,ビジュアライゼーションの自動化とソフトウェアを利用することを提案しました。このコンセプトの一例として,日本電気で開発され,様々な場所で利用されているソフトウェア・エンジニアリング・アーキテクチャを説明しました。このシステムの最大の特徴は,設計と生産の質の向上,プログラムの読みやすさ,高品質プログラムのテストと設置の生産性の向上を保証することです。

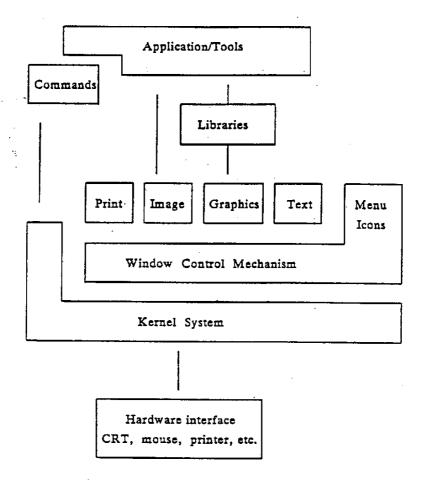

ソフトウェア・エンジニアリング環境と題した第三セッションでは,情報処理振興事業協会のシグマ・プロジェクトの秋間氏が,世界的に注目されているシグマ・プロジェクトについて紹介しました。これは,通商産業省から研究奨励金が出ているソフトウェア開発技術の推進プロジェクトです。彼は,このプロジェクトの背景,目的,特徴,シグマ・システムのフレームワーク,システム構成,データベースとネットワーク・サービスおよびシグマ・ワークステーションとオペレーティング・システムのプロトタイプおよび将来の展望について詳しく説明しました。

シグマ・ワークステーションの重要な特徴のひとつとして、第三セッションではマルチメディア・ウィンド・システムを詳しく説明しました。彼は、機能要件の設計ポリシー、ハードウェア要件、マルチメディア・ウィンドウとプリンタなどの設備、ソフトウェア製造プロセスについて紹介しました。このプロジェクトは、ソフトウェアの生産性が向上し、ソフトウェアの信頼性と質を高めることが予想されるため、国際的に広く注目されています。

最後に、コンピュータ分科会のセッションについて総合的なコメントを

述べたいと思います。このフォーラムは非常に有意義で、両国の優れた研究者との意見交換を楽しみました。このフォーラムは将来も討論を続け、協力しあう価値があると思っています。しかしながら、もう少し発表件数を減らすべきだったと考えています。最近の技術的テーマを話し合うには発表件数が多すぎて、限られた時間が無駄に使われてしまいました。これは、前回のフォーラムでも指摘されたことですが、まだ改善されていません。ですから、日本で開かれる次回のフォーラムでは、構成内容を変えることを提案したいと思います。

実用的なフォールトレランス・コンピューティング・ジステムに関する ドイツ側からの発表については、日本よりずっと多くのシステムの研究が 進められているという感想を持ちました。また、ソフトウェア・エンジニ アリング環境の開発に関する実際の研究方法に、非常に強い感銘を受けま した。これは、製品の効果を立証できたと考えています。

これで発表を終わります。どうもありがとうございました。

# 3.3 半導体分科会

共同主査の田中昭二教授に代わりまして、半導体に関する討議結果を発 発します。非常に素晴らしい会議であり、特に、構成が適切であったと思 います。また、発表原稿数も適切であり、コンピュータ分科会のように時 間の配分を気にする必要もあまりなく、次々と発表が進みました。

A STATE OF THE STA

. .

半導体は、当然のことながら、優れた材料であり、この材料を支配する ものは情報技術を支配します。ですから、半導体の討議には所有権が主張 される問題が多く含まれていますが、このような微妙な分野にはふれずに 進めました。私たちは、競争が行われる前の分野、特に、材料指向型の研 究開発と、その分析、製造方法についての見解や研究結果の交換を中心に 討論を進めました。

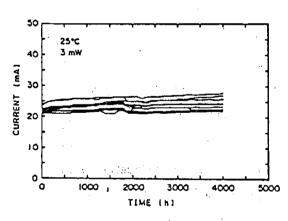

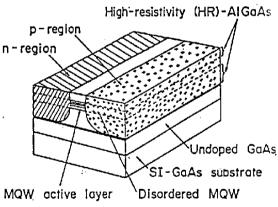

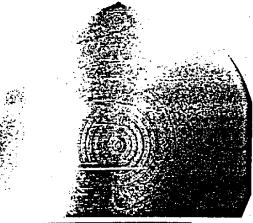

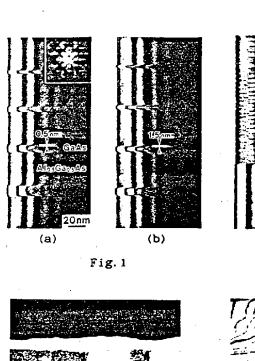

しかしながら,種々の分野における将来のデバイス製造の見通しは非常 に明るいと感じました。例えば,桜井氏は、オプトエレクトロニクス集積 回路トランスミッターのスライドを見せてくれました。このスライドは,近い将来に登場するものを暗示しています。彼の講演では,この回路の心臓部となるアルミニウム砒素,ガリウム砒素のレーザー・エミッターが主テーマとして取り上げられました。また,これに関与する開発,材料および加工技術を紹介しました。

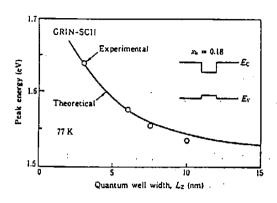

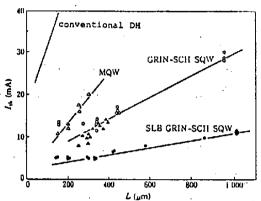

アカデミックな側面からの見解として、Pilkuhn 教授が、 von Klitzing 教授がオープニング・セッションで述べた内容の延長どもいえる非常に素晴らしい発表を行いました。これは、バンド構造エンシニアリングの総合的な概念で、特定の光放出装置、レーザーなどにとって望ましく、必要な電導性や不連続な価電子帯を作るためのものです。素晴らしい発達を遂げている非常に有名なガリウム砒素、アルミニウム・ガリウム砒素系についても素晴らしい発表を行いました。さらに、非常に多くの種類の材料についても紹介し、シュツットガルトの大学やマックス・プランク研究所が、これらの半導体化合物について分業体制で共同開発している内容についても発表しました。

もちろん,近代の半導体業界とマイクロエレクトロニクスの牽引車であったシリコンについての発表も行われ詳しく論じられました。特に,非常に難しいように見えますが,コンピュータ・サイエンス,コンピュータ・ハードウェア,電気通信に大きなインパクトを与えると思われる新しい開発成果についても紹介されました。

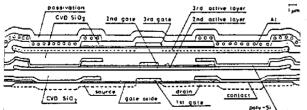

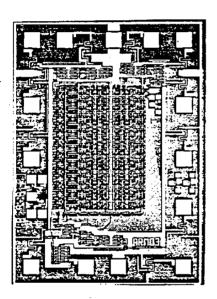

赤坂氏の講演では、半導体分野の人々にとって非常に興味深いシリコン結晶の内部にデバイスを三次元に配置したものが紹介されました。まず、シリコン基板にデバイスの層を乗せ、その上に多結晶性シリコンを重ねます。この多結晶性シリコンを再結晶すると、材料の物理的特性が発揮され、結晶の方向性が非常に重要な役割を果たします。彼は、例えばラマン・スペクトロスコピーを使って、各々の基礎研究がどのような関連性を持っているかの優れた例を紹介しました。このラマン・スペクトロスコピーは、10年前までは完全に理論的な手法でしたが、今や、非破壊的に迅速に調べられる優れた方法として利用されています。皆様も、赤坂氏と彼のグループが、この三次元デバイスの開発に、大成功をおさめたことがおわかり

になったとおもいます。

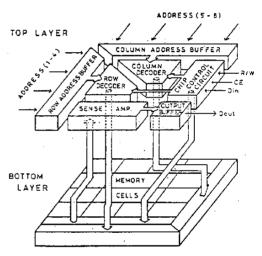

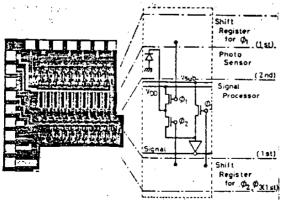

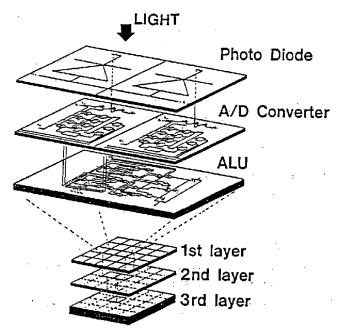

もうひとつ,リアルタイムのイメージ変換と光学データ処理に非常にコ ンパクトで高速かつ内部結合した (inter-connected) デバイスの原理を応 用するという発表も注目されました。これも非常に素晴らしい講演であり、 材料とそのプロセスを理解することがいかに重要かということを再度認識 させられました。この場では、討議の概略だけで、内容にまで詳しく立ち - 入るつもりはありませんが,各レベルがいかに複雑であるかはご理解いた だけたと思います。材料は、この建物のように、全く異なる活動を持った フロアから作られた非常に複雑な建物のようなものです。ここには、光ダ イオードを持つ個々のパーツから始まり、信号処理が進んで三次元に移行 します。これは、非常に素晴らしいことです。このように私たちは非常に 有意義な話し合いを行いました。また、ミュンヘンのFraunhoufer Society - で始まったプログラムもあったので,意見の交換も活発に行われ,非常に 素晴らしい人間的な接触もありました。この研究所で様々なアプローチを 試みています。 Bauser 夫人は,低温での研究を行っています。 これは,液 晶エピタキシーを作るので、美しく完璧なシリコン結晶が酸化物の上に乗 っています。このように個人的な接触、アイデアの交換は非常に素晴らし いものでした。

この他の材料も取り上げられました。ドイッは、化学の分野で優れた伝統がありますが、リソグラフィーとそれに必要な材料についての非常に優れた発表でもこのことが立派に証明されました。発表件数を多くしなかったので、討論の時間が十分取れたと思います。もちろん、発表原稿を選択しなければなりませんでしたが、適切なものを選べたと思います。

最後の発表は、リソグラフ技術としてのイメージの反転(image reversal)で、特殊な光吸収の性質を持たせた誘電分子(die molecule)をこのレジストに使うという、Buhr 博士と Hoechst-Kalle の同僚研究グループによるものです。ドイツ国内はもちろんのこと、アメリカ、日本などの世界各国と密接に協力しながら行っています。専門家たちも、非常に優れた開発成果であり、写真露出、電子線露出および、X線レジストを使って美しく明解な構造ができることを認めています。このテーマは非常に詳しく論じられ、

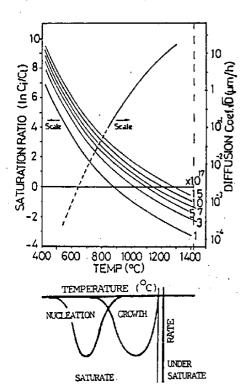

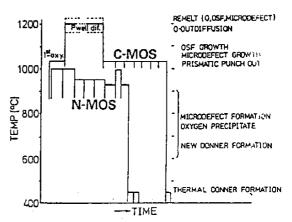

複雑なトポグラフィーにきれいな線がかけるという大きな利点があります。 これは、ダイナミックRAMだけでなくあらゆる世代のシリコン技術への 利用が期待できる高度な集積デバイスの中心課題になることは間違いなく、 スリー・ファイブでもこれらの材料を利用しなければならないと思っています。 材料と、その理解、その利用方法について総合的で有意義な議論が行わ れました。そして、高須氏が、非常に印象深い発表を行いました。これは、 - 一見単純なように見えますが,非常に多くの情報を含んだものです。彼は, - 次のように述べています。おそらく10年前には、非常にクリーンなシリ コンを作れば、N-MOSプロセスでもC-MOSプロセスでも、バイポ ーラ技術でも必要があればどこにでも利用できるだろうと考えられていま した。しかし、これは間違っていました。個々のプロセスは、各々、特殊 な性質の材料が必要であるということが発見されました。例えば、Aとい う業者はプロセスXだけを対象とし、Bという業者はプロセスYに最も適 - しているということです。魚には白ワイン,ローストビーフには赤ワイン を飲みたいといったようなものです。しかし,ある特定の工場,特定の目 的に合わせて設計されたシリコン・ウェーファーを作るということは,基 本的材料となるシリコンを非常に明確に理解し、加工技術を考案しなけれ ばなりません。テレフンケン社のGraff 博士は,加工中に混入する不純物 を除去するために使用している特殊な技術について非常に素晴らしい発表 を行いました。デバイスの設計と共に、単に基板材料だけでなく、製造工 程全体を通じて、各々に適した材料を考案しなければなりません。技術は、 - 互いに協力しながら発展しますが,各々の部分に個々の科学的アプローチ が必要とされます。このことは、非常にはっきりと現実に証明されている こと思います。材料やプロセスに対する経験的知識に頼る時代は過ぎ去りま した。非常に基本的な原理からこのような問題を理解しなければなりませ ん。扱っているディメンジョンが小さくなればなるほど、これらを深く理

このことは、従来は研究室でしか必要とされていなかったような基礎物 理学に基づく新しいタイプの装置・機器類が生まれ、これが、半導体産業 の成功によって不可欠の装置になるということを意味します。

解する必要性が高まります。

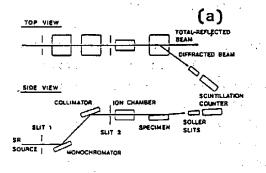

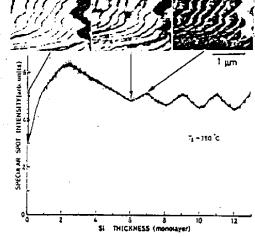

個々の要件に合わせた独自のプロセス技術を考案・制御できるように、材料とプロセス技術の分析は、できるだけ迅速にできなければなりません。この問題について、私たちの討論ではかなりの時間が割かれ、ほとんどの発表で取り上げられました。もう一つの例は松井氏が発表したもので、高エネルギー物理学における非常に高価で魅力的な手段であるシンクロトロン照射です。ご存知のように、ドイツはこの分野に非常に高い能力をもっています。非常に早くからこのことが認識され、また、ドイツには大型加速器や装置の伝統があるため、工学および科学が相乗的に発展しました。ベルリンとハンブルグには、さらに大型の装置とシンクロトロン技術があり、多くの人々がこの研究所にやってきてシンクロトロンについて研究しました。かれらは、帰国して、筑波やその他各地の様々な装置を使って活発な研究を進めています。

ここで、特性を調べるための技術を列記した長いリストを見せます。 X線は、非破壊的であるため非常に優れた有用な手段です。サンプルを分解する必要がありません。また、基本的には分光学的方法であるため、非常に多くの情報を包含しています。物質内部で進行している状態を、そのままの状態で観察する透過型 X線トポグラフィーについての説明が行われました。材料とプロセス技術を理解するための、平面波を使った平面波トポログラフィーという非破壊的技術も紹介されました。

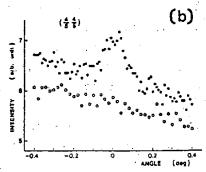

半導体材料内の様子を知ることは、半導体技術にとって重要な問題です。これは、転移量といって、特定の格子欠陥は非常に重要な意味を持っていると思われます。これは、固体物理学、結晶学、化学の基本的問題であり、転移密度の高いウェーファーと低いウェーファーの写真の対称性を見ればその違いが簡単にわかります。これをもとにしてガリウム砒素の基板を改良して、高速集積回路とオプトエレクトニクス装置に用いるガリウム砒素を作るための膨大な量の研究が日独両国で進められています。

もう一つの例は、小切間氏が発表したものですが、これは、結晶内部で進行している状況を知るための新しい方法です。しかし、これは先にのべた松井氏の写真だと思います。これは、建造中のモノクロメーターですが、新しい装置がどうやって作られるかということを紹介するためにお見せし

ます。これについてはかなり多くの成果が出ており、もっと優れた装置が 必要になっています。

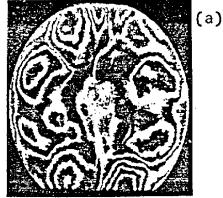

小切間氏は、X線の応用例も紹介しました。このようなアルミニウム・ ガリウム砒素ーアルミニウム砒素のヘテロ接合,カンタム・ウェルを観察 する新しい技術を紹介しました。ウェッジを作り、それをX線で観察する 〔САТ〕と呼ばれる新しい技術を発明しました。これは, 化学組成, イ ンタフェースの性質を調べるための非常に高度で感度の高い技術です。こ のウェッシの写真から, 新しいタイプのデバイスの性質を決める材料の性 質を調べる手段として利用できる技術の概要が理解いただけると思います。 他の電磁スペクトルの分野にも,迅速,非破壊的に高度な情報を示す分 光学的技術があります。これは、本研究所のWeber博士が紹介しました。 彼は、私たちの研究所が、よりクリーンで高性能のシリコンを望んでいる 人々に新しい方法と手段を提供するために試みている基礎研究の中から、 様々な活動を紹介しました。フォトルミネッサンスの強度が,ここに,波 長の関数としてプロットされています。これらの線には、非常に多くの情 報が含まれています。材料を照射し,そのルミネッサンス強度を見れば. 基本的な電子プロセスについて詳細な情報を得ることができます。例えば、 シリコン結晶内に作られた炭素対を見ることができます。炭素は、非常に 検出が難しく、材料にトーピングすることはありません。また、単なる供 与体や受動体ではなく、グラファイトや気体から、材料内に入ると思われ ます。炭素は、電気的に不活性であるという直接的な理由で重要なのでは なく、沈澱の核になるという間接的な理由で重要であり、結晶内の非常に

Weber博士と彼のグループは、この炭素一炭素対から発生する特殊な信号を発見し、この発光信号を使ってシリコン内の炭素検出限界を2桁引き下げることができました。これは非常に重要な成果で、新しいキャリブレーション曲線ができると思います。以前は、1cmのあたり5~15原子の炭素濃度しか測定できませんでした。これでも、以前から、あらゆる化学的な方法より非常に感度の高い方法でしたが、G線の強度を使うことによって、感度をずっと上げられることが立証されました。これは、シリコンの

繊細な構造を破壊するおそれがあります。

物理学的性質の完全な理解から生まれた非破壊的分光学的方法が非常に有用であることを示す一例です。

シリコン内に含まれる酸素も非常に重要な意味を持ち、研究分野でも開 発分野でも非常に活発に研究されているテーマです。酸素の量が,集積回 「路の成功,不成功の鍵を握っています。世界有数のシリコン・メーカーで あるWacker-Heliotronic のWagner 博士が, 酸素の作用, 例えば, 熱供与体 ( thermal donar ) について素晴らしい発表を行いました。 シリコン内で特 殊な熱が発生すると、酸素原子が集まって結晶内にドービングします。そ - して, 電気的活性を示し始めます。これらは, 熱供与体と呼ばれています。 これは、非常に困った現象で、結晶の持っている優れた性質を破壊します ので十分理解しなければなりません。ここに非常に優れた物理学的研究が があります。エネルギー・レベルを計算した研究ですが、これも私たちの 研究所が、産業界と協力して行ったものです。日本人研究者も、非常に高 度な技術を使ってこれに参加しています。 Wagner 博士は、彼の研究結果に ついても報告しました。熱供与体のシーケンスであるMa1とMa2の対があ ると思われます。焼きなましや熱処理を行うと、この対が行ったり来たり します。すなわち、非常に複雑で、複数の原子が関与する分子化学的変化 - がシリコン内で進行しています。これは,私たちが内部で起こっているこ とを理解する上で、非常に大きな意味を持っています。もっと小さいディ メンションのことを知るためには、これらを見逃すことはできません。個 々の物理的性質をよく観察しなければなりません。これは,他の発表でも 紹介されました。

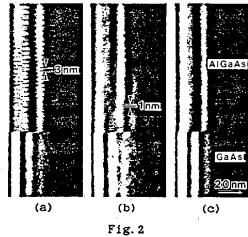

ご存知のように、電子顕微鏡は非常に重要な装置です。Siémens の Föll 博士と Oppolzer 博士が、日本製の高分解能電子顕微鏡を使った研究発表を行いました。彼は、電子顕微鏡の様々な応用例について素晴らしい発表を行いました。原子がどの位置にあるのかを知らなければなりません。例えば、この場合のこれは単結晶シリコン上のポリシリコンです。ここに点が見えますが、これは、個々の原子の回折像を表わしています。これが本物の原子と考えることは非常に危険ですから、やめて下さい。これは複雑な回折パターンです。何を見ているかを理解しなければなりません。Föll 博

士は、大型コンピュータを使って根本原理から適切な計算を行って回折パターンをシミュレートしなければ、見ているものが何かを理解することはできないと断言しています。

そして、非常に優れた警告を発すると同時に、実際に見ることができる 具体的なフリンジを示しました。これは、専門家を対象としたもので、インタフェースの格子フリンジです。これは非常に重要な意味を持ち、このインタフェースを理解しなければなりませんし、このような性質は電子顕微鏡の画面の解釈を非常に複雑にしています。ここや、ここで突然フリンジが停止しているのが見えますが、ここでフリンジが終わっているので、ここに転移欠陥があると早急に結論することはできません。これは、彼の発表と分科会での討論の中で学んだことであり、共著者の意見でもあるのですが、ここで、もう一度、科学的なインパクトということを強調したいと思います。すなわち、科学的原理に基づいて完全に理解しない限り、誤解が生じるおそれが大きくなります。

このような測定の中から収集できる情報は非常に重要であると申しあげましたが、研究室から生まれたもうひとつの例を紹介したいと思います。日本の論文のひとつが、マイクロプローブ反射の素晴らしい例を紹介しています。すなわち、高エネルギー電子を使い、これを反射させれば、材料内の状況を知ることが出来るというものです。ここで、小切間氏は、全般的にますます小さなディメンションに進んでいく傾向があると述べています。この場合は、データを高速で取得する(acquisition)能力をもつ非破壊的な手段だけでなく、電子顕微鏡と同じように、できるだけ小さいディメンションに進んで行かなければなりません。私たちは、結晶が成長する時の個々の非常に小さい結晶点を非常に丁寧に観察するマイクロプローブ反射の研究結果に大きな感銘を受けました。

何度も何度も繰り返されたテーマは、材料と材料のエピタキシーを理解 し、製造することが非常に重要なポイントであり、この材料の特性を決定 するということです。この二つは切り離すことはできず、私たちの議論で は、これについての素晴らしいアイデアが交換されました。そして、お互 いに強い影響力を及ぼしました。田中昭二教授と彼の研究グループの発表は、非常に優れたものでした。ドイツ側参加者になり代わり、日本側の出席者全員に感謝したいと思います。非常に熱心な討議が繰り広げられました。ご参会の方々に感謝したいと思います。意見の交換は非常に実りあるものでした。

## 4. 閉 会 挨 拶

## 4. 閉 会 挨 拶

## 4.1 新 欣 樹 通商産業省機械情報産業局電子政策課長

## [閉会挨拶]

エングル先生,柳井先生,トーマスさん,そして,ご列席の皆様! まずはこのフォーラムに参加された皆様が2日余りにわたるハードスケジュールを成功裏に終えられたことに対しまして敬意を表したいと思います。

ただいまの3つの分科会のサマリーレポートを伺いまして,今回のフォーラムがたいへん有意義であったとの感を深くしたしだいでございます。とくに,従来の情報技術分野における研究成果の情報交換に加えまして,今後の日独両国間の研究交流や共同研究の可能性といったことにつきましても検討をいたしましたことは,今後のこのフォーラムの役割を方向づけますうえできわめて重要な契機になったと認識をいたしたしだいであります。このように,今回,多大な成果を得ることができましたのも,エングル,

柳井両議長、親愛なるトーマス氏をはじめBMFTの皆さん、および日独 双方の主催者の皆様の周到なる準備とご努力の賜物であると考えます。

次回のフォーラムは来年の11月に京都か奈良で開催されるとのことで ございますが、その際には今回同様、有意義かつ活発な交流がなされるこ とを期待するしだいでございます。 ダンケシェーン。

## 4.2 U.トーマス 研究技術省第4局次長

## 〔閉会挨拶〕

このフォーラムを終えるに当り、一言ご挨拶を申し上げたいと存じます。 この活動が年々盛んになってきて嬉しく存じます。私共は、ますます得る ところが増えてきているという印象を持っています。議論百出致しました が、明らかにレベルの高いものでした。お互いに議論ができ、しかも非常 にオープンに議論できるという信頼感が増してきております。この事はい つも重要な事でした。

また、うれしい事に、ドイツ側のGMDと日本側のJIPDECの間の協力で、今回のフォーラムの準備から実際の運営まで、順調に行われたと思

います。この場をかりまして、GMDとJIPDECの皆様のご尽力に対し 感謝の意を申し上げたいと存じます。といいますのも、その仕事は決して 簡単なものではなかったからです。このように困難で複雑な事柄を組織化 し、運営する場合には、いつでも距離というものが重要な要素となります。 今回のフォーラムの準備から運営まで参加して重要な役割を担ったわれわ れドイツ側の1人は、近い将来、東京に赴任することになっております。 その結果、両国にとって非常に良い、情報技術のための橋渡し役となるで しょう。

率直に申し上げて、この会場には研究関係の官庁の方が何人かいらっしゃっていますが、私共にとってこの種の行事は大いに役立つものだと申し上げたいと思います。と申しますのは、これによって、情報技術の分野での研究を促進するに当っては、関係官庁からの視点も含めて、一体どういった種類の取り扱い方が、適切なものなのかという事について思いめぐらしているからなのです。私はまた、新電子政策課長より、どのように日本の通商産業省がきめこまかく自国の産業を指導しているかを教えてもらおうとも致しましたが、いくつかの詳しい説明をいただきましたので、われわれの参考にさせていただきたいと思います。

次回のフォーラムは日本でというご招待にはうれしく存じます。私共皆 よろこんで参加したいと思いますし、なによりも当然のことながら、この フォーラムの使命の一つは、科学者・技術者の交流、科学技術の交流にあるのだと申し上げたいと思います。また、両国の友情を深めるという使命もございます。このことは、この席を貸りまして、率直に申し上げたいと思います。私共は、ドイツと日本の科学者同士の友情を深めたいと思っています。私共は、ドイツと日本の科学者自身のためになるからであり、かつ私共両国のためにもなるからだと思っています。さらに申し上げれば、次回のフォーラムは、今回よりも一層中味の濃いものとなり、われわれが若い科学者の人達に日本で仕事をしたり、反対に日本の若い科学者達に、このドイツ連邦共和国で仕事ができるような、もっとたくさんの可能性を与えるにはどのようにしたら良いのかという事について、議論をすることになるでしょう。これは必ずしもやさしい事ではないのはもちろんですが、言葉の

壁, まあわれわれドイツ側からの方が, ひょっとしたら日本の科学者よりも躍び越えるのが難しいかも知れませんが, このような壁があります。しかし, もちろん, 相互に知り合う事が重要であり, そこではおたがいに最善の形で出会うことができると思います。そして思いますに, このフォーラムの場で両国の科学者にもっと相互の交流のチャンスを与え, 日本とドイツで共同研究作業をしてもよいという時期が今, 熟してきたと思います。そして, この基礎をここにうち建てるお役にたてたことと思います。このことは誰しもが願っていることです。

また、お礼申し上げなければならないのは、民間企業からこのフォーランムに参加して下さった方々です。この場を借りまして厚くお礼を申し上げたいと思います。多くの民間企業の方々の参加がなければ、今回のフォーラムの価値は間違いなく半減したことでありましょう。

新電子政策課長、さて最後にもう一度言わせていただきたいと思いますが、私自身非常にうれしく思うのは、日本の通商産業省とのコンタクトが年々密になって、また他の通商産業省の方々とも面識を得る機会ができたということなのです。私自身の側からただ申し上げたいのは、…というのは皆様に申し上げたいのですが、エンゲル先生がまだこれから閉会の辞を述べられますので、…皆様方、帰路つつがないよう、そしてまたここにお越しいただいたことを再度お礼を申し上げたいと思います。この当地にて、お骨折りいただいたのは、クワイサー教授と研究所の皆様ですが、ボンから参りました私共に対して温かくおもてなしいただいたことについてお礼を申し上げたいと思います。われわれは、本当にバーデンビュルテンベルク州とこの研究所をおとずれてよかったと思います。われわれは皆来年日本でお会いできることを本当に楽しみにしております。ご清聴ありがとうございました。

## 4.3 W. L. エングル ドイツ側議長 アーヘン工科大学教授

〔閉会挨拶〕

皆様,お疲れさまでした。せっかくおいでいただきましたのに,十分な

お世話もできませんで失礼いたしました。次のフォーラムではまたお互い に頑張りましょう。無事お帰りください。ありがとうございました。

.

5. ニューメディア分科会アブストラクト

## 5. ニューメディア分科会アブストラクト

LOW- AND HIGH-VOLTAGE THIN FILM TRANSISTORS FOR ADDRESSING FLAT PANEL DISPLAYS

Prof.Dr.-Ing. Ernst Lüder

Each picture element (pel) of a liquid-crystal-flat-panel display (LC-display) is, as a rule, addressed by a circuit consisting of a thin-film transistor (TFT) and a storage capacitor. Fabrication processes and performance of CdSe-TFT's and a-Si-TFT's are reported. Both transistors possess a double-layer gate-dielectric out of anodized  ${\rm Ta}_2{\rm O}_5$  and evaporated or  ${\rm CVD-SiO}_2$  . Due to a three-step annealing process the CdSe-TFT exhibits very good properties, namely a mobility of 160 cm $^2/\text{Vs}$ , a switching ratio  $R_{off}/R_{on} = 10^9$ and an  $I_{off}$  = 0.1 pA at 3000 lux. A 12 000 pel-display was fabricated with and, for the first time for CdSe-TFT's, also without storage capacitors. The latter was feasible because of the low  $I_{\mbox{off}}.$  The display without storage capacitor provides a higher contrast and a wider viewing angle than the display with C's. This is achieved by the elimination of a parasitic capacitive voltage divider. Optimum contrast without storage capacitors is 1:48, the viewing angle for a contrast 1:16 resp. 1:8 is  $45^{\circ}$  resp.  $50^{\circ}$  in horizontal direction. Pel-yield was 99.8 % inspite of fabrication in a non-dustfree laboratory. This stems from a robust fabrication process and from overdesigning the devices. The self-healing property of anodization virtually eliminates failures in the dielectrics, whereas the TFT's could be built to withstand 100 V and to switch in 1  $\mu s$ , both exceeding the requirements for LC-displays.

The high voltage CdSe-TFT is based on reactively sputtered Ta $_2O_5$ -dielectric which is anodized afterwards in order to withstand 400 V. The spread in break-through voltage was very narrow with a standard deviation of  $\sigma=0.05$ . This TFT was used to address a PLZT-light valve with a switching time  $\leq$  1  $\mu s$ . The high voltage TFT is also suitable for addressing VF- and EL-displays, where the high currents of CdSe-TFT's of 500  $\mu A$  per 100  $\mu m$  channel-width are actually required. The current in a-Si-TFT's with SiO $_2$  or SiN as gate dielectric amounts to about 3  $\mu A$  per 100  $\mu m$  channel-width. In a-Si-TFT's with Ta $_2O_5$ -dielectric the current was enlarged to 12  $\mu A$  per 100  $\mu m$  due to the higher dielectric constant of Ta $_2O_5$ , even though a double layer dielectric of Ta $_2O_5$  and SiN was used. In all cases the TFT's had the same thickness of the gate dielectric. A comparison between the CdSe-TFT's and a-Si-TFT's will conclude the talk.

## A Large Full-Color Flat Panel Display for HDTV

## Teruo Hirashima

NHK Science and Technical Research Laboratories, Tokyo, Japan

#### 1. Introduction

HDTV is an entirely new television system which fullfills viewer's demand for a high quality, wide screen picture. It transmits five times the amount of information received by conventional television. It has a sense of presence and reality, and has a great impact on viewers.

26~40-inch CRTs and 50 ~400-inch projection type displays were already developed for HDTV, but for home-use a thin flat panel display is preferable because of space and weight. A flat panel is an ideal display, but there are many problems not yet solved and its research and development still has a few risks.

The development of a flat panel for TV is more difficult than for datagraphics, because TV display requires full-color, good grey tone and high speed of response.

## 2. Current technologies

Table 1 shows an example of specifications required for HDTV display and Table 2 the comparison of devices used for a flat panel for HDTV on the specifications shown in Table 1.

#### (1) Plasma display panel (PDP)

PDP is most promising for a meter-size, large panel. Its feasibility depends upon the precise fabrication technology. Because of limited resolution due to areas occupied by phosphor and cell barrier, full-color PDP is not suitable for a small panel. It is superior to CRT when its size is over 40-inch-diagonal large panel. To produce tri-color, PDP uses UV rays to excite phosphors, but luminance and efficiency are not sufficient because of a small pixel volume. It is necessary to search for gas composition and discharge mode to radiate more intense

UV rays with higher efficiency.

(2) Electroluminescent display (EL) and light emitting diode (LED)

The main bottleneck of EL and LED for a full-color panel is a poor blue light emission, and the basic research has to be done to find out new materials.

ZnS:Mn and SrS:Ce were reported as blue light emissive EL materials, but ZnS:Mn has insufficient luminance of only 3 ft-L and efficiency of 0.002 lm/V and SrS: Ce is not good in blue color purity.

In the case of LED, SiC, GaN, ZnSe and ZnS which have a bandgap over 2.6 eV were developed, but none of them have obtained sufficient luminance as yet.

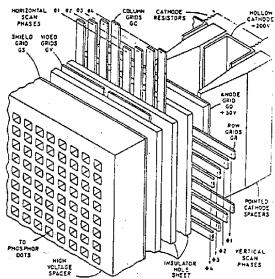

(3) Flat CRT and vacuum fluorescent display (VFD)

High(5 $\sim$ 30 kV) or low(50 $\sim$ 150V) voltage cathodoluminescence is utilized to obtain high brightness and good color. In conventional CRT, an electron gun has to be placed far from the screen, to obtain a wide deflection angle of electron beam. This makes CRT bulky.

Various concepts of a flat full-color CRT have been investigated, but none of them are successful.

In the first type of flat CRT developed by U.K. Philips, electron beam scanning and energizing function are separate. Its scanning system is housed in a flat package, because a low energy electron beam is easily deflectable, and a large area channel multiplier is used to get high energy electrons which excite the phosphor screen. In this way, monochrome panel of 12 inch screen 75 mm deep was developed.

The second approach of flat CRT was made by Matsushita. It uses multi-line filaments instead of a single gun and several kinds of line electrodes for adressing and modulation. A full-color panel of 10-inch screen 65 mm deep was developed. This structure is similar to VFD.

The third concept of flat CRT utilizes two dimensional gas discharge cathode or plasma cathode, as an electron source, which was reported by Siemsns (11.5-inch screen 60 mm deep) and Lucitron(35-inch screen 5 inch deep).

In all three cases, spacers must be used to be pressure resistant so a new

concept should be introdused for the sake of compatibility of high resolution and a large area screen. Furthermore it is very difficult to fabricate complicated electrodes throughout a meter-size panel. From these viewpoints, a plasma cathode flat CRT is most promising for a large flat panel. VFD has a problem in power consumption when it is made large.

## (4) Liquid crystal display ( LCD )

LCD has attractive features: flatness, low power consumption, low voltage drive and good full-color. But in the twisted nematic (TN) LCD which is now widely used for many purposes, the contrast greatly decreases as scanning line increases owing to an inevitable crosstalk between pixels on the same line. To avoid this, active addressing was investigated to separate each pixel by an electrical switch. A thin film transistor (TFT) is currently used as a switch.

At present 2~4 inch active adressed portable TV receivers are commercially available. Its size will increase 14 inches in five years, but defect and uniformity will be more significant.

## 3. A 20-inch full-color PDP developed by NHK Laboratories

Recently NHK Laboratories developed a 20-inch panel of which size is the biggest as a full-color PDP. It is a pulse discharge memory panel of simple structure which is favorable for a large panel (Fig.1). Its luminance is rather low (about 30 cd/m) but it is most feasible to achieve a large panel.

Fig.1 PDP of a simple structure

Table 1 Disirable specications of HDTV display

Scanning line 1125 Field frequency 60 Hz Aspect ratio 16:9 Screen size 0.8 m (vertical) x 1.4 m (holizontal) Viewing distance 2.4 m (three times screen height) Horizontal viewing angle 30° Luminance \_ 150 cd/∞ m<sup>2</sup> Contrast ratio 70:1 Luminous efficacy 1.5 lm/W

Table 2 Characteristics of devices for a HDTV flat panel display

|            | acreen | defini- | lumi= | full-    | thick-<br>ness | power<br>consump. | total |

|------------|--------|---------|-------|----------|----------------|-------------------|-------|

| PDP        | ©      | 0       | Δ     | <b>©</b> | <b>©</b>       | Δ                 | 0     |

| EL         | Δ      | 0       | Δ     | ×        | 0              | Δ                 | ×     |

| LED        | - Δ    | Δ       | 0     | ×        | 0 '            | Δ                 | ×     |

| Flat C R T | Δ      | 0       | ©     | ©        | Δ              | 0                 | Δ     |

| VFD        | ×      | Δ       | 0     | 0        | Δ              | Δ                 | ×     |

| LCD        | Δ      | 0       | 0     | 0        | 0              | Δ                 | Δ     |

<sup>©</sup> excellent, ○ fair, △ good, × not good

## Materials for colour TV based on Liquid Crystal Technology Dr. U.-H. Felcht

The fast development of high information Liquid Crystal Displays involves new challenges for chemical material science. The complex construction of a Liquid Crystal Display requires specially optimized materials. They must be compatible both as regard to the production of the displays and in its functions. In this case it is desirable that the chemical industry develop a balanced product package for the electronic industry. Of particular importance for high information color LCD's (TV) are new fast switching liquid crystals, optimized orientation layers, photoresistmaterials, high density color-pixel filters and sealing materials.

Ferroelectic, smectic C\*, liquid crystals are basically characterized by fast switching time, bistability and improved contrast ratio. Unsolved problems concerning bistability, grey scaling and shockproof are being worked on very intensively. Solving the problems from the chemical angle offers many advantages against the TFT/nematic-technology. The high density colour-pixel filters can be produced by structurized dye printing techniques or by electrophoretic methods. Photoresists and Sealings have to be compatible with LCD materials during processing steps.

## FLAT CRT

## Kinzo Nonomura Central Research Labolatories Matsushita Electric Industrial Co., Ltd. Osaka Japan

## Introduction

A considerable amount of effort has been made to develop a variety of flat CRTs in the past decade. The progress made in the field of color technology has been remarkable. Nevertheless, we still do not have flat color CRTs, which are up to the standards of quality set by conventional CRTs, put into practical use. In this paper, present status and some considerations on future of flat CRTs are described.

## Types of flat CRTs

Various types of flat CRTs have been devised since Aiken Tube and Gabor Tube back in the nineteen-fifties. The types of flat CRTs may be classified into three groups according to the structure of cathodes as shown in Table 1. Five typical types from Table 1 are shown in Figs. 1-5.1)-5) One of these types, namely, Matrix Drive and Deflection System (MDS) flat CRT reported by the author in 1985 will be described in some detail referring to Fig. 1. In the MDS flat CRT, 3000 controlled beams are formed by means of a matrix of 15 horizontal filament cathodes and 200 perpendicular electron beam control electrodes. Each beam is horizontally deflected in 6 steps (two sets of R.G.B.) and vertically deflected in 32 steps (including the interlace) to form an image consisting of 192,000 elements on the display panel. A complete picture is formed by means of a line-at-a-time method.

The inherent advantages of MDS flat CRT are:

- 1) Flatness of the screen and good linearity of the picture,

- 2) Good uniformity of the beam focus throughout the screen,

- 3) Freedom from convergence problems,

- 4) High resolution and high brightness,

- 5) Possibility of a large screen panel with a self-supporting structure.

## Some considerations on future of flat CRTs

The important factors in realizing a color flat T.V. are:

- 1) Uniformity of beam current,

- 2) Uniformity of beam spot size and shape,

- 3) Accuracy of beam landing position.

· Lack of any of these factors results in poor image quality.

In a single-point cathode type, he beam current is uniform in principle. In multi-cathodes or area cathode types, it is necessary to take some measures for realizing above mentioned three requirements. It may be a feedback system for beam currents, or application of dynamic focusing voltage, or the beam index'system, for instance.

No matter what the size of the conventional CRTs is, the basic principle is the same shadow mask system. While there can be a number of different types in the principle of flat CRTs.

The future principle of flat CRTs will be not necessarily one but a number of types according to the screen size, resolution, etc., of the display. In any case, certain measures would be incorporated to realize the above mentioned three requirements.

#### References

- 1)M.Watanabe, K.Nonomura, et al., SID 85 DIGEST, pp.185-186,1985

- 2)M. Yamano, et al., IEEE Trans.on C.E., Vol.CE-31, No.3.PP.163-173, 1985

- 3)D.L.Emberson, et al., SID 86 DIGEST, PP.228-231, 1986

- 4)R.Meyer, et al., JAPAN DISPLAY '86, PP.512-515, 1986

- 5)M.Dejule, et al., SID 86 DIGEST, pp.410-413, 1986

Table I Classification of flat CRTs

| Cathode type.                | Types of flat CRT                                                                                                       | Companies who investigated                     |  |  |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--|--|

|                              | (1) Flat CRT with a side gun<br>(2) Channel Multiplier Flat CRT                                                         | Sony, Sinclair, Hitachi, Sanyo<br>Philips      |  |  |

| Multi-cathodes               | (1) Guided-Beam Flat CRT (2) H-addressing and V-deflection system                                                       | RCA<br>Kanazawa Inst. of Tech.                 |  |  |

| Two-dimensional area cathode | (1) XY matrix addressing (1) VFD (11) Hybrid Plasma Flat CRT (111) Microtips FD  (2) Matrix Drive and Deflection System | LETI-IRDI-Commissariat a<br>I'Energie Atomique |  |  |

Fig.1 MDS flat CRT (Matsushita)

Fig. 2 Flat CRT with a side gun (Sanyo)

Fig. 3 Channel Multiplier Flat CRT (Philips)

FIG.4 Microtips F. D. (Leti-IRDI-CEA)

Fig.5 Hybrid Plasma Flat CRT (Lucitron)

#### SOLID-STATE LIGHT VALVES

## R. Gerhard-Multhaupt

Light-valve projection represents a proven technique for the display of large and bright high-resolution video images. The centerpiece of a light valve is a spatial light modulator which modifies the light from a suitable source by means of reflection, refraction, birefringence, diffraction, or scattering. Addressing and control of the spatial light modulator is achieved with electron beams, light beams, primary images, passive or active matrices. The resulting light modification consists of spatially varying changes in the propagation direction, the phase, or the polarization and is transformed into the required intensity modulation by input and output filters that also absorb the light not required for the desired image.

In this talk, several spatial light modulators and addressing techniques, as well as combinations thereof, are discussed on the basis of commercially available or experimental light valves. Solid-state technologies are emphasized, since they promise compactness, fast response, reliability, high resolution, and full integration of light-control and addressing devices.

Control layers modulating the phase or the propagation direction of the incoming light are used in a Schlieren optical system which provides for the required intensity modulation of the output light. Examples of such devices include deformable layers of fluid or viscoelastic materials, liquid-crystal cells or electro-optic substrates which scatter or diffract light, and deformable mirrors or membranes.

Spatial light modulators, which are based on electrically induced birefringence, change the polarization state of the light and thus necessitate polarization optics for the desired conversion to intensity-modulated light. This control-layer category encompasses twisted-nematic (TN), highly (HBE) or super-twisted birefringence-effect (SBE), and surface-stabilized ferroelectric (SSFLC) liquid-crystal cells as well as electro-optic layers from anorganic or organic crystals, ceramics, and guest-host polymers.

Addressing and control of the spatial light modulators may be effected by electric field variations, which are in turn generated by electron-beam-deposited charge distributions, light-beam- or image-induced photoconductivity patterns, externally driven row and column electrodes, and matrices with active elements for each pixel.

Our goal, the active-matrix-addressed solid-state high-resolution spatial light modulator, represents the counterpart to the solid-state imaging device already available. It may be used not only for the light-valve projection of large images, but also e.g. as an input or filtering device in optical-signal or image processing applications, as coherent-to-incoherent, incoherent-to-coherent, or wavelength converter, as a light-controlling element in adaptive optics, and as a routing and switching device for optical interconnections.

# High-definition Television Transmission in Telecommunications Tetsuya MIKI NTT, Research & Development Headquarters

Since HDTV's bandwidth is very wide compared to that of existing TV system, wideband transmission including bandwidth reduction coding is essential.

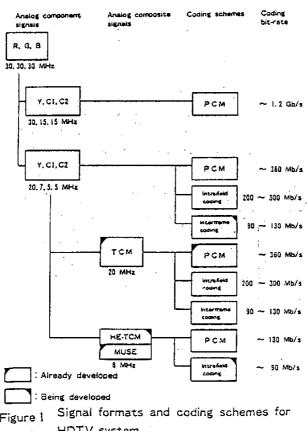

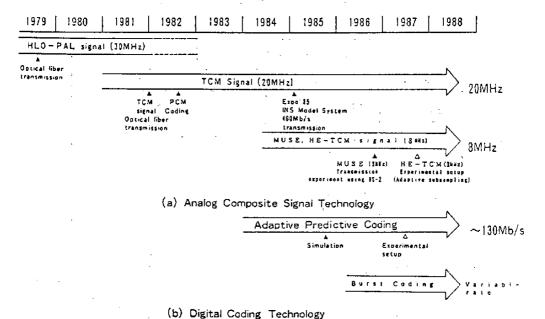

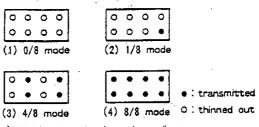

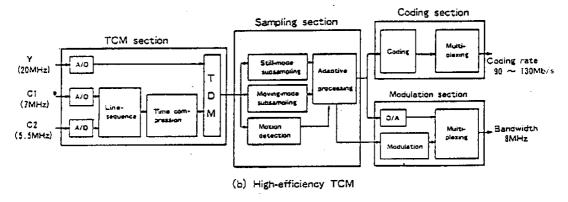

Signal formats and coding schemes for HDTV are shown in Fig.1. The history of HDTV video technology development in Japan is shown in Fig.2. We have already developed 20 MHz Time Compression Multiplexing (TCM) video signal. The two bandwidth reduction technologies being developed in Japan are "MUSE" and "High-efficiency TCM (HE-TCM)". In the future, burst coding, whose bit-rate is variable, would be one of the most important technology in Asynchronous Time Division (ATD) network. HE-TCM signal as shown in Fig.3 is obtained by adaptive sub-Nyquist sampling (subsampling) with intrafield and interframe interpolations. This method reduces HDTV signals to 8 MHz bandwidth, and these compressed signals are converted to 90 ~ 130 Mb/s digital HDTV signals by also applying DPCM or PCM coding technologies.

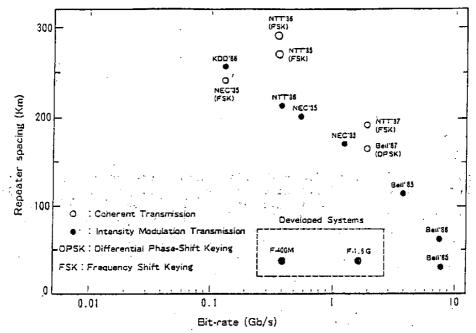

In telecommunications, there are various types of large-capacity transmission systems applicable to HDTV transmission: optical fiber cable, coaxial cable, satellité, and terrestrial radio transmission systems. Optical fiber cable transmission and satellite communications technologies, which are especially attractive for HDTV transmission, have already been developed. Table 1 shows the NTT's optical fiber cable transmission system (land system). The F-1.6G system, which has the transmission capacity of 1.6 Gb/s, has already been developed as a large-capacity transmission system. Furthermore, coherent optical transmission technologies are now under study. Figure 4 shows recent trends in long-distance, super large-capacity optical transmission experiments. By using new super large-capacity transmission, HDTV signal can be transmitted more economically. Analog high-efficiency TCM signal and digital adaptive predictive coding technologies are under development for application to HDTV. As digital equipments such as HDTV receivers become smaller and their power consumption is reduced by VLSI technology, HDTV transmission service becomes more and more economical.

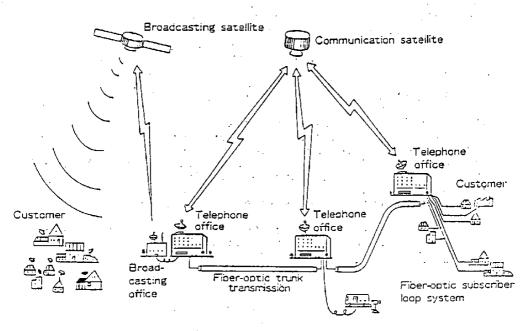

Figure 5 shows the HDTV transmission concept for the future. HDTV broadcasting signal will be distributed to customers using a direct broadcasting satellite system, communications satellite and optical fiber cable transmission systems. In addition, since HDTV signal will be transmitted nation-wide, various applications of the HDTV system will become available.

HDTV system

Figure 2 Development of HDTV video technologies

(a) Multi-mode adaptive subsampling

Figure 3 High-efficiency TCM

Table 1 Optical Fiber Cable Transmission System (Land system)

|                           | F-6M           | F-32M        | F-            | 100M | F -400M      | F-1.6G       |  |

|---------------------------|----------------|--------------|---------------|------|--------------|--------------|--|

| Line Cade                 | CWI            |              | 8 B 1 C       |      | 1081C        |              |  |

| Information<br>Bit-rate   | 6. 312Mb/s     | 32.06Mb/s    | 97. 728Mb/s   |      | 397. 200Mb/s | 1. \$888Gb/s |  |

| Line Sitrate              | 12. 624Mb/s    | 64. 128Mb/s  | 111. \$89Mb/s |      | 445. 237Mb/s | 1.7833Gb/s   |  |

| Capacity<br>(64Kb/s Tel.) | 95ch           | 480ch        | 1440ch        |      | 5760ch       | 23040ch      |  |

| Wavelength                | 1.2, 1.3<br>μm | ł. 3 μm      |               |      |              |              |  |

| Optical Fiber             |                | G [          |               |      | S M          |              |  |

| Source                    |                | inG.         | aAsP L        | D    |              |              |  |

| Detector                  |                | G            | InGaAs-APC    |      |              |              |  |

| Repeater<br>Spacing       | 15 km          | 10. 15. 25km | 25. 30 km     |      |              |              |  |

| Bit Error Rate<br>/Rep.   | 10-14          | 10-"         |               |      |              |              |  |

Figure 4 Recent trends in long-distance large-capacity optical transmission experiments

Figaure 5 HDTV transmission concept for the future.

## Review of Proposals for HDTV Transmission

Dr. Ludwig Stenger

#### Abstract

The contribution is subdivided into three sections. In the first there is a discussion of the transmission media available or under active research. Usefull satellite bands at 12 GHz, 22 GHz and 42 GHz are considered and the characteristics of channels allocated during WARC '77 and the status of the planning efforts in the European Broadcasting Union (EBU) for 22 GHz are explained. Alternative approaches by medium power satellites are indicated. HDTV transmission in the "hyperband" of CATV systems and in future broadband ISDN systems based on optical fibre technology are discussed. TDM system proposals and the status of work on coherent optical transmission systems are considered.

In the second section transmission formats for 12 GHz-WARC-type channels ("smallband channels") and for channels above 12 GHz with a "wider" RF bandwidth are discussed. Signal processing techniques, necessary to adapt the original HDTV signal bandwidth to the available channels are considered too. Rather sophisticated motion adaptive filtering and subsampling techniques have to be used for the transmission of HDTV through WARC channels by MUSE and HD-MAC (Eureka, EU 95). There are less stringent signal-processing requirements in case of two-channel systems, of wideband MAC-compatible techniques and of wideband non-compatible, revolutionary systems. Digital assisted televison (DATV) is a usefull technique in all applications.

All-digital solutions are possible in 22 GHz satellite channels and on the optical-fibre based B-ISDN. For that, source coding techniques for data-rate reduction have to be investigated and appropriate modulation and multiplexing schemes have to be considered. In Europe these subjects are dealt with in supra-national projects RACE and COST 206. Some of the proposals made there are outlined.

In the third section the status of research and implementation work is reviewed and a scenario for the introduction of a <u>HDTV</u> service is outlined.

### PROGRESS IN HDTV RECORDING TECHNOLOGIES

#### Yoshitaka Hashimoto

Sony Corporation

Information Systems Research Center

4-14-1 Asahi-cho, Atsugi-shi

Kanagawa-ken, Japan 243

Phone (0462) 30-6165

The HDTV analog VTR has been available for practical applications for a period of 4 years. However, the picture quality is not yet fully satisfactory because of limited bandwidth, relatively low signal to noise ratio, and picture quality degradation due to multiple generation dubbing. In order to cope with these difficulties, the advent of the HDTV digital VTR is strongly desired. This paper describes the recent technical progress in our HDTV digital VTR development.

In 1985, we developed an experimental HDTV digital VTR with a bit rate of 1.037 Gbps in an effort to realize a high quality production-use VTR. This machine successfully demonstrated the feasibility of such ultra-high speed recording. However, the signal parameter values were chosen principally for experimental purposes. The results from this experimental VTR were presented at the 3rd Germany Japan Forum on Information Technology in Tokyo, October 1986.

In May 1986, the CCIR reported the proposal for a new recommendation of parameter values for HDTV in Report 801. Although no accepted, these parameter values are the only ones available so far, and it is necessary to confirm the technical feasibility of digital tape recording through the extensive study of high speed recording technology.

With some modifications to our previous machine, we succeeded in realizing an experimental HDTV digital VTR with a total bit rate of 1.188 Gbps. By adopting a luminance sampling frequency of 74.25 MHz, that is 5.5 times the 13.5 MHz sampling frequency of CCIR Rec. 601. the proposed parameter values in the CCIR Report 801 have been fully satisfied. Using the same number of 8 recording heads as the previous machine, the recording rate per channel is 148.5 Mbps and the minimum recording The measured S/N at the wave length is 0.69 µm. decision point is approximately 26 dB(pp/rms) and the raw bit error rate is roughly  $2.5 \times 10^{-5}$ . Using the error control mechanism based on Reed-Solomon product code with overhead for parity, sync code and ID code included in the blanking period, the errors are almost completely level sufficient for practical corrected to the applications. Even after 20th generation dubbing, no picture quality degradation has been observed.

Further distinctive features of this newly developed machine are: 8 channels of professional quality digital audio sampled at 48 KHz with 16 bit/sample linear quantization recorded on 8 longitudinal tracks, and reduced processor size by utilizing VLSI chips developed for the 4:2:2 digital VTR and other advanced semiconductor devices.

Table 1 shows the parameters of the new experimental HDTV digital VTR.

In conclusion, the development of a new experimental HDTV digital VTR which meets the draft HDTV studio standard shown in CCIR Report 801 has verified that ultra-high speed recording and playback at 1.188 Gbps is feasible.

## References

- (1) Y. Hashimoto, "HDTV Recording Technology", the 3rd Germany-Japan Forum on Information Technology, Tokyo Oct. 22-24, 1986

- (2) Y. Hashimoto, "Experimental HDTV Digital VTR with a Bit Rate of 1 Gbps", 1987 International Magnetic Conference, FB-07, Tokyo, April 14-17 1987

- (3) H. Tanimura, Y. Hashimoto, T. Yoshinaka, "HDTV Digital Tape Recording", the 15th International Television Symposium and Technical Exhibition, Montreux, June 11-17, 1987

#### Table 1. Parameters of the experimental HDTV DIGITAL VTR developed in 1987

## Mechanical and Tape Format

Tape Metal particle type (Hc:1440 Oe, Br:2150 G) Tape width 1 inch

805 mm/sec Tape speed

1.0 hours using 11,75 inch reel with 18  $\mu m$  thick tape Recording time

Video Recording

Head Recording: Sendust sputtered type

Playback : Ferrite Head gap length Recording:  $0.35 \sim 0.4 \mu m$

Playback:  $0.25 \sim 0.3 \mu m$ 37 μ⊞ Track pitch

Recording: 34 μm Playback: 27 μm Track width Number of channels

Drum speed 7200 rpm

Audio Recording Head Recording: Thin film type

Playback : Ferrite Recording: 1 μm Playback: 0.65 μm Hed gap length

Track pitch 400 µm

Recording: 360 μm Playback: 200 μm Track width Number of channels 8 (max)

one channel per one track

Video Signal Format

Y 30 MHz R-Y 15 MHz, B-Y 15 MHz Video bandwidth

(recorded simultaneously) 74.25 MHz sampling frequency Y

R-Y 37.125 MHz, B-Y 37.125 MHz

8 bit/sample, linear Quantization S/N 58.8 dB

1.188 Gbps Data rate

Error correction using a Reed-Error Control

Solomon product code: Error concealment using an adoptive method

Channel coding Scrambled NRZ:8-8 conversion

Minimum recording wave length 0.69 µm

Audio Signal Format

Sampling frequency , 48 KHz 16 bit/sample, linear Quantization Error control Cross-interleaving with CRCC Channel coding HDM-1

#### M. Hausdörfer

Pickup Tube or Solid State Imager

- Alternatives for HDTV Image Signal Generation? -

At first glance, this subject does not seem to be of immediate interest - because the pickup tube with semiconductor target stands on the summit of its technology and the silicon solid state imager, used in colour television cameras, steadily gains attention and its share of application. The outcome of this match is predictable.

All this is true for standard television.

High resolution picture taking systems with signal bandwidths of more than 20 MHz - as the HDTV systems use - are continously fighting aperture losses and the impairment of signal to noise ratio, besides other aggravations due to registration problems, etc.. In addition, there is the basic demand for an unchanged sensitivity of the HDTV camera as compared to the standard TV camera.

The silicon solid state image sensor is provided with some features in signal generation, which the pick up tube does not possess. But both devices considerably differ in the characteristics of the noise spectrum that influence the subjective weighting of the perceived noise of the displayed picture.

This contribution deals with the relations of picture signal generation and signal to noise ratio taking the limited definition capability of the pick up device into consideration.

#### Mr. Hori

#### GENERAL INFORMATION ON THE HDTV SYSTEM

The high definition TV (HDTV) system has been rapidly introduced into broadcasting and other industrial uses.

The HDTV system is being tested in experimental broadcast via the BS-2 satellite in Japan, and is expected to come into use in covering the 1988 Olympic Games.

From the viewpoint of practical use, state-of-the-art technology has not necessarily been embodied in the hardware for the HDTV system. It seems that only part of potential basic technology has been put to practical use. The realm of technology for the most part sill remains to be explored.

The following is the latest information on the camera which plays one of the important roles in the HDTV system.

#### [Sensitivity and S/N]

The typical sensitivity of current HDTV cameras on the market is equivalent to F3.2 at an illumination level of 2000 lux. The low sensitivity was one of the most important problems since it was lower by 1 to 1.5 stops than that of the broadcasting cameras currently in use. Among factors that have helped solve this problem are the development of a new pickup tube and improvement in transmittance of beam splitting prism and the performance of the pre-amplifier connected to the pickup tube. As a result, the sensitivity has tripled to F5.6 at 2000 lux, and the S/N ratio of 44 dB has increased by 5 dB to 49 dB. Naturally, the improvement in S/N ratio can translate into an increase in sensitivity.

#### [Resolution and Lag]

At present, the resolution of a still picture can be said to be acceptable.

The problem is dynamic resolution deterioration. It is related to the pickup tube lag. In this respect, a remarkable improvement has been attained; the new pickup tube has attained resolution comparable to that of the current broadcasting cameras.

#### [Digital DTL]

A digital DTL is not necessarily essential for the current broadcasting system so that an analog DTL serves the purpose. However, the digital DTL is indispensable to the HDTV system that involves great difficulty in generating the DTL signal and needs elaborate operations. It should be noted that the hitherto prohibitively expensive DTL now cost half as much as before due to advances in semiconductor technology and use of less expensive devices.

#### [Size Reduction of Camera]

Generally, the TV camera can be reduced in size through simplification of the circuitry, employment of ICs, and reduction in power consumption.

The greatest of all advantages of a compact camera is a reduction in price.

However, it seems almost impossible to develop the camera that at once meets the performance requirements of the HDTV system and equals the so-called "handy cameras" which are in wide acceptance in the current TV system.

How much can the camera be reduced in size at the present technical level?

#### [Lens]

The image reproduction by the HDTV system is fraught with many problems (e.g. longitudinal chromatic aberration, lateral chromatic aberration, and distortion). The details will be given later. Briefly, any zoom lens currently available fails to give the required performance. It is unlikely that this problem will be solved all at once in the near future.

Unlike in the case of the current TV system, a sophisticated shooting method need be employed for better image reproduction. In fact, many film production methods have been incorporated in the HDTV system software development. This approach is called electrocinematography. The study on the advantages of film production technology of a long history has led to the development of a fixed focal lens with enhanced performance. Of course, a low-magnification zoom lens has been developed in parallel.

#### [Reduction in Running Cost]

The running cost of the present camera is very high partly because of a relatively short service life of the pickup tube. The new pickup tube is designed to last as long as tubes used in the present TV system. This means a considerable reduction in the running cost.

Autostereoscopic Three-Dimensional Television Experiment Using Lenticular Sheets and a High-Resolution Braun Tube

#### J. Hamasaki

Institute of Industrial Science, University of Tokyo

1000 200

,

####

For realization of an autostereoscopic 3D television, it is essentially important to reduce informations to be displayed for an observer, because optical wave informations from a 3D object are too large to be handled electronically in real time.

It is an acceptable hypothesis that an image recognized by a human observer is the image which is created in his brain from data percepted by his eyes. To display a 3D image, therefore, it is sufficient if constituent data enough for a human brain to create an unambiguous image in real time are supplied. This means that informations necessary for 3D image display can be tremendously reduced, when the observer's eye lenses are included in the optical system for image reconstruction, and his inherent ability of image recognition is also included in the data processing system.

It has been shown that an autostereosopic 3D television is possible either by the volume scanning method with optical sectioning in real time or by the projection method using a lens plate. The former method has not only an inherent disadvantage of phantom image problem, but also needs a high field-frequency necessary for flickerless observation. This requirement makes it difficult to match with the already well-developed 2D television system. The latter method needs a high quality 2D display device, which must have a large display area, high resolution, good chromaticity, high brightness, and high positional accuracy necessary for registration with a lens plate, although this method is superior to the former in the compatibility with the 2D television system. 1)

2D display devices having a matrix of tiny fixed-position display elements, such as liquid crystal, electroluminescent spot, plasma glow spot, fluorescent spot, or light -emitting diode, have the accuracy for registration with a lens plate. But, they have at the present moment neither the large display area nor the high resolution, both of which a Braun tube does have.

In this paper, an autostereoscopic television experiment, using a high-resolution Braun tube with beam indeces and lenticular sheets, is described. The positional accuracy of display has been improved by the newly devised "position-synchronized-read-out method". The precise image drawn on the fluorescent screen of the tube is displaced onto the back focal plane of a lenticular sheet by means of the other newly devised "modified relay-lens plate", 3) ~ 7)

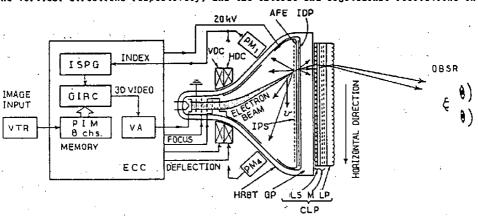

#### 2. Experiments

Figure 1 shows a simplified diagram of the experimental apparatus for displaying an autostereoscopic-3D-television image. HRBT is a high-resolution Braun tube with beam indeces(IPS), which are fluorescent stripes (with 50 µm width and 1mm pitch) printed on the thin aluminum electrode(AFE) at the back of the fluorescent screen(IDP). When IPS is hit by a dynamically focused electron beam (with 70 µm spot diameter and accelerated by 20kV), it emits a light pulse (in green), which is received by 4 photomultipliers(PM1-PM4) through windows of the glass envelope of the tube. After amplification and shaping, this index signal determines the timing (in ISPG) of the read-out pulses (~5.6MHz) and the interpolation timing signal(~45MHz). Both of them determine the exact timing of reading-out (in GIRC) pixels of 8 parallax images sequentially from the memory(PIM). Thus, 8 parallax images are interleaved in registration with IPS, and simultaneously displayed at the rate of 60 3D-images per sec. (525/2 interlaced horizontal scans per 1/60 sec.) 3D video bandwidth is 30MHz.

In Fig. 1. CLP is the composite lens plate, which consists of the modified relay-lens plate and the lenticular sheet (LP). Since the face plate (GP) of the tube is much thick - er than a lenticular sheet having a wide viewing zone, the image on IDP must be displaced onto the back surface of LP. The modified relay-lens plate consists of another lenticular sheet with a long-focal length and 7 masks, all of which are in registration with IPS, and it forms 8 line-images per pitch at the back of LP. These 8 line-images per lenslet of LP generate 8 fan beams. An observer at 0.7-1.5m in front of LP chooses arbitrarily two of those beams at a moment with his eye lenses, and then he recognizes naturally a 3D object in real time.

Figure 2 shows a photograph of the experimental Braun tube with the composite lens plate. Figure 3 shows stereo-pair photographs of a reconstructed 3D image of a plasticine statue. The parallax images of this 3D image were taken by a CCD camera with the object on a rotating table. The display area has 280mm and 220mm in the horizontal and vertical directions respectively, and the lateral and logitudinal resolutions in

Figure 1. Simplified diagram of autostereoscopic 3D television display

the vicinity of LP are 1mm and 16mm, respectively. The viewing zone has approximately 20cm width. The image brightness and the width of viewing zone can be improved if LP is contained in the tube's envelope.

Figure 2. Experimental Braun tube with the composite lens plate

### 3. Discussions

3.1 Stabilization of the index signal

When a high-resolution Braun tube with beam indeces is the device of displaying a 3D image, accurate read-out pulses must be generated even if 3D video signal is strongly amplitude-modulated.

Focusing and deflection-linearity of a Braun tube at the begining of a horizontal scan are generally poor, and the first index stripe is not always expected to be usable for determining the start pulse. Therefore, to generate the start pulse of displaying in each of horizontal scans, deflection linearity at the starting position of displaying must be adjusted within a certain tolerance, and an index stripe without defects along its full vertical length must be found out and be used.

Because 3D video signal having depth informations is deeply and quickly changing, it is necessary to superpose a video pulse with a constant amplitude for establishing the start pulse. And it is also necessary to use a phase-lock-loop(PLL) for stabilizing the read-out pulses for each of horizontal scans. Moreover, phase shift of index signal at amplification and PLL(in ISPG shown in Fig.1) must be minimized, since index pulses are not periodical at all. To reduce disturbances due of transient phenomena in ISPG, it is often effective to superpose short video pulses, which are synchronized with the read-out pulses and at the phase to hit the index stripes. These auxiliary

Figure 3. Stereo-pair of a 3D image reconstructed on the Braun tube

pulses are superposed on the 3D video channel in VA shown in Fig.1

#### 3.2 Autostereoscopic 3D television camera

Since television camera devices have resolution poorer than a high-resolution Braun tube, a necessary number of parallax images must be taken with many optically aligned cameras. CCD(charge-coupled-device) camera is one of the best for this purpose, because it is compact in size, and has positionally fixed photoelectronic-conversion elements with high sensitivity.

For adjusting magnification and distance, the same method as an autostereoscopic 3D camera is applicable. If a television camera with very high resolution become available, a single camera device with the same optics as the 3D camera would be usable. 2)

#### 4. Conclusions

It has been demonstrated that an autostereoscopic television display is done by using a high-resolution Braun tube with beam indeces.

Although stereoscopic television systems are already in market, many important subjects are left unsolved in the field of the autostereoscopic 3D television. Some of them are listed as follows:

- 1) Full color autostereoscopic television

- 2) Autostereoscopic television with a wide screen and high brightness

- 3) Frequency-band reduction of autostereoscopic television signal

- 4) Compatibility with the 2D television system, including apparatus for recording

- 5) Standardization of autostereoscopic television system

For future development of autostereoscopic television system, mutual colaboration between people in the fields of electronics, vision research, information processing and many application fields of 3D television is strongly needed.

Acknowledgements: Many thanks to people of Sony Co., Ltd., Toppan Printing Co., Ltd., and colleagues of the institute. This work was done with the coworkers listed in the references, and supported by Hoso-Bunka Foundation, and Ministry of Education and Culture of Japan.

References: - 1) J. Hamasaki: "Autostereoscopic 3D television experiments", AIP Conf. Proc. No. 65. Subseries on Opt. Sci. and Eng. No. 1: Optics in Four Dimensions; 531-556. AIP, 1981.

<sup>2)</sup> J. Hamasaki; "Three-dimensional photography and its applications". Proc. Int'l Symp. on Image processing and

its applications,:Progress in Image Processing:149-158.IIS.Univ.of Tokyo, 1984.

3) J.Hamasaki, S. Vematsu, O. Takeuchi, A. Okada, S. Utsunomiya; Direct display of 3D images by means of Braun tube: Proposal on Image-signal composition by position-synchronized-read-out ".Tech.Report ITEJ, VV 72-4 (IPA 78-4, IPD180-4). '85.10

<sup>4)</sup> M.Okada, J.Hamasaki, S.Utsunomiya, O.Takeuchi, K.Kanbayashi, S.Uematsu; "Righ precision Braun tube display device using position-synchronized-read-out method", Tech.Report ITEJ, ED'87-22(Vol.10, No. 54, 13-18), '87.3 5) J.Hamasaki, M.Okada, S.Utsunomiya, S.Uematsu, O.Takeuchi, K.Kanbayashi; "Direct display of 3D images by means of a high-resolution Braun tube with beam indeces", Tech.Report ITEJ, ED'87-23(Vol.10, No. 54, 19-24), '87.3

<sup>6)</sup> J. Hamasaki, M. Okada, S. Utsunomiya: "Improved display method of real-time 3D images using a high-resolution Braun tube with beam indeces: Analysis and experiments for high fidelity extraction of beam indees", Tech. Report ITEJ, VVI'87-15(Vol.11, No.1, 1-6), '87.5

<sup>7)</sup> S.Utsunomiya, J. Hamasaki, M. Okada: "Relay lens plate for displacement of real image plane in the depth direction: Experiments and barrier positions", Tech Report IECEJ, EID-18, '87.6

#### 3DTV WITHOUT GLASSES

#### Reinhard Börner

At Heinrich-Hertz-Institut in Berlin/West-Germany the author is developing 3-D-System for projection onto lenticular screens.

The diagonal of the large screen and the viewing distance are of about the same length in order to obtain a most natural impression of presented space and objects.

Using sidelobes of parallax panoramagrams for projection, the distance between the projectors (e.g. 6 projectors for 5 stereopairs) is no longer limited to the spacing of the observer's eyes. Therefore no special projectors are required; customary projection equipment for slides and video may be used. On the other hand, the selectivity of a wide-angle lenticular screen has to be increased enormously to minimize crosstalk in the outer panorama zones. This was achieved by a certain arrangement of the projectors, and by a new type of optical

of the screen and throughout all viewing-zones. The photographic projection equipment was introduced for the first time at Funkausstellung in Berlin 1986 and in addition a monocromatic recording- and projection system at HDTV-Kongreß in München 1987. This equipment will be explained and some aspects of future application to video camera and projection system will be discussed.

correction with increased selectivity across the whole area

6. コンピュータ分科会アブストラクト

#### 6. コンピュータ分科会アブストラクト

#### Data Base Machine Architectures

H. O. Leilich

#### Abstract: