# 第5世代のコンピュータ

データフローマシン/データベースマシンの調査研究

昭和57年2月

財団法人日本情報処理開発協会社団法人日本電子工業振興協会

この報告書は、日本自転車振興会から競輪収益の一部である機械工業振興資金の補助を受けて昭和56年度に実施した「第5世代電子計算機に関する内外技術動向調査」の成果をとりまとめたものであります。

# 序文

この報告書は、財団法人 日本情報処理開発協会からの委託により、社団法人 日本電子工業振興協会が昭和56年度事業として実施した「第5世代コンピュータ基幹技術に関する調査研究」のうち「データフローマシン/データベースマシンの調査研究」の結果をとりまとめたものである。

この調査は、1990年代に実用化を目標とした第5世代コンピュータの基幹技術であるデータフローマシン/データベースマシンについて、各バイロットシステムの基本設計に必要な基礎データの収集分析ならびに開発のための基本システムをとりまとめたものであり、「技術調査委員会」(委員長東京大学工学部電気工学科助教授 田中英彦氏)を設置して実施した。

調査の実施にあたり、ご指導、ご協力いただいた関係官庁、関係各位ならびに直接労を賜わった委員各位に深く感謝の意を表わすとともに、この報告書が有益に活用いただければ幸いである。

昭和57年2月

#### 〈本調査で作成した報告書・資料〉

- 第5世代のコンピュータ研究開発計画

- リ ボータフローマシン/データベースマシン

- リ ロジックプログラミング

- " " 波及効果

- " 関連技術動向調査

- " 研究開発計画・付属資料

# データフローマシン/データベースマシン技術調査委員会

(敬称略 順不同)

| 委員長 | 田  | 中    | 英 | 彦 | 東京大学           | 工学部電気工学科 助教授                          |

|-----|----|------|---|---|----------------|---------------------------------------|

| 委 員 | 雨  | 宮    | 真 | Д | 電電公社武蔵野電気通信研究所 | 基礎研究部第一研究室 調査役                        |

| "   | 田  | 中    |   | 譲 | 北海道大学          | 工学部電気工学科 講師                           |

| "   | 山  | 本    | 昌 | 弘 | 日本電気(株)        | C&Cシステム研究所<br>コンピュータシステム研究所           |

| "   | 門  | 脇    | 吉 | 彦 | (株)日立製作所       | 神奈川工場CPU設計部主任技師                       |

| "   | 淹  | 沢    |   | 誠 | (財)日本情報処理開発協会  | 開発部 係長                                |

| "   | 相  | 馬    | 行 | 雄 | (株)富士通研究所      | システム研究所 主任研究員                         |

| "   | 伊  | 藤    | 徳 | 義 | 沖電気工業(株)       | 総合システム研究所通信処理研究部<br>コンピュータアーキテクチャ 研究室 |

| "   | 竹  | 内    | 彰 | _ | 三菱電機(株)        | 中央研究所システム第 2 グループ                     |

| "   | 島  | 田    | 俊 | 夫 | 電子技術総合研究所      | 電子計算機部計算機方式研究室                        |

| "   | 喜連 | ējij |   | 優 | 東京大学           | 工学部電気工学科                              |

| M.  | 後  | 藤    | 厚 | 宏 | 東京大学           | 工学部電気工学科                              |

| "   | 宫  | 地    | 泰 | 造 | 三菱電機(株)        | 情報電子研究所情報処理開発部<br>ソフトウェアグループ          |

| "   | 来  | 住    | 晶 | 介 | 沖電気工業(株)       | 総合システム研究所通信処理研究所<br>コンピュータアーキテクチャ 研究室 |

| 協力者 | 長名 | 11(4 | 隆 | 三 | 電電公社武蔵野電気通信研究所 | 基礎研究部第一研究室調查員                         |

| 事務局 | 菊  | 池    |   | 瑛 | (社)日本電子工業振興協会  | 開発部 部長代理                              |

| "   | 清  |      | 紹 | 英 | (社)日本電子工業振興協会  | 電子計算機担当 課長代理                          |

| "   | 小  | 島    | 謙 | = | (社)日本電子工業振興協会  | 電子計算機担当                               |

## はじめに

本報告書は、昭和56年7月、(財)日本情報処理開発協会から(社)日本電子工業振興会へ委託された「データフローマシン/データベースマシンに関する調査研究」の報告書である。

この委託調査は、昭和57年度から始められる第5世代コンピュータプロジェクトに反映するための研究開発計画の基礎調査として進められたもので、第5世代コンピュータンステムの基幹技術に関する先行研究の1つとして位置付けられる。

第5世代コンピュータシステへの目的は、知識情報処理システムを実現することである。人間が、 過去に蓄積した膨大な知識と基にして新しい局面に対応し、またその経験を新しい知識として蓄え てゆくように、コンピュータにも同様の能力を持たせようというのである。これによって、従来のコ ンピュータで問題とされて来た多くの難点を克服することが期待されている。

このようなコンピュータは、膨大な知識を能率良く蓄え必要に応じて取り出す機能と、取り出した 知識を活用して推論を行う機能とからなると考えられる。前者は知識ベースマシン、後者は推論マシンと呼ばれているがこれらのマシンを支える基本的なハードウェア機構は何であろうか。それは現代のコンピュータの延長線上にあるものであろうか、それとも全く異なった新しいものであろうか、これらの問いに対し、今完全な答えが用意されている訳ではない。それは今後の研究が進むにつれてより明確になってゆくべき性格のものである。しかし、この基本機構として今最も有望視されているもの、若しくは将来の基本機構の礎となる可能性が高いものを抽出することはできる。それは、関係データベースマシンと、データフローマシンである。関係データベースマシンは知識ベースマシンの基礎であり、データフローマシンは並列度の高い推論処理の基本機構であると考えられる。

本調査研究は、とのようなデータフローマシンとデータベースマシンを対象とし、それらの検討を 行うことを目的とする。具体的には、われわれはこの調査研究の目的を次のように設定し作業を進め ることとした。

- 1. これら両マシン研究の現状分析

- 2. 両マシンの諸技術の検討と整理

- 3. マシン実現上の問題点の抽出

- 4. 実現諸技術の提案

- 5. ブロトタイプマシンのイメージ作成

- 6. 実験機第1版の仕様作成

- 7. 前期研究開発作業計画の立案

### 8. 研究開発用人員の推定, 支援環境の明確化

調査研究に携わった者とその役目分担は以下に示す通りである。

田中英彦主査

雨 宮 真 人 DFMグループリーダ

田中 譲 DBMグループリーダ

山 本 昌 弘 DBMグループ

門 脇 吉 彦 DBMグループ

滝 沢 誠 DBMグループ

相馬行雄 DFMグループ

伊藤徳義 DFMグループ

竹 内 彰 一 **DFM**グループ

島 田 俊 夫 DFMグループ

喜連川優 DBMグループ

後 藤 厚 弘 DFMグループ

宮 地 泰 造 DBMグループ書記

来 住 晶 介 DFMグループ書記

長谷川 隆 三 DFMグループ・協力者

清 超英 事務局

以上の他、電総研の植村俊亮氏、日本電気の日吉茂樹氏、富士通の牧之内顕文の各氏には、 との調査研究の初期段階でのヒアリングに御脇力いただき貴重な御意見をたまわった。

この調査研究委員会は、昭和56年7月末より、昭和57年2月まで、ほぼ6カ月足らずの間、月2回程のペースで作業を進めた。始めてから10月の始めまでは、この作業の目的をしぼり、両マシンの研究現状についての認識を深めて検討を必要とする項目をしぼり込むことを行った。この間は、全員集まって作業を進めた。11月から2月の始めまでは、両マシンの技術検討、プロトタイプのイメージ作り、研究開発計画の立案等を行ったが、作業の時間を多くする意味から、データフローマシン、データペースマシンのグループに分かれ並行して作業を行った。何回かの会合は時間を多く取り、まる1日を費している。これらの並行作業では各グループリーダがまとめ役となり検討を進めた。主査は両グループに参加した。毎回の検討会では常に全員が作業結果を持ち寄って相互に検討し合い、次回までの宿題を持ち帰るというパターンで進めたため、実際に要した全時間はかなりになるであろう。

このようにして進めた検討の成果がこの報告書である。なにぶんにも短期間で作業を行ったため、細かな諸点に検討洩れの箇所や、検討不十分な点が見受けられることは否めない。しかし、この検討に携わった者はそれぞれの立場における忙しさにもかかわらず皆非常に熱心に作業を行った。この報告書が将来のコンピュータ技術の研究に役立てば幸いである。

## はじめに

| 第 1 部 | 3 デ・ | ータフ  | ローマシンの研究                                         | 1  |

|-------|------|------|--------------------------------------------------|----|

| 1     | . 概  | 要    | ······                                           | 3  |

| 2     | . デ  | ータフ  | ローマシン研究の背景と意義                                    | 7  |

|       | 2.1  | 知識   | 情報処理からの要請                                        | 7  |

|       | 2. 2 | デー   | タフローマシンの目的と意義                                    | ç  |

|       | 2. 3 | 計算   | モデルとデータフローマシン                                    | 17 |

| 3     | . デ  | - タフ | ローマシン研究の現状                                       | 16 |

|       | 3.1  | デー   | タフローマシン用言語の研究                                    | 16 |

|       | 3. 3 | l. I | I d                                              | 16 |

|       | 3. : | l. 2 | VALID                                            | 19 |

|       | 3. : | 1.4  | VAL                                              | 21 |

|       | 3. 1 | 1. 5 | CAJOLE                                           | 24 |

|       | 3. 2 | デー   | タフローマシンの研究開発の現状                                  | 26 |

|       | 3. 2 | 2. 1 | Dennis (MIT) マシン                                 | 26 |

|       | 3. 3 | 2.2  | Arvind (MIT)マシン                                  | 29 |

|       | 3. 2 | 2. 3 | Rumbaugh マシン ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 32 |

|       | 3. 2 | 2. 4 | LAU システム ······                                  | 34 |

|       | 3.2  | 2. 5 | DDM1(Utah大学)                                     | 35 |

|       | 3. 2 | 2. 6 | Manchester 大学のデータフローマシン                          | 38 |

|       | 3. 2 | 2. 7 | Keller マシン ······                                | 41 |

|       | 3. 2 | 2. 8 | TOPSTAR (東京大学)                                   | 43 |

|       | 3. 2 | 2. 9 | D <sup>3</sup> C (東京大学)                          | 47 |

|       | 3.2  | . 10 | D <sup>3</sup> P ( 沖電気工業 )                       | 50 |

|       | 3.2  | .11  | 東北大学のデータフローマシン                                   | 52 |

|       | 3.2  | .12  | Passive Memoryless Architecture                  | 54 |

|       | 3.2  | .13  | 富士通のデャタフローマシン                                    | 56 |

|       | 2.0  | 1.4  | <b>売終 種の ニュタフロー・ハハ</b>                           |    |

| 3.2.15 通研のデータフローマシン                                                | 60   |

|--------------------------------------------------------------------|------|

| 3.3 リダクションマシンの研究開発の現状                                              | 64   |

| 3.3.1 Berkling のマシン                                                | 64   |

| 3.3.2 Tre leavenのリダクションマシン                                         | 67   |

| 3.3.3 Mago のリダクションマシン                                              | 70   |

| 3.3.4 日本電気のリダクションマシン                                               | 72   |

| 3.3.5 ALICE                                                        | 74   |

| 4. データフローマシンの実現技術の検討                                               | 78   |

| 4.1 データフローマシンの検討項目                                                 | 78   |

| 4.2 データフローマシン用高級言語とその評価                                            | 79   |

| 4.2.1 従来型言語の問題点                                                    | 79   |

| 4.2.2 関数型プログラミングとデータフローマシン                                         | 80   |

| 4.2.3 論理型プログラミングとデータフローマシン                                         | 83   |

| 4.2.4 履歴依存性                                                        | 85   |

| 4.2.5 既存データフローマシン用高級言語の総括                                          | 86   |

| 4.2.6 非决定性処理                                                       | 89   |

| 4.2.7 計算モデル                                                        | 90   |

| 4.3 データフローマシンの制御方式と機能要素                                            | 95   |

| 4.3.1 計算機構                                                         | 95   |

| 4.3.2 データフローマシンの制御方式                                               | 96   |

| 4.3.3 リダクションマシンの制御方式                                               | 99   |

| 4.3.4 データフローマシンとリダクションマシンの特徴比較                                     |      |

| 4.3.5 非決定的処理の制御                                                    |      |

| 4.3.6 命令セット                                                        |      |

| 4.4 構造メモリ                                                          | 116  |

| 4.4.1 データフローマシンにおけるデータ構造操作と構造メモリの目的                                | 116  |

| 4.4.2 構造データメモリの機能                                                  |      |

| 4.4.3 構造メモリの現状                                                     |      |

| 4.4.4 構造メモリの実現方式の検討                                                |      |

| 4.5 ネットワークとアクティビティ割り付け                                             | 145  |

| 451 データファーマシング かけるネットワークとその役割 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 1.45 |

| 4.5.2 ネットワーク技術の現状     | 147          |

|-----------------------|--------------|

| 4.5.3 アクティビティ割り付付     | 151          |

| 4.5.4 アクティビティ割り付け制御方式 | 1 52         |

| 4.6 入 出 力             | 1 <b>5</b> 6 |

| 4.6.1 入出力処理形態         | 156          |

| 4.6.2 入出力装置接続形態       | 159          |

| 4.6.3 チャネルと割込み        | 160          |

| 4.6.4 入出力と並列性         | 161          |

| 4.6.5 入出力動作と基本命令      | 162          |

| 4.7 データフローマシンの実装法     | 165          |

| 4.7.1 全体構成            | 165          |

| 4.7.2 モジュール間インタフェース   | 167          |

| 4.7.3 サービスプロセッサの実装    | 168          |

| 4.7.4 スループットと問題の並列度   | 168          |

| 4.7.5 VLSI技術の導入       | 169          |

| 4.7.6 データフローマシンのVLSI化 | 170          |

| 4.7.7 ネットワークの実装       | 171          |

| 4.8 制御ソフトウェア          | 173          |

| 4.8.1 プログラムの起動        | 173          |

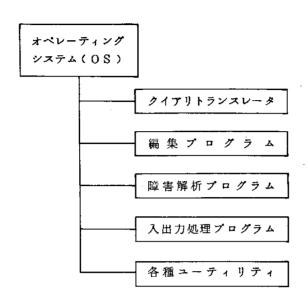

| 4.8.2 データフローマシンのOS    | 175          |

| 4.9 信頼性処理             | 178          |

| 4.9.1 冗長化方式           | 178          |

| 4.9.2 故障検出            | 179          |

| 4.9.3 リカベリ            | 185          |

| 4.10 デバッグ機能           | 188          |

| 4.10.1 ソフトウェアデバッグ用の機能 | 188          |

| 4.10.2 ハードウェアデバッグ用の機能 | 190          |

| 5. データフローマシン実験機のイメージ  | 1 91         |

| 5.1 実験機第1版のイメージ       | 191          |

| 5.1.1 実験機第1版の位置付け     | 191          |

| 5.1.2 データフローマシン用京級言語  | 192          |

| 5.1.3 アーキテクチャ        | 196 |

|----------------------|-----|

| 5.1.4 制御方式と命令セット     | 206 |

| 5.1.5 オペレーティングシステム   | 212 |

| 5.1.6 実装法と目標性能       | 214 |

| 5.2 実験機第2版のイメージ      | 216 |

| 5.2.1 高級言語           | 216 |

| 5. 2. 2 OS ·····     | 216 |

| 5.2.3 ハードウェア         | 216 |

| 5. 2. 4  信頼性技術       | 217 |

| 5.2.5 ネットワーク         | 217 |

| 5.2.6 実装法            | 217 |

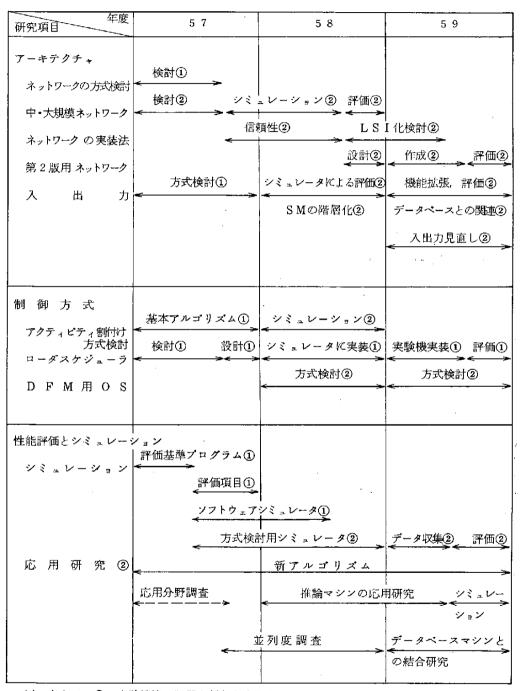

| 6. 研究開発内容            | 219 |

| 6.1 研究課題             | 219 |

| 6.1.1 基礎研究           | 219 |

| 6.1.2 高級言語           | 221 |

| 6. 1. 3 応用研究         | 222 |

| 6.1.4 アーキテクチャ        | 224 |

| 6.1.5 制御ソフトウェア       | 230 |

| 6.1.6 実装法            | 231 |

| 6.2 研究プロジェクトの構成      | 232 |

| 6.3 研究プロジェクトの内容      | 234 |

| 6.3.1 データフローマシンの理論研究 | 234 |

| 6.3.2 高級言語の研究        | 236 |

| 6.3.3 アーキテクチャの研究     | 237 |

| 6.3.4 制御方式の研究        | 246 |

| 6.3.5 実験機の開発         | 248 |

| 6.3.6 性能評価とシミュレーション  | 251 |

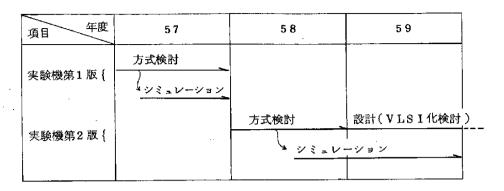

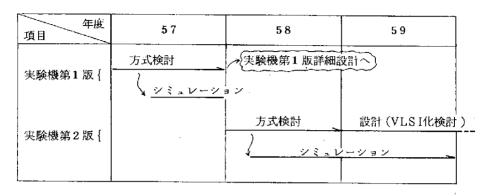

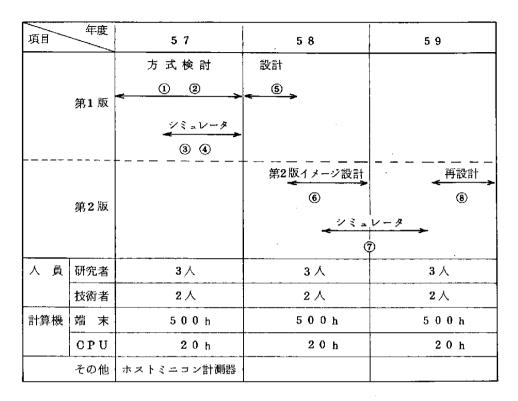

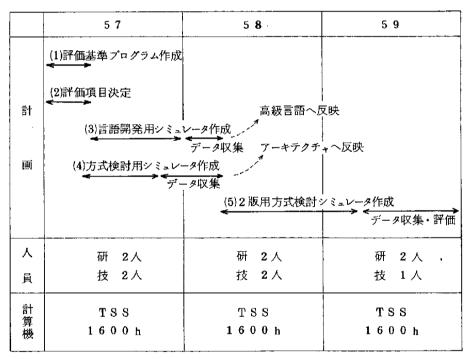

| 7. 研究開発計画と体制         | 256 |

| 7.1 研究開発のタイムスケジュール   | 256 |

| 7.2 研究開発体制           | 256 |

| 7.2.1 ソフトウェア開発支援環境   | 256 |

•

| 7.2.2 ハードウェア開発環境         | 257 |

|--------------------------|-----|

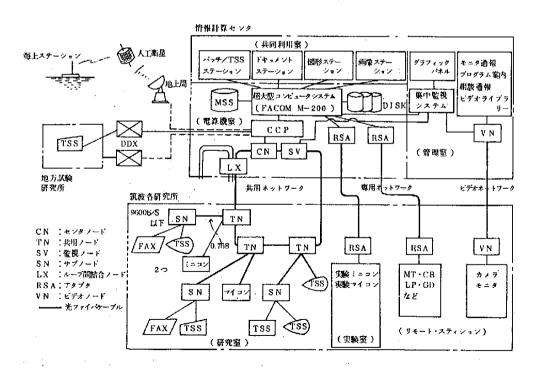

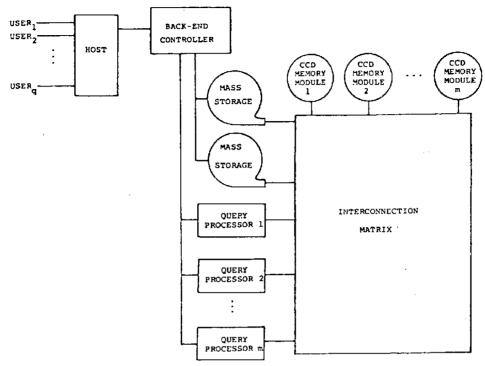

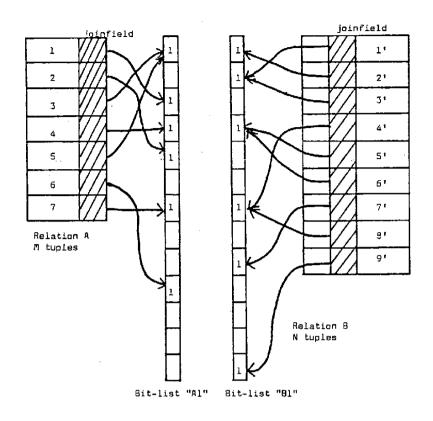

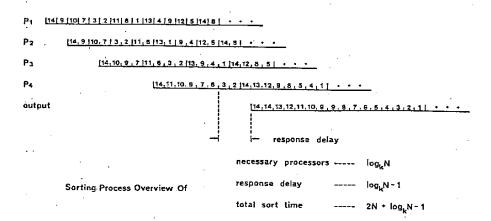

| 第 2 部 データベースマシンの研究       | 263 |

| 1. 概 要                   |     |

| 1.1 背景と意義                | 263 |

| 1. 1. 1 データベース応用の拡大      |     |

| 1.1.2 知識情報処理におけるデータベース   |     |

| 1. 1. 3 データベースマシン開発の必要性  |     |

| 1.2 FGCSプロジェクトにおける位置づけ   |     |

| 1.3 機能と性能に対する要求          | 266 |

| 1.3.1 現状のデータベースマシンの問題点   | 266 |

| 1.3.2 機能に対する要求           | 266 |

| 1.3.3 性能に対する要求           | 267 |

| 1.4 開発目標とマシンのイメージ        | 268 |

| 1.4.1 開発目標               | 268 |

| 1.4.2 マシンのイメージ           | 268 |

| 2. 背景と意義                 | 273 |

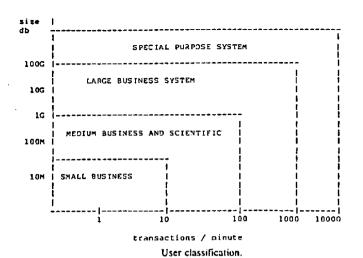

| 2.1 データペース応用の拡大          | 274 |

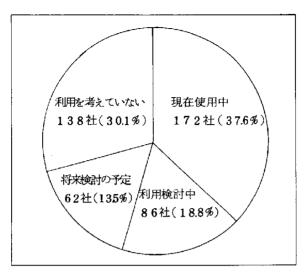

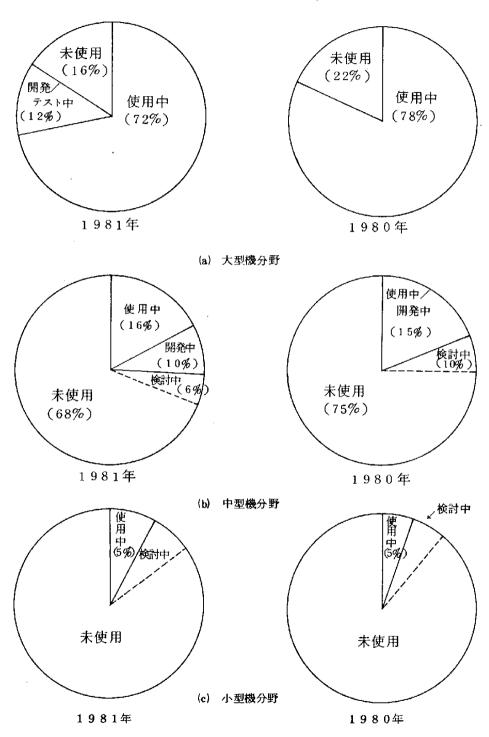

| 2.1.1 データベース応用の現状        | 274 |

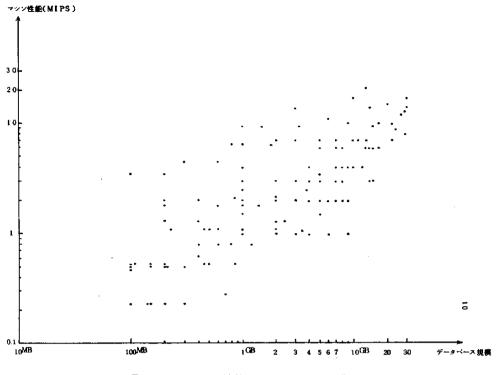

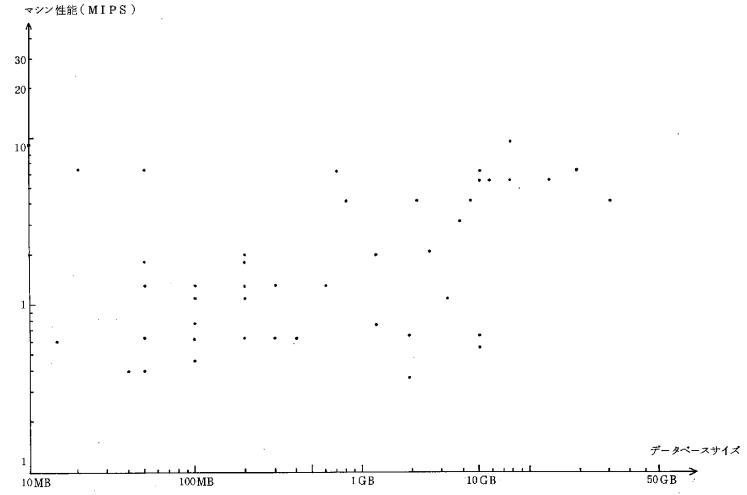

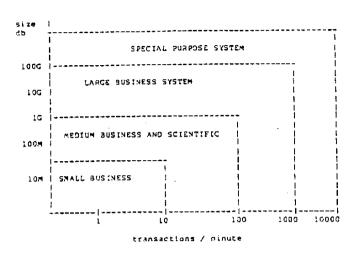

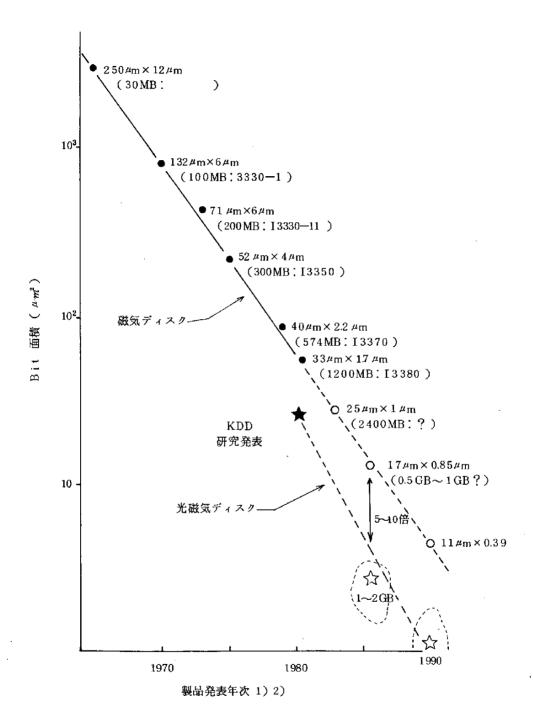

| 2.1.2 データベース規模           | 278 |

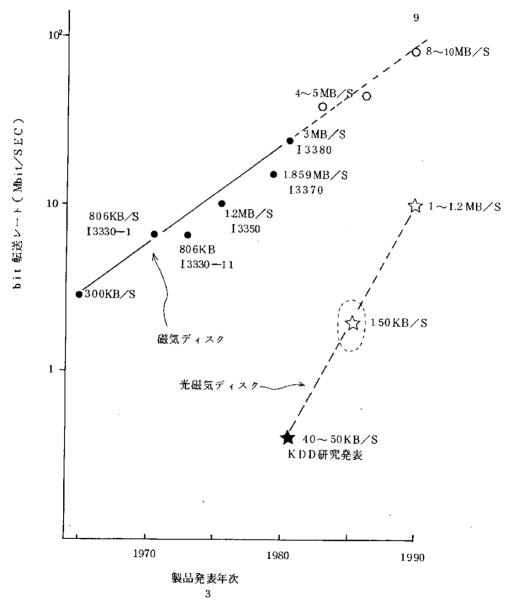

| 2.1.3 処理速度               | 279 |

| 2. 1. 4 データベース応用分野の拡大    | 281 |

| 2.2 データペースシステムの現状と将来     | 283 |

| 2.2.1 問題点                | 283 |

| 2.2.2 データベースシステムの機能      | 285 |

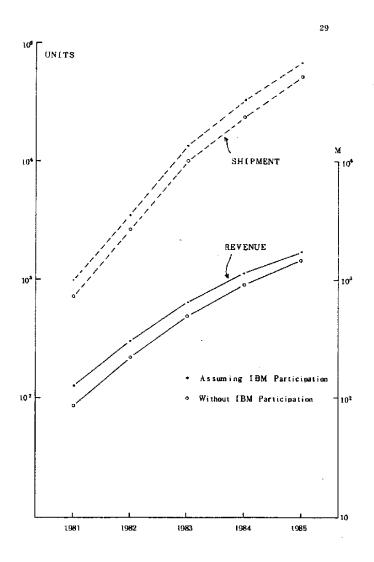

| 2.2.3 データペースマシンの必要性と市場予測 | 286 |

| 2.3 知識情報処理におけるデータベース     | 289 |

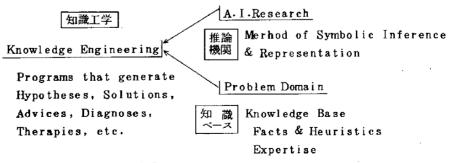

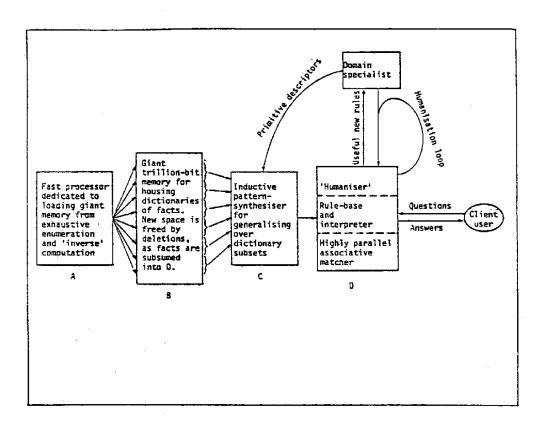

| . 2.3.1 専門家システムとデータベース   | 289 |

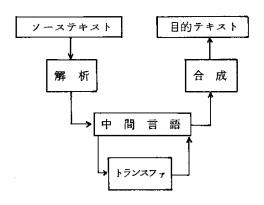

| 2.3.2 言語翻訳システム           | 294 |

| 2.3.3 知識工学が必要とするデータベース   | 296 |

| 2.4 データベースマシン開発の社会的要請    | 301 |

| 3. データベースマシン研究開発の現状                    | *************************               | 303         |

|----------------------------------------|-----------------------------------------|-------------|

| 3.1 データベースマシンの分類                       |                                         | 303         |

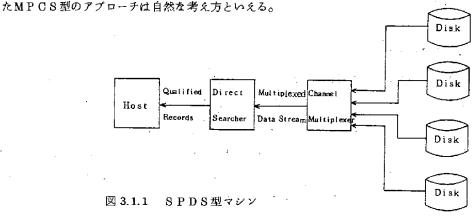

| 3.1.1 SPIS型マシン                         |                                         | 304         |

| 3.1.2 SPDS型マシン                         |                                         | 304         |

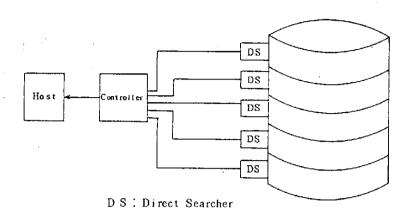

| 3.1.3 MPDS型マシン                         | ••••••••••••••••••••••••••••••••••••••• | 305         |

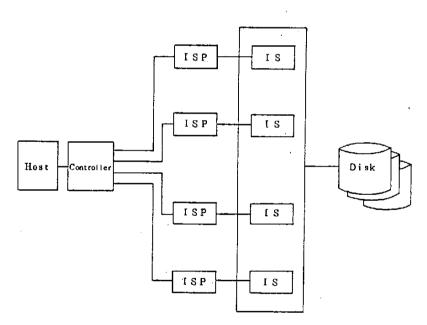

| 3.1.4 MPIS型マシン                         |                                         | 305         |

| 3.1.5 MPCS型マシン                         |                                         | 306         |

| 3.2 データペースマシンのアプリケーション依存性              | *************************************** | 308         |

| 3.2.1 Bibliographic Search             | •••••••••••                             | 308         |

| 3.2.2 Bussiness Application            |                                         | 309         |

| 3.2.3 Statistical Analysis Application |                                         | 309         |

| 3.2.4 結 論                              |                                         | 310         |

| 3 3 代表的なマシンの定量的評価                      |                                         | 311         |

| 3 3 1 各マシンの特長                          |                                         | 311         |

| 3.3.2 各種バラメータの設定                       |                                         | 312         |

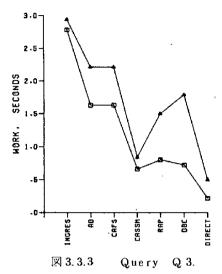

| 3.3.3 各種問い合わせに対するマシンの性能評価              |                                         | 314         |

| 3.3.4 結 論                              |                                         | 319         |

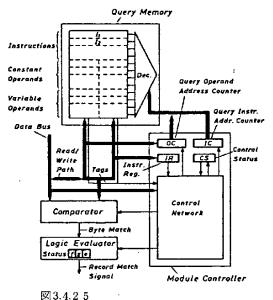

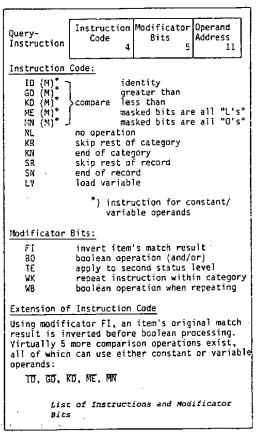

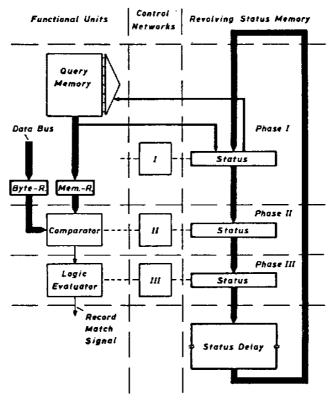

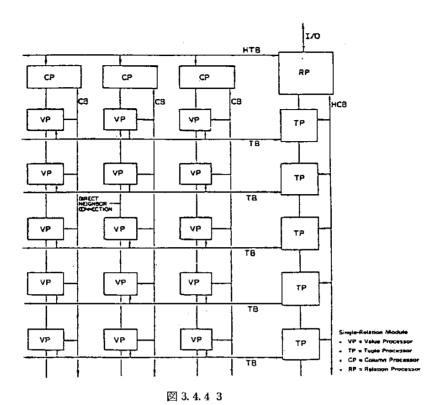

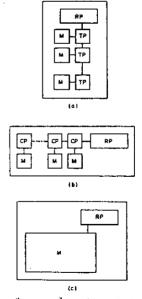

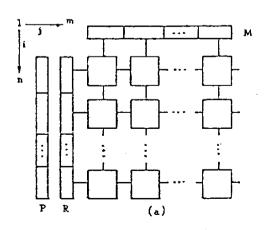

| 3.4 各種データベースマシンとその特徴                   |                                         | 321         |

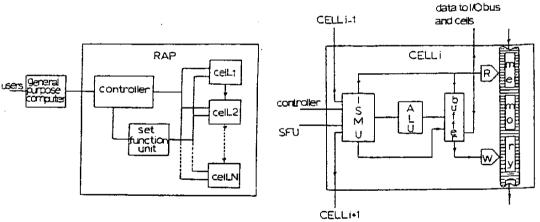

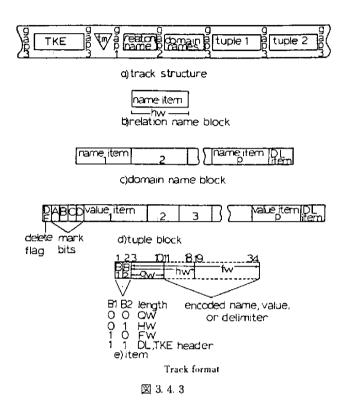

| 3. 4. 1 RAP                            |                                         | 322         |

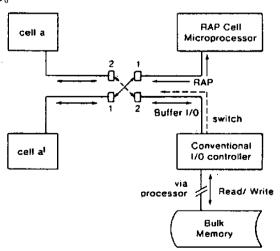

| 3. 4. 2 RAP3                           |                                         | <b>3</b> 26 |

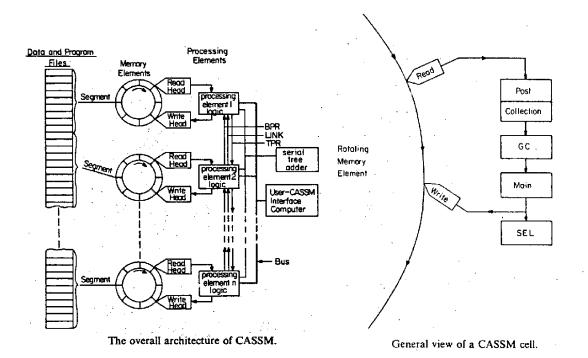

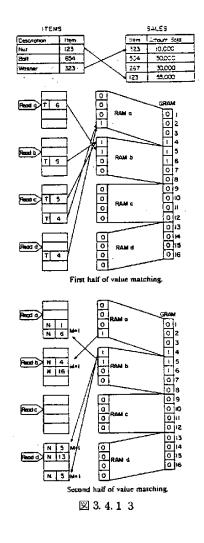

| 3.4.3 CASSM                            |                                         | 328         |

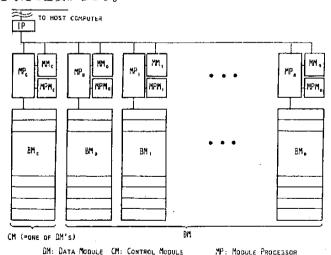

| 3. 4. 4 E D C                          |                                         | 330         |

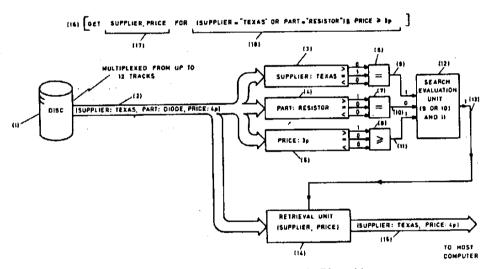

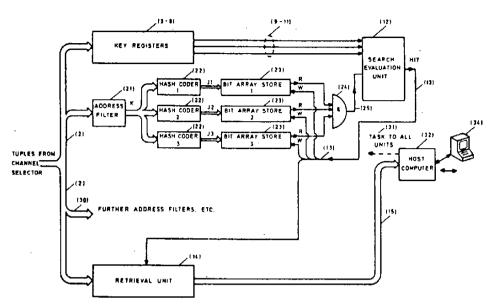

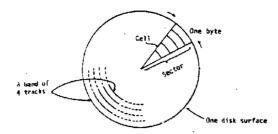

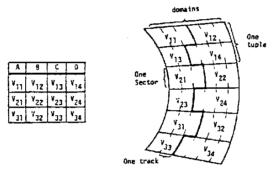

| 3.4.5 CAFS                             |                                         | 332         |

| 3.4.6 RARES                            |                                         | 334         |

| 3.4.7 サーチプロセッサ                         |                                         | 337         |

| 3.4.8 I DM 5 0 0                       |                                         | 340         |

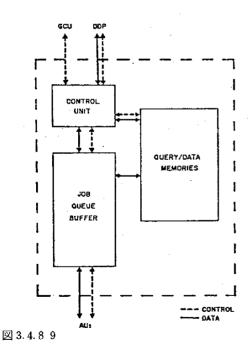

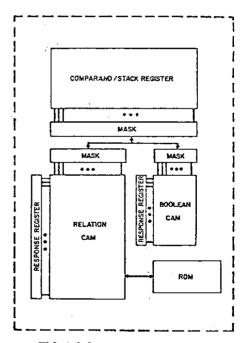

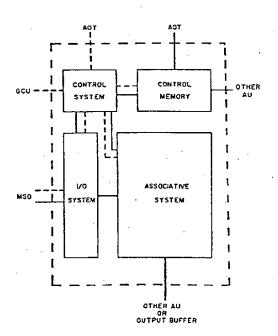

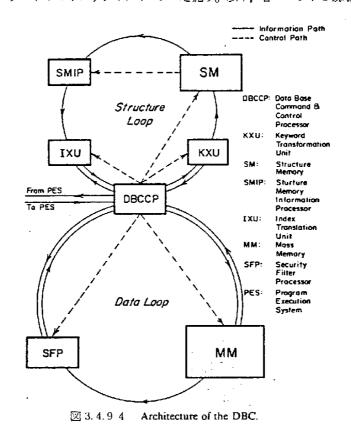

| 3.4.9 データコンピュータ                        |                                         | 341         |

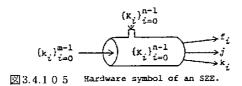

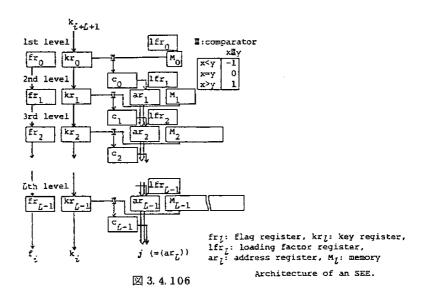

| 3.4.10 シストリックアレイを用いた関係データベースマシン        | *************************************** | 344         |

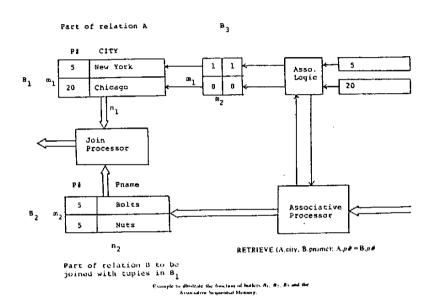

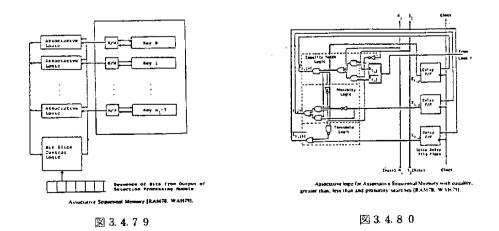

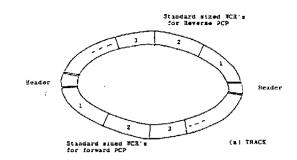

| 3.4.11 DBCジョインプロセッサ                    |                                         | 349         |

| 3.4.12 SRM ·····                       |                                         | 352         |

| 3.4.13 セルラアレイを用いたソートおよびプロジェクション        | *************************************** | 355         |

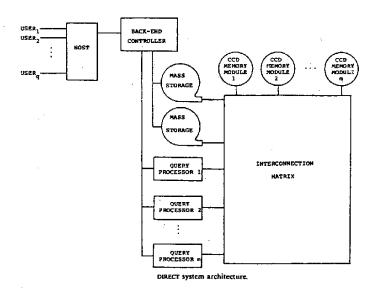

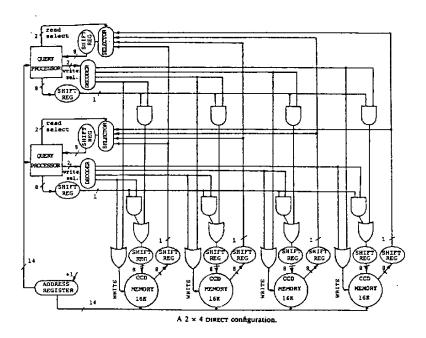

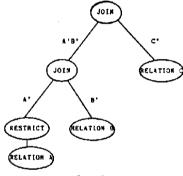

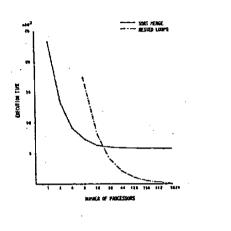

| 3.4.14 DIRECT                         | 357  |

|---------------------------------------|------|

| 3.4.15 Data Flow DIRECT               | 362  |

| 3.4.16 Highly Concurrent Tree Machine | 365  |

| 3.4.17 MICRONET                       | 370  |

| 3.4.18 DIALOG                         | 374  |

| 3.4.19 WCRC                           | 378  |

| 3.4.20 RELACS                         | 3 82 |

| 3.4.21 DBC                            | 386  |

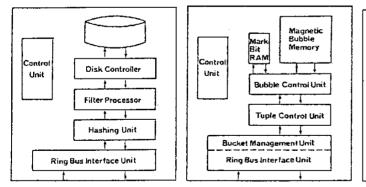

| 3.4.22 改良型磁気パプルメモリを用いたデータペースマシン       | 391  |

| 3.4.23 XDMS                           | 394  |

| 3.4.24 データフローデータペースコンピュータ             | 396  |

| 3.4.25 GRACE                          | 400  |

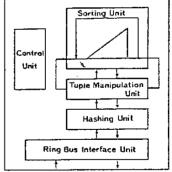

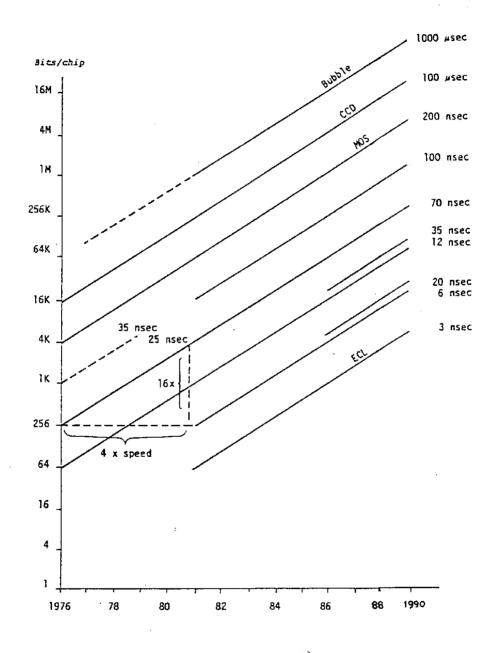

| 4. 実現技術                               | 408  |

| 4.1 ハードウェア                            | 408  |

| 4.1.1 素子技術                            | 408  |

| 4.1.2 大容量化技術                          | 414  |

| 4.1.3 大容量化技術の実際例                      | 419  |

| 4.1.4 モジュール間の各種結合方式とその評価              | 423  |

| 4.2 アーキテクチャ                           | 429  |

| 4.2.1 並列処理,パイプライン処理技術                 | 429  |

| 4.2.2 新アーキテクチャ                        | 432  |

| 4.2.3 各種処理技法とその評価                     | 434  |

| 4.3 ソフトウェア                            | 451  |

| 4.3.1 マルチユーザの支援技法                     | 451  |

| 4.3.2 柔軟性に関する技法                       | 453  |

| 4.3.3 RASIS                           | 453  |

| 4.3.4 高水準言語インタフェース                    | 457  |

| 4.3.5 分散データペースシステム関連技術                | 457  |

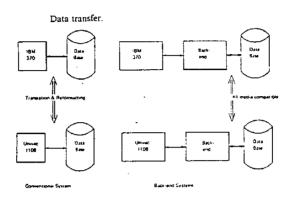

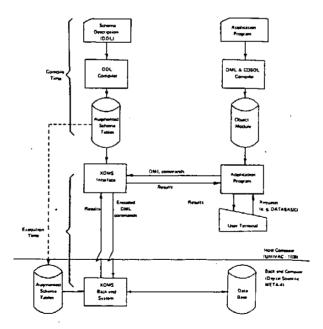

| 4.3.6 ホストとのインタフェース                    | 466  |

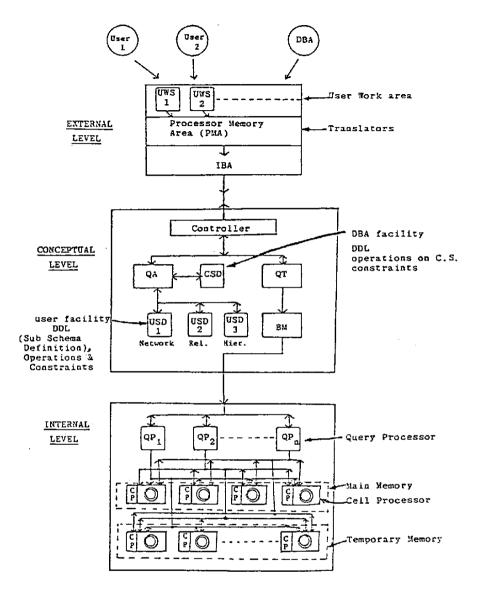

| 5. プロトタイプデータペースマシンの概要                 | 470  |

| 5.1 システムイメージ                          | 470  |

|                                       |      |

| 5. 1. 1 基本構造                                    | 470         |

|-------------------------------------------------|-------------|

| 5.1.2 種々の考え方                                    | 470         |

| 5.1.3 プロトタイプマシンのイメージ                            | 471         |

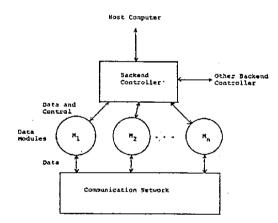

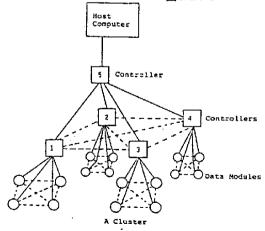

| 5.2 アーキテクチャ                                     | 473         |

| 5.2.1 はじめに                                      | 473         |

| 5.2.2 処理方式                                      | 474         |

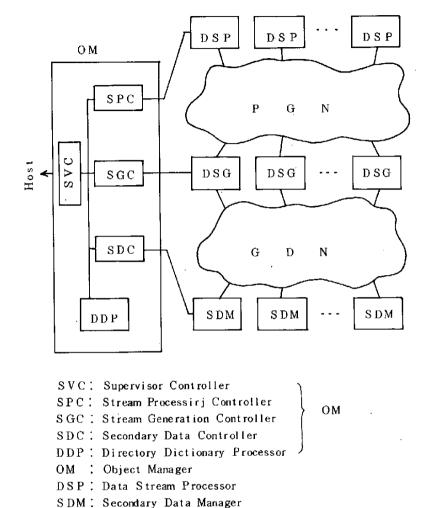

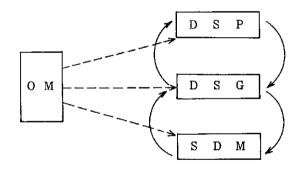

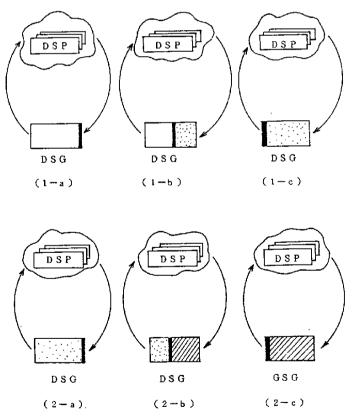

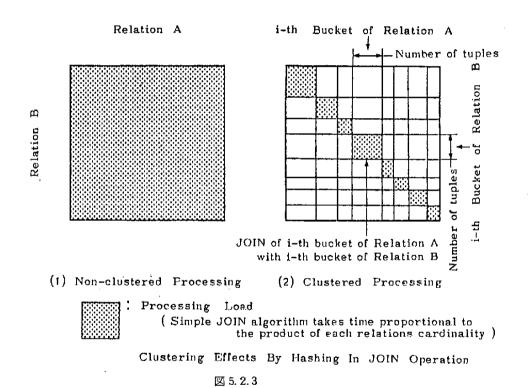

| 5.2.3 アーキテクチャ                                   | 484         |

| 5.3 ソフトウェア ···································· | 497         |

| 5.3.1 基本ソフトウェアシステム                              | 497         |

| 5. 3. 2 データベース管理ソフトウェア                          | 498         |

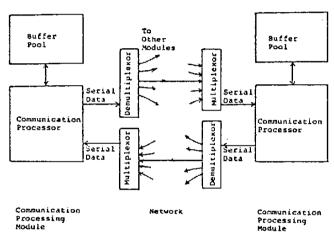

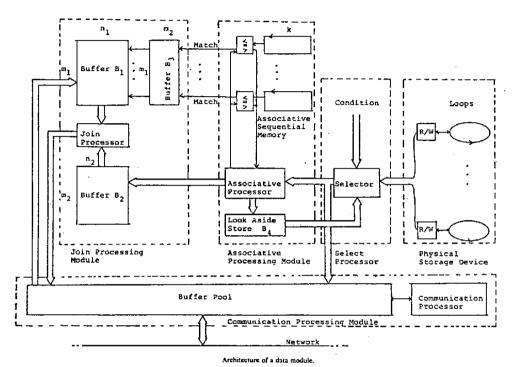

| 5.4 機能モジュール                                     | 502         |

| 5.4.1 関係代数演算処理モジュール                             | 502         |

| 5.4.2 結合ネットワーク                                  | 50 <b>5</b> |

| 5.4.3 2次記憶モジュール                                 | 505         |

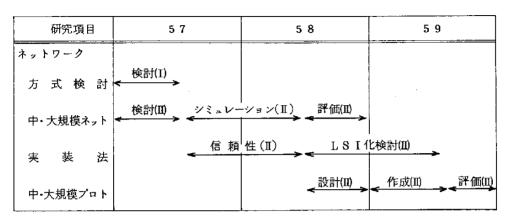

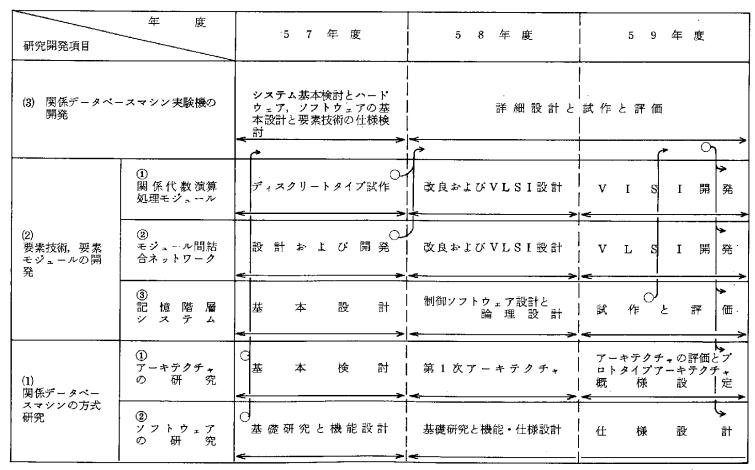

| 6. 研究開発内容と開発計画                                  | 509         |

| 6.1 関係データペースマシンの方式研究                            | 509         |

| 6.1.1 関係データベースマシンのアーキテクチャ研究                     | 509         |

| 6.1.2 関係データベースマシンのソフトウェア研究                      | 516         |

| 6.2 要素技術の開発と要素モジュールの開発                          | 522         |

| 6.2.1 関係代数演算処理モジュール                             | 522         |

| 6.2.2 結合ネットワーク                                  | 526         |

| 6.2.3 記憶階層システムの開発                               | 527         |

| 6.3 関係データベースマシン実験機の開発                           | 533         |

| 6.3.1 実験機設計と開発                                  | 533         |

| 6.3.2 シミュレーション                                  | 557         |

| 7. 研究開発計画と体制                                    | 560         |

| 7.1 研究開発計画の相互関連                                 | 560         |

| 7.2 研究開発体制                                      | 560         |

# 第 I 部 データフローマシンの研究

## 1. 概 要

知識情報処理システムにおける重要な機能の1つは推論機能である。これは、膨大な知識の中から関連のありそうな知識を見出すためのパターンマッチ機能としての統合化機能と、推論を進めて行く上で立てた仮説の失敗にもとづく自動的な後戻り機能を特徴とする。従って最終結論に夢り着くまでに、多くの試行錯誤を繰返しており、複雑な推論を実行するには一般に非常に多くの処理を必要とする。また、その処理は非決定的であり前似って定め難い。このような処理を従来のコンピュータの上で実行するとその逐次性の故に多くの時間を必要とし、また制御の記述が複雑になる。しかし、処理自体は本質的に多くの並列性を含んでおり、それらをハードウェアの都合上直列に実行することは、そのための制御を複雑にし処理速度を遅くこそすれ、何ら本質的なことではない。このような処理に向いた計算機構、それがデータフローマシンである。

データフローマシンは、データの依存関係による自然な操作の流れを基としており、関数型言語が その基本と考えられるので、プログラム作成上プログラマに与える負担が軽減され、ソフトウェア生 産性を向上できる可能性もある。

本検討グループは、このようなデータフローマシンを実現するための基礎検討を行うことを目的とする。すなわち、データフローマシンの諸技術を整理して問題点を明らかにすること、それらの問題点を検討し幾つかの解決策若しくはそれを見出すための手順を示して研究計画を立てること、出来れば目指すべきデータフローマシンのプロトタイプイメージを示し、それに至るための実験機第1版の仕様を固めること、またそのための研究開発用人員、支援環境を推定すること等である。

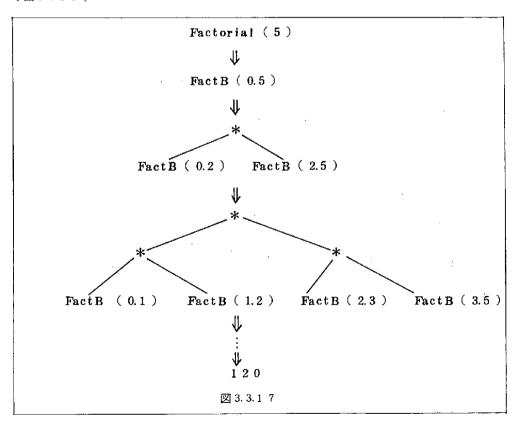

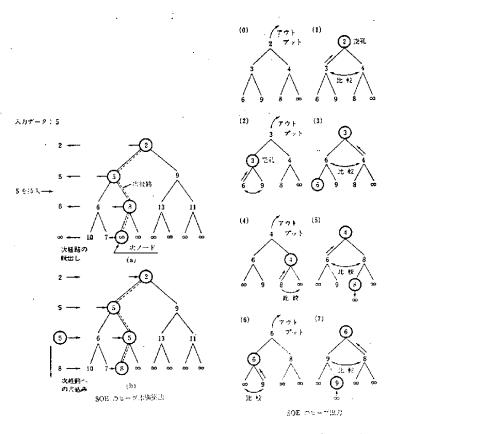

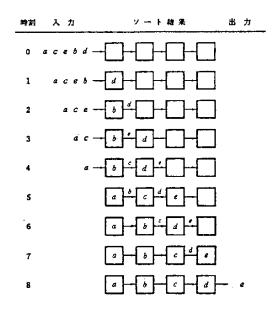

このデータフローマシンの検討報告書は 7章からなる。第 2章は、データフローマシン研究の背景 について記述しており、知識情報処理システムからの要請や現代のコンピュータシステムの問題点について述べている。また、計算モデルについての一般論やデータフローマシンの一般説明等が為されている。計算モデルの研究から見れば、制御フロー、データフロー、リダクションという分類が考えられ、リダクションマシンも検討すべき 1 つのアーキテクチャではあるが、その研究は未だ多くなく能力として不明な所も多いので今後の進展に待つことにし、以下、データフローを中心に検討を行っている。

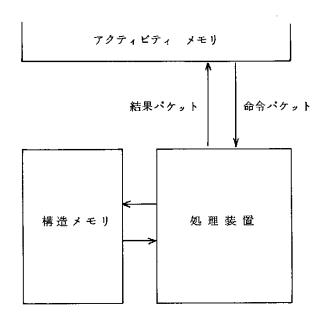

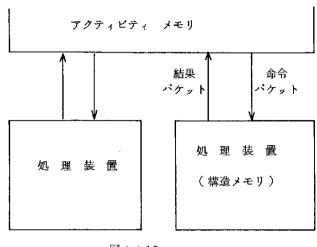

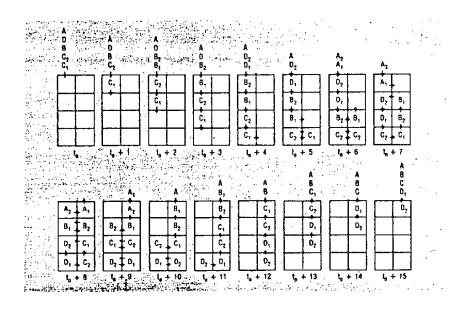

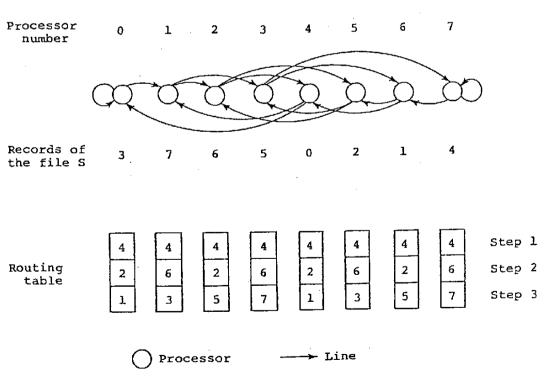

第3章はデータフローマシンの現状についてのサーベイである。まず、言語についてのサーベイで、 関数型言語、単一代入言語等データフローマシンに関係の深い言語の他、データフローマシン用とし て提案されているVAL、Id、VALID 等の言語の説明がある。次に各所で行われているデータ フローマシンとリダクションマシンの研究開発の現状についてのサーベイがあり、これら両マシンの 関連についても触れている。 第4章はデータフローマシンの諸技術を検討したものである。まず、データフローマシン用高級言語に関しては、従来の言語の問題点が如何に解決されるか、またデータフローマシン用言語一般の問題点とその対策について述べられている。次に、データフローマシンの制御方式と基本操作の検討では、発火したアクティビティの検出機構、手続き、ループ、条件式等の制御、基本構成要素等が述べられる。基本構成要素としては、アクティビティメモリ、処理実行ユニット、構造メモリ、入出力制御装置と、これらを結合するネットワークを考えており、これらそれぞれについてその構成法、問題点、等に関して述べられている。知識情報処理向きのデータフローマシンでは、特に構造データに対する取扱い能力が優れている必要があり、構造を蓄えそれに対する操作を受持つ構造メモリは1つのキー要素である。また、データフローマシンはその性質上、多くの並列動作要素を持っているため、それらの間の能率良い通信機能は全体の能力を左右する重要な要素である。

従来のコンピュータにおけるオペレーティングシステムに相当する機能に関しては未だ殆んど研究 が為されていない状況であるが、やはり重要な技術である。特に、データフローマシンにおける入出 力の扱い、発火したアクティビティを多くの処理実行ユニットのどこで処理するかを決定するアクティビティ割り付け方式、マシンの信頼性を維持するための誤り検出、再試行、システム再編成方式等 はその中でもまず検討されねばならない項目であり、これらについての検討が述べられている。

次に、データフローマシンを実装する場合当然問題となる VLSI による実装方式の検討、多くの並列度を含むデータフロープログラムや、データフローマシンを如何に能率良くデバッグするかの検討も為されている。特に後者は、データフローマシンの可能性を左右する重要なキーポイントとなる可能性があり、今後十分検討する必要がある。

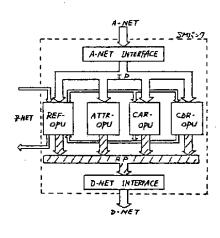

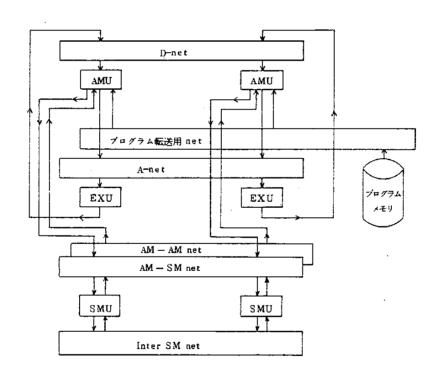

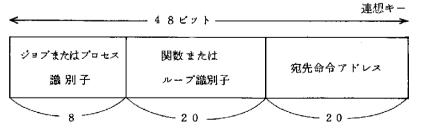

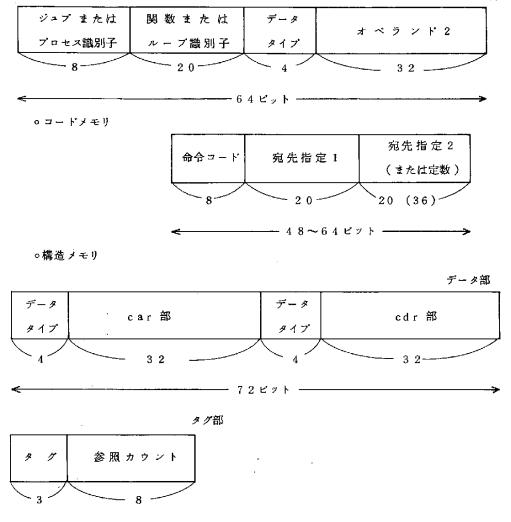

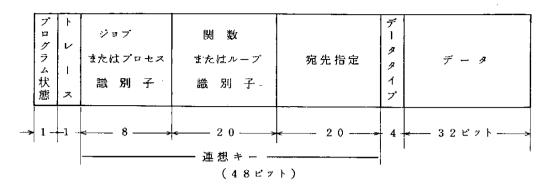

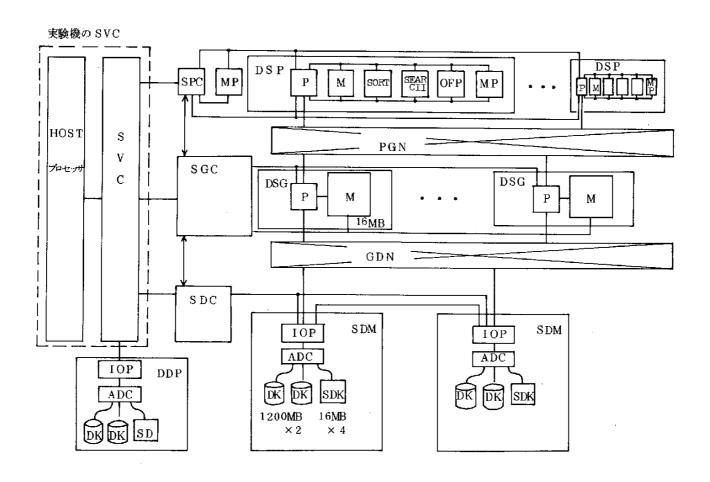

第5章は、以上の検討結果を踏まえて、データフローマシンのプロトタイプとして提案するもののイメージを記述したものである。記述は実験機第1版と第2版という形で分けておこなわれているが、データフローマシンの基本構造は両者ともに不変である。すなわち、実験機第1版の目的はデータフローマシンの基本構造を試作実験を通して示すことにあり、データフローマシンとして重要な要素は発んどその中に含まれている。高級言語としてはまず、汎用のデータフロー言語を設定し、基本命令も汎用の命令セットになっている。ハードウェアとしては、アクティビティメモリ、処理実行ユニット、構造メモリがそれぞれ数台ずつ設置され、それらが結合ネットワークを通して接続された形をとっている。マシン内を流れるトークンの形式としては、ジョブ、カラー等の識別用のタクフィールドが長い形になってかり、制御の様々な方式実験が行いやすいようになっている。また、アクティビティ制御にはハッシングを用い、各機能要素の制御にはマイクロプログラムを用いて制御の融通性を確保している。実装は、現在入手できる程度のLSIや TTL IC を用いるものとしており、特に高速性をねらう訳ではない。1つのアクティビティ制御に数48 程度要し、総合性能4 MIPS 程度が目標で

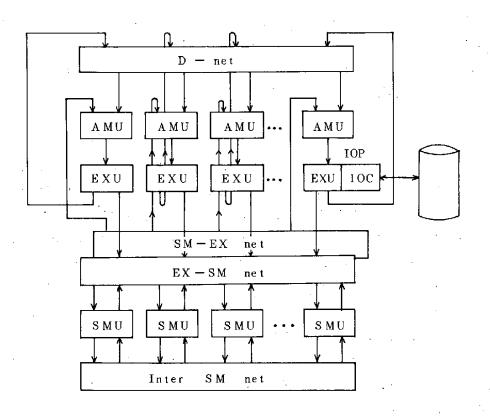

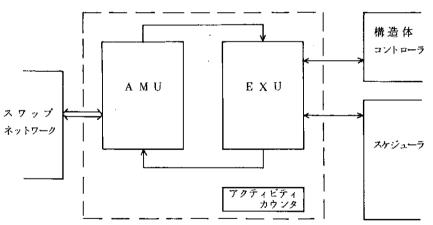

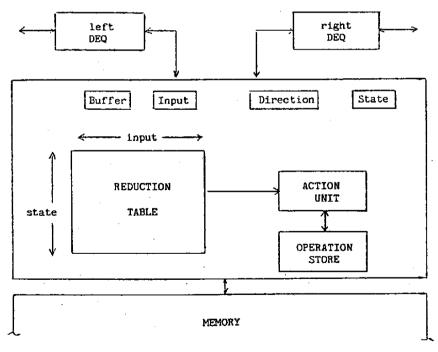

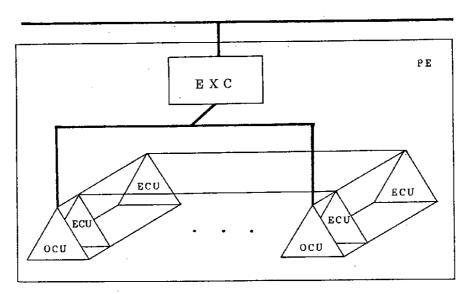

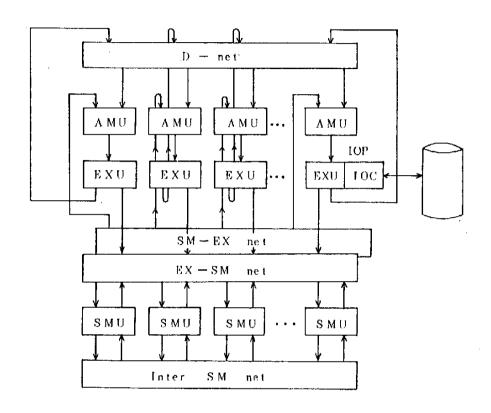

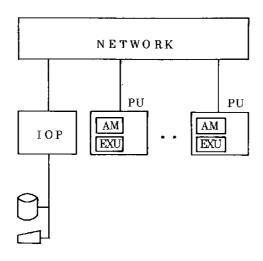

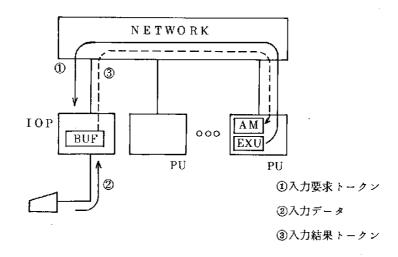

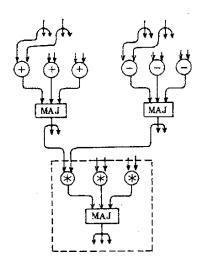

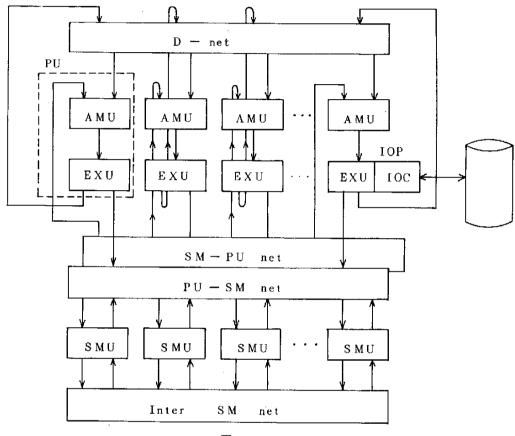

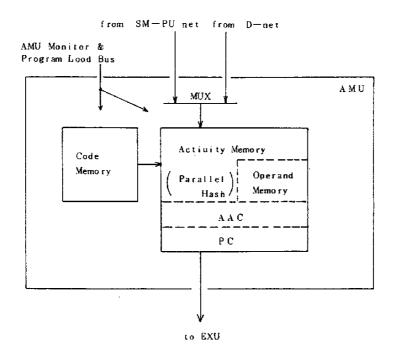

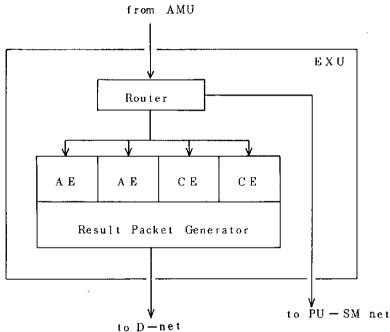

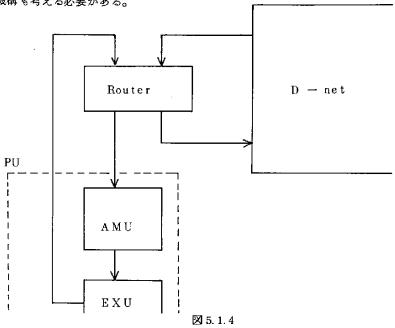

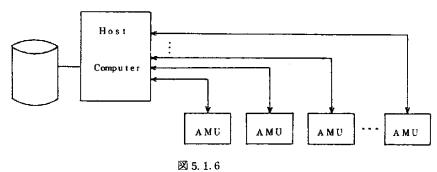

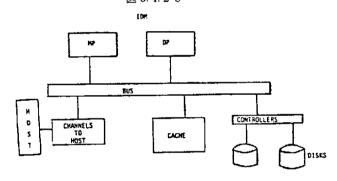

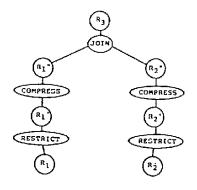

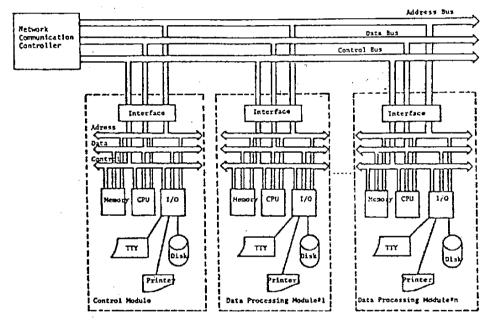

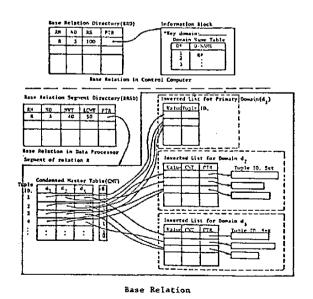

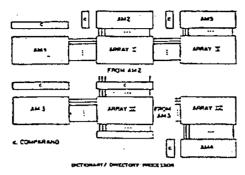

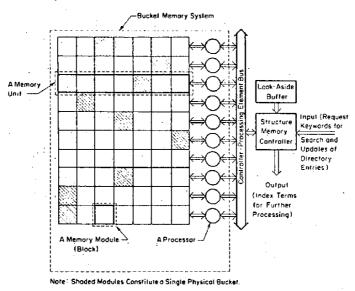

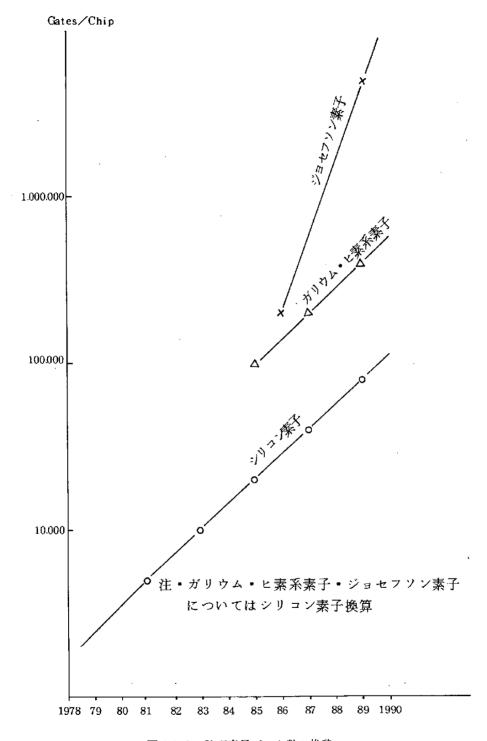

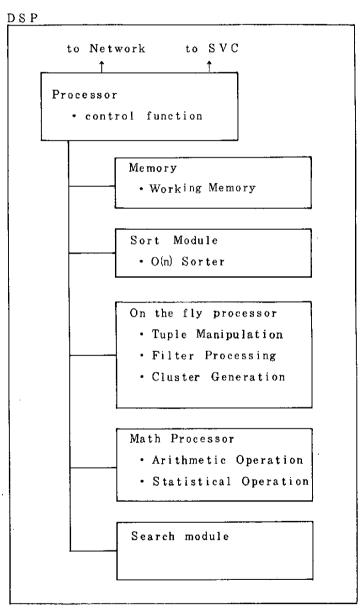

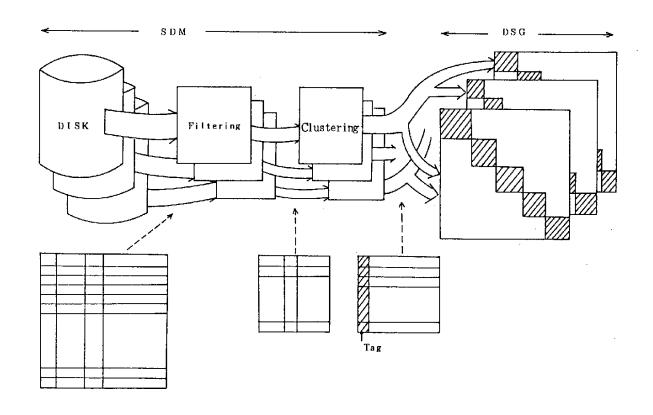

ある。実装すべきオペレーティングシステムは,実験のために必要最小限なものに限られている。 以上のような実験機の構成図を図1.1に示す。マシンの規模としては,図中のAMU,EXU,SMU 等の台数がそれぞれ8~16台程度のものを考えており,そのメモリ容量はAMU合計4MB,SMU 合計8MB程度のものである。

AMU: Activity Memory Unit

EXU Execution Unit

SMU : Structure Memory Unit

IOC : Input/Output Controller

D-net: Distribution Network

SM-EX net, EX-SM net

Inter SM net : 結合ネットワーク

図1.1 DFM実験機の構成

この実験機第1版での成果を基に作られる実験機第2版は、様々な項目の拡張・発展を目的としたものである。従って、基本構造は変わらず、速度の向上、並列度の向上、記憶容量の向上等の数量的な拡張やRASの向上等実用化技術の開発が外目には中心となる。VLSI実装を前提としたマシンとし、第1版における制御方式の検討結果を踏まえ、各要素の制御部はハードウェア化される。さらに、知識情報処理の核言語の開発に合わせてそれに向いた命令セットの実装、例えば統合化(unif-ication)向き命令セット等が設けられ、推論マシンとしての機能を備えることになる。

第6章は、以上のようなデータフローマシンを開発してゆくための研究計画を記述したものである。まず、研究課題を整理し、基礎研究、高級言語、応用、アーキテクチャ、制御ソフトウェア、実装法の6つに分類し、それぞれについて、何が課題となっているかそのポイントを詳述している。次に、それらの課題を明らかにしてゆくために設置すべきサププロジェクトの一覧が示され、課題との関係が述べられている。その後には各サププロジェクト毎に、その目標、研究ポイント、研究内容、研究計画等が詳しく述べられている。研究計画では、第5世代コンピュータプロジェクトの前期である1982~1984年までの3年間を対象とし、どういう順序で作業を進めるべきかが線表の形で述べられている。また、それら各サププロジェクトの遂行に必要な研究人員、所要道具等も示されている。サププロジェクトとして取り上げられているものは、データフローマンンの理論研究、応用研究、実験機第1版の試作、性能評価とシミュレーション、それに幾つかの個別研究である。個別研究には、高級言語、アクティビティ制御方式、アクティビティ割当方式、演算ユニット、構造メモリ、結合ネットワーク、入出力制御方式等の研究が含まれている。

第7章は、研究開発計画のまとめであって、第6章の各サプジェクト毎に述べられている各作業計画がまとめられており、合わせて各作業間の関連が示されている。また、所要人員等についてもまとめて一覧表になっている。

ことに示した研究開発計画は、最小限の人員、最短長の研究期間である。現在のコンピュータの原型が最初に作られてから今のような形になるまでに40年程が経っている。それとは全く新しい原理にもとづくシステムの現実的可能性を示すには、3年間は如何にも短かい。従って、前期3年間はこの基本的な原理の有効性・将来性を判断するための材料を提供するための基礎研究期間であり、ここで示した作業計画以外にも種々の形で並行して研究を進める必要があると思われる。

## 2. データフローマシン研究の背景と意義

#### 2.1 知識情報処理からの要請

第5世代コンピュータシステムは知識情報処理を目的として開発される。知識情報処理では従来の情報処理システムとは異なり、推論・問題解決、知識ペース管理など高度の機能が要求されることになる。これらの高度化された機能を効率的に実現するためには従来の数値計算主体の逐次制御によるノイマン方式のアーキテクチャでは無理があり、並列処理を基本とする新しいアーキテクチャを開発することが必要となる。

従来の処理方式では予め定められた手順に沿って処理を進めて行くことで事足りたが、推論を主体とする処理方式では前もって処理手順が定められているわけではなく、コンピュータは求められた目標に向かって、自ら手順を模索、設定しながら処理を進めていくことが要求される。推論処理では一意的に目標に達することはまれであり、多くの試行錯誤を経て目標に到達することになる。即ち非決定性処理が必然となり、この非決定性処理を効率的にサポート出来るマシンアーキテクチャが要求される。

非決定性処理の方式としては、depth first strategy、と breadth first strategy の 2 方式が考えられる。depth first strategy では複数個ある解法(処理手順)のうちどれか1 つを選んで、目標に到る (success)か、処理が進まなくなる (failure)まで処理を先へ進めてゆく。もし failure の場合には処理を後戻りさせ、他の解法を選び直して同様の処理を進める。一方 breadth first strategy では複数個の解法を並列的に試行してゆく。 depth first strategyは逐次的実行に適しており、現在多くの人工知能プログラムはこの方式を用いている。

しかし知識情報の規模が大きくなり、高度の知識情報処理を行う場合には推論の深度及び適用すべき推論規則の数も多くなり、それだけ試行錯誤の回数も増大することになる。このように複雑、高度化した処理を逐次制御をベースとする depth first strategyによっていたのでは有効な時間内で問題を処理することは不可能である。したがって多数の解法を(多数のプロセッサを用いて)同時並列的に試行させ、必要な解を早く見つける breadth first strategy を実現することが必要になる。

知識ペース管理においても知識ペース探索では大量の知識データの中から必要なデータを高速に探索して引き出してくることが要求される。従来のノイマン方式では実行制御部とメモリ部とのネックのために、知識ペース探索の高速化は困難である。知識ペース機能実現には関係データペース

機能などメモリシステム側に処理機能を持たせた高機能化メモリ方式が要求されることになるが、 とのような知識ペース管理ハードウェアと推論制御用ハードウェアを一体化し、高性能システムと して機能させるためには個々の機能を独立実行させる分散制御方式の確立が必要である。

知識情報処理で扱かうデータは個々の数値ではなく、記号とそれらの関係構造を表わすデータとなる。これは一般にパターンといわれる、推論処理にしる、知識ベース管理にしる、パターンの探索、照合、パターン構造の解析等が処理の基本操作となる。これらの操作をサポートする演算装置はノイマン型マシンにおけるALU等に比べはるかに高度である。特にパターンの照合、探索を効率的に行うためにはこれらの演算装置とパターン格納用メモリとが一体化される必要があり、このメモリ管理と推論実行制御を融和させ高速処理を実現するには集中制御を基本とするノイマン方式は不都合である。

最近VLSI技術の進展が著しく、今後さらに進展をとげるものと思われる。上記に述べた並列 処理、分散制御を実現するための素子技術がVLSI技術によって確立されつつある。多数個のVLSI 素子を並列的に同時動作させ、Breadth first strategyによる推論実行や多数バンクで構成 されるメモリシステム内での知識ペース並列探索などを実現するためのアーキテクチャの検討も非 現実的なものではないと思われる。

とのように多数個のVLSI素子を用いて高度の並列処理を実現し、推論処理、知識ベース管理を可能とするためには高度並列処理の計算モデルとそのモデルにもとづくアーキテクチャの具体化が不可欠である。

現在,並列処理,分散制御を実現するための計算モデルおよびアーキテクチャとしてデータフローマシンがその実現化の可能性という観点から有効であると考えられる。

データフローマシンでは\*各演算はその必要なオペランドが揃ったときにいつでも実行可能となる "という実行原理により処理を進める。この実行原理によりデータフローマシンは従来のノイマン型マシンに比べて高度並列処理, 関数的処理, 分散制御, 記憶セル概念の排除, 等を徹底させたアーキテクチャ方式およびプログラミング方式を実用的なものとする可能性をもっている。

またこれらの特性から、データフローマシンは関数型処理方式をさらに発展させた述語論理型処理方式すなわち先に述べた推論処理、知識ペース管理のためのハードウェア基盤を与える可能性を 持っているといえる。

この可能性を追究し、実用的なマシンアーキテクチャを確立していくことが本プロジェクトの目 的である。

## 2.2 データフローマシンの目的と意義

本プロジェクトは第5世代コンピュータシステムのハードウェアアーキテクチャの基盤を確立することを目的とするものである。第5世代コンピュータは知識情報処理を主たる目的として開発されるが、高度の知識情報処理をサポートするマシンの構造としては従来のノイマン方式による逐次型マシンでは処理能力の点で不都合である。第5世代コンピュータのソフトウェア方式は従来方式とは質的に異なり述語論理の概念を基本とし、その処理メカニズムには非決定性処理、パターン照合処理、関数的処理等の機能が要求される。これらの機能を実現しかつ処理を実用的時間内で行なうためには、多数個のVLSI素子を同時実行させる高度並列処理の方式を確立することが、第5世代コンピュータのハードウェアアーキテクチャ開発課題となる。このような高度並列処理マシンのアーキテクチャとしてはデータフローの原理にもとづく方式が有効であると考えられる。VLSI素子技術の進展は著しく、今後さらに高集積、高機能化素子が開発されていくものと思われるが、これらのVLSI素子を多数個用いる情報処理システムのイメージは定かでなく、コンピュータアーキテクチャに課せられた研究課題となっている。この多数個VLSIを用いるシステムの制御方式としてはデータフロー概念にもとづいて分散制御を実現するのが現在の所最も有効なように思われる。この意味でもデータフローマンンの方式確立はコンピュータアーキテクチャにとって重要な研究項目であるといえる。

データフローマシンの開発は世界的にみてもまだ基礎研究の段階であり、実用マシンの開発を目指した研究は未だ行われていない。

また世界の研究の大半は超高速科学技術計算を応用領域と考えて研究を進めており、第5世代コンピュータプロジェクトのように知識情報処理、即ち記号処理を応用領域と考えたデータフローマシンの開発研究は日本独特のものである。この意味で本プロジェクトの構想は世界先導的であり、プロジェクトの与えるインバクトは大きいといえる。

第5世代コンピュータの開発では、そのサブシステムとして推論サブシステムおよび知識ベースサプシステムを開発し、これを融合させていくという方策をとる。この両サプシステムは中期段階で並列処理方式にもとづいて開発が進められる。このためのハードウェアメカニズムは高度並列処理をサポートするものでなければならず、その基盤は本プロジェクトで確立されたデータフローマンンアーキテクチャにより与えられることになる。即ち中期に開発される両サプシステムのハードウェアシステムとしては並列型推論マシンサプシステムおよび並列型知識ベースマシンサプシステムが予定されているが、この両マシンサプシステムの開発にはデータフロー制御方式、データストリーム処理方式、構造メモリ構成方式、ネットワーク構成方式などの要素技術の確立が必要になる。

本プロジェクトの推進によって確立されるデータフローマシン方式に関わる種々のハードウェア構成方式、実現方式、実装方式等がとれらの要素技術確立のための基盤を与えるととになる。

#### 2.3 計算モデルとデータフローマシン

最近のVLSI技術、素子技術の進展には目覚ましいものがあり、高速・高機能・低コスト化の傾向を強めている。一方、ソフトウェアの低生産性の問題が顕在化しており、知能処理への要求が高まるにつれて、今後益々問題となってくるものと思われる。これを背景に、30数年以上続いたノイマン原理にもとづく計算機の構造を変革し、ノイマン原理に依らない言語および計算機アーキテクチャを構築しようとする動きが活発化してきている。ノイマン原理のコンピュータの特徴は、CPUとメモリを結ぶ一本の通信路からなる構造、通信路を経由して one at a timeに進められる計算、プログラムカウンタを用いた逐次的・集中的制御、線形アドレスメモリ概念にある。かってノイマン型コンピュータの利点であったこれらの特徴が、今日の計算機にさまざまな幣害をもたらしていることが明らかになってきた。

例えば、プログラムカウンタによる逐次制御(single control flow stream)は、並列処理構造を実現する上で大きな支障となり、VLSI技術への適合が困難である。また、プログラムの面では、一本の計算の道筋を与えてしまい並列実行可能性を失う他に、goto 文にみられるように jump 概念が入りプログラム構造を不透明にする。一方、メモリセル構造は、計算に本質的でないプログラム変数なる概念をもたらし、副作用などわずらわしい問題を引き起こす元凶になっている。

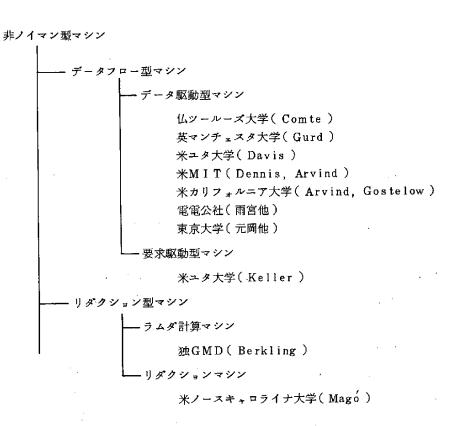

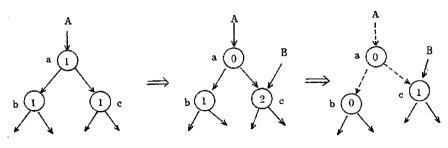

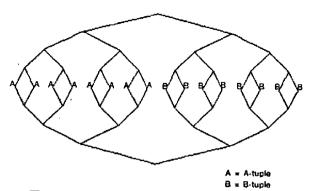

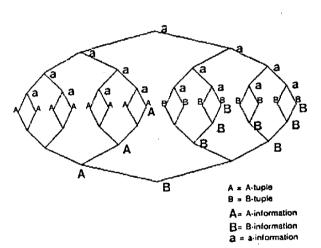

このような反省を基に、ノイマン原理から脱脚した新たな計算機構(非ノイマン型コンピュータ)が注目を集めるようになった。図 2.3.1 は非ノイマン型コンピュータの研究動向をまとめたものである。これらはデータフロー型マシンの研究とリダクション型マシンの研究に分かれるが、いずれも関数型マシンとして位置付けられる。

## A. データフロー型マシン

データフローマシンのアイデアは最初 J. B. Dennis によって明確に提示された。

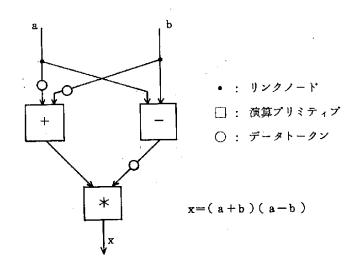

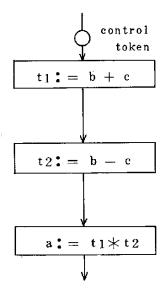

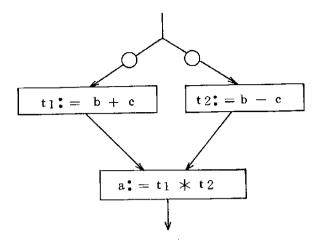

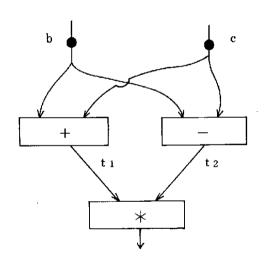

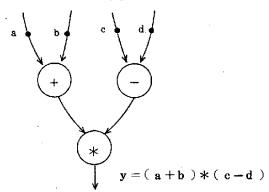

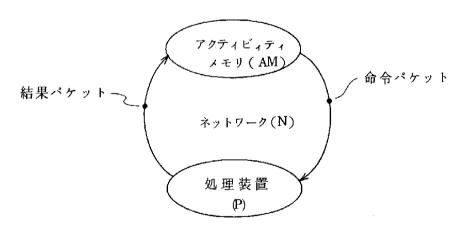

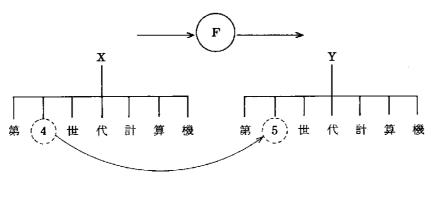

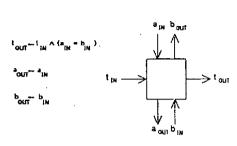

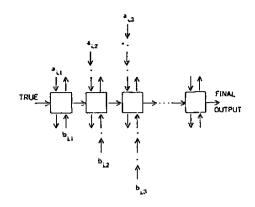

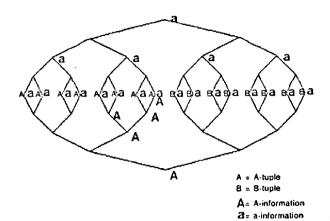

データフローマシンでは、図2.3.2 に示すように、プリミティブなレベルのプログラムは演算間のデータの流れを記述するデータフローグラフで表現される。データフローグラフは、入力トークンが入れられると実行を行い、出力トークンを出す、関数を定義しているとみることもできる。

関数あるいは命令の実行契機の与え方の違いによって、データフローマシンはデータ駆動型と 要求駆動型に分けることができる。

データ駆動の原理では、命令は必要なデータ(トークン)が全て揃った(到着した)ときに何ま 時でも実行可能となる。実行原理は、命令の実行順序が制御移行(control flow)の形で予め

図 2.3.1 非ノイマン型マシンの研究動向

図 2.3.2 データフローグラフ

定められている従来のマシンとは大きく異なっている。関数の実行順序はプログラムカウンタの 指示やデータフローグラフの位置によらず、データの依存関係のみで決まる。プログラム中に並 列実行の指定を陽に行わなくとも、問題に内在する並列性がそのままの形で引出される。

データフローマシンは、このような実行原理を具体化するマシンとして提案されているものであるが、プログラムカウンタやメモリセルの概念は持っていない。ノイマン型マシンの元凶は少なくとも原理において取り除かれている。このことおよび自然な形で並列処理を達成しらる構造であることがデータフローマシンの大きな魅力である。

一方要求駆動の原理では、命令はその結果が必要とされるときに駆動され、命令の実行に必要なデータが到着してなければその発生元の命令に要求を出す。要求駆動は、無駄な計算を行わずに済み資源の有効利用が図れる点や、計算の能力の点(例えば、必要になるまで実行を引き延ばす遅延評価が行いやすい)でデータ駆動よりすぐれた面を持つが、実現性、効率の観点では問題がある。現在研究・開発されているデータフローマシンの殆んどはデータ駆動型である。一般にデータフローマシンという時にはデータ駆動型をさす場合が多い。

#### B、リダクション型マシン

リダクションの機構では、ひとつの式を実行できる部分から評価してその部分式を評価結果のデータで置き換えていくことによって計算が進められる。literal substitution (文字 列置換え)による還元(reduction)が計算の基本となる。リダクション型マシンはこの機構をハードウェアで実現しようとするものである。

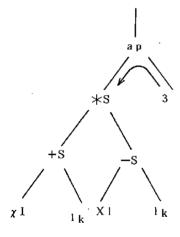

Berkling はこの考えにもとづき、スタックを用いたラムダ計算マシンを開発した。ラムダ計算において入式の引数への適用 (application)を、式中の変数の文字列置換えという方法で還元していくものである。 call by name, call by value, static binding などを実現するため機械語として数種類の application primitive を用意している。

最近では、J. Backus の提唱した関数型言語(FFP)を実行する Magoのリダクションマシンが注目されている。引数評価が最内側から行われることに特徴があり、全引数が予め評価されるまで関数の計算は始められない。計算が最内側から行われる点ではデータ駆動と差はない。

リダクションマシンは、ノイマン原理からの脱却を図った関数型マシンのあり方として示唆に 富んだものであるが、実現性の面で不明な点が多い。

#### C. 計算モデルとの関連

ノイマン原理に依らないコンピュータとして、データフロー型マシンおよびリダクション型マシンの研究が行われているが、これらのマシンの計算基盤となる計算モデルとプログラミング言語との関係について少しふれておく。計算の構造について考える場合、言語の syntax (表現の

世界)と semantics (意味の世界)を記述した formal system とその computing system (計算の世界)とに分けてとらえるとみ通しがよくなる。

計算モデルは computing system を抽象的に表現したものであり、言語の semantics をマシンの上で実現する機構を規定するものである。これまでに存在するあるいは提案された計算モデルを整理すると、control flow モデル、data flow モデル、reduction モデルに分類することができる。これらのモデルの特徴については 4.2.7 計算モデルで詳述する。

control flow モデルは従来のノイマン型マシンをモデル化したもので、プログラムカウンタによって逐次的に進められる計算を、制御の流れ(control flow)としてとらえる。メモリ概念が存在し、データは参照によって(by reference)処理される。制御の流れは、単一(single control flow stream)であり、従って計算の道筋は一意に定まる。

data flow モデルは、データフロー原理(by value)にもとつく計算をモデル化したものである。実行に必要なオペランド(データトークン)が到着するといつでも実行が始められる。データに依存関係がない計算は独立に(並列に)実行することができ、計算の道筋は複数存在する。data flow モデルを具現化したマシンがデータフローマシンであり、パケット通信を基本に構成される。

reductionモデルは適用型言語の semantics を忠実に反映した計算モデルである。 application の過程を reduction としてとらえ、文字列の置換えにより計算が進められる。 置換の対象 (reducible subexpression)が複数個存在する場合、それらは任意の順序で置換が行われてもかまわない。したがって計算の道筋は複数存在することになる。 reductionの 方法には、直接文字列そのものを置換する string reduction と、ポインタを利用して式 (グラフ)の変更を行う graph reduction の 2 つがある。 reduction マシンの構想例はいくつかあるが実際に作られた例は、Berklingによるスタック型の マシンのみである。

ここで各計算モデルと言語及び実マシンとの関係を少し考察しておこう。

control flow モデルはノイマン原理そのものであり、従来型言語およびノイマン型マシンとの結びつきがはっきりしている。一方、data flow モデルは、言語の semantics が先にあってそれを実現するモデルとして提案されたというより、むしろデータ駆動制御という計算の進め方から生まれたモデルである。data flow モデルと対応関係にある言語として、単一代入言語をもげることができるが、単一代入規則を遵守すれば data flow 計算に適合するという歴史的過程から生じた関係にすぎない。したがって data flow モデルの上にどのような言語を乗せるかが問題となる。data flow モデルは関数的性質を保存しており、駆動による実行という観点からも関数型(適用型)言語や論理型言語との関係が深いが、それらの言語と計算モデルとして

どういう関係にあるのか、それ程明らかになってはいない。これに対して、reductionモデルはラムダ計算における semantics を反映したもので適用型言語と密接な関連がある。しかし 実際の reductionマシンとして具体的に提示された例はなく(Berklingらの試みはあるが)、実現性については不明である。最近注目されたした論理型言語に目を移すと、論理型言語の semantics を反映した計算モデルも実マシンも今の所存在しない。

データフローマシンが関数型あるいは論理型言語の実行マシンとなるかを探究する糸口として、関数型言語と論理型言語の違いについてもう少しみてみよう。言語の syntax (スタイル)の面では、関数型は applicative であり、論理型は declarative である。計算モデルと関連の深い semantics の面からは次のことがいえる。関数型ではオプジェクトの変換(オプジェクトからオプジェクトへの写像)と内側計算を基本とし、どのような変換過程を辿っても一意に解に到達する(もし存在すれば)normal form property を持つ。

一方論理型では、resolution が計算の基本となる。この場合、何通りもの解が存在し、また一意に解に到達するとは限らないので normal form property は成立しない。

データフロー型マシンはかなり研究されてきており、リダクション型マシンに比べると実現性 が高いと思われるが、これを関数型あるいは論理型言語の実行マシンにするためには data flow モデルとそれぞれの言語の計算モデルとの関連を明確化しておく必要がある。また data flow モデルと reduction モデルの計算機構としての得失を明らかにしていくことも重要である。

# 3. データフローマシン研究の現状

## 3.1 データフローマシン用言語の研究開発の現状

データフローマシン用言語としては単一代入型言語と関数型言語がある。単一代入型言語は1つの手続き内では同じ変数に2度以上値を代入してはいけない、いいかえれば代入文の左辺に同じ変数名を2回以上使用してはならないという制限を持っている。この制限によりデータの間の副作用がなくなり並列計算が可能となる。この型の言語は従来の手続き型言語であるFortranやAlgol等とみかけ上あまり大きな違いがないため多くのデータフローマシンに採用されている。単一代入型言語は、通常はデータフローグラフに変換され、データ駆動方式により実行される。

一方関数型言語は数学の関数の概念をそのままプログラミング言語に取り入れたもので、 f(g(h(x)))のようにプログラムを記述する。関数型言語は通常ラムダ計算にもとづき、リダクション方式により処理されるものが多い。

この節では単一代入型の言語の代表として Val, Id, Valid, CAJOLE を取りあげた。その理由は前3者はコンパイラを作成中であり活発な研究が続けられているため、また CAJOLEは その理論的な面に興味があるためである。

#### 3.1.1 Id

A. 場 所 カリフォルニア大学アーバイン校

B. 人 Arvind, R. Thomas 等

#### C. 特 徵

ブロック構造を持つ単一代入型の言語で構文的には Algol にもとづいている。言語の意味はデータフローグラフで表わされ、演算はノード、変数はグラフの線、変数の値は線上にあるトークンに対応する。線上のトークンは2個以上同時に存在してもよい。

Id の基本的機能を以下に述べる。

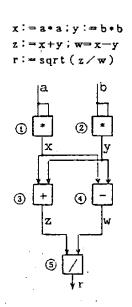

ブロックはノードを線で結んだもので、通常の演算を表現したものである(図3.1.1)

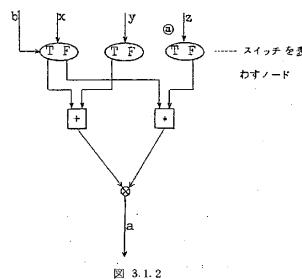

条件式は図3.1.2で表わされる。bが真であると各スイッチはTの方の線にトークンを出し、 偽であればFの方の線にトークンを出す。

(if b then x+y else x=z)

図 3.1.1 .

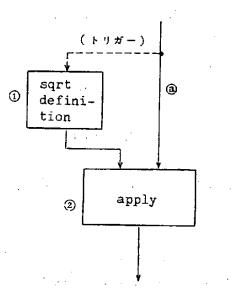

関数の呼出しは apply 演算子を用いる。図 3.1.3で①の箱は②の線へトークンが来ると 2乗根を求める関数 Sqrt の定義を出力として②の箱へ送る。②の箱は②の引数を表わすトークンに①から来た関数を表わすトークンを適用してその結果をトークンとして出力する。

図 3.1.3

ループは図3.1.4のように表現される。

演算上はこのループに入るトークンに色をつける働きをする。Idでは同じ関数を並列に実行する場合プログラムを共有することが可能になっている。そのためユーザ定義の関数単位でトークンに色を付け、どの関数に属するトークンであるかを識別している。ループも1個の関数とみなすので上が必要となる。Liはループから出て行くトークンの色を取り去り、このループを呼んだ関数の色を与える。Pは繰り返しの判定式で、この値が真なら繰り返しを行い、偽ならループを抜ける。Idではループの中も並列に実行する。従ってn-1回目のループのトークンとn回目のループのトークンが入り混じるため各ループごとに色を付ける。それがDで、D・はその色を取り去る。

(initial  $x \leftarrow a$ while p(x) do

new  $x \leftarrow f(x)$ return x)

TF

3

1

2

3

3.1.4

データ構造はトークンの列を一まとめにする

ストリームと構造メモリ(I – Structure )がある。この構造メモリの特徴は書き込みも読み出しも1回しか許さないことである。こうすることにより副作用を防止している。

Val との相異は思想的にはVal が静的(すなわちコンパイル時)に処理を行うのに対し、Id は動的(実行時)に処理を行う。文法的には Val は型宣言があり、Id にはない。意味的には Val はグラフの線上に1個のトークンしか許さないが、Id は複数個を許す。

## D. 問題点

処理を動的に行うのでオーバヘッドが大きいといわれている。

#### E. 現 状

IdをLisp に変換する版とデータフローグラフに変換する版のコンパイラが開発されている。

#### 一参考文献一

- 1) Arvind \*データフローアーキテクチャの研究開発 \* 電子協昭和54年度特別セミナー議事録

- 2) Arvind 他 "An Asynchronous Programming Language and Computing Machine" California Irvine TR114A, 1978.

#### 3.1.2 VALID

VALID(Value Identification Language)は電電公社武蔵野通研で設計・開発が進められているデータフローマシン用高級言である。1)

武蔵野通研ではデータフローマシンの研究を、数値処理用と記号処理用の両面から行っているが、 両マシンでのプログラミング環境を構築するために、汎用の高級言語として設計されたものである。

VALIDは関数概念を徹底させた適用型の高級言語で、シンタクスはAlgol 風を基調としながらセマンティクスはあくまで関数型を貫くという設計思想にもとづいており、以下の特徴を有している。

(I) プログラム変数の概念はない。プログラムは Value 定義, Function 定義および Macro 定義のみからなる。特に Value 定義式では,

(

$$x_1, x_2 \cdots, x_n$$

) =  $< expression>$

により複数 value を一度に定義できる。

- (2) 式の集合である Block 概念を持つ。 Block 自身も式であり、 clause · · · end で定義される。 Block 中では scope ルールに従う local value の定義が許される。 Block中の式は : で区切られるが、 評価順序はデータ依存関係のみに依る。 Blockの生成する値は return 式 により示される。

- (3) 繰返しは全て再帰概念にもとづいて記述される。従来型言語でのループ表現による繰り返しは、 次のような再帰式で記述される。

$$\underline{\text{for }} (< \text{iteration value names} > \underline{)} \underline{\text{init }} (< \text{initial values} > \underline{)}$$

do <block including recur expression>

再帰式は無名の再帰関数を定義するものと解釈する。

(例1)

$$\begin{array}{cccc} \underline{for} & (r, q : integer) & \underline{init} & (y, o) \\ \\ \underline{do} & \underline{if} & r < x & \underline{then} & \underline{return} & (r, q) \\ \\ & \underline{else} & \underline{recur} & (r-x, q+1) \end{array}$$

(4) 複数 Block の並列実行は fork - join 概念にもとづく並列実行式 2)

for each <value name> in [<expr1> · · · < exprn>]

do <parllel body>

return < construction expression>

により陽に表わすことができる。

(例2)

$$\frac{\text{for each i } \underline{\text{in}} (1 \cdots \text{n}) \underline{\text{do}}}{z = a(i) * b(i)}$$

$$\text{return vector } (z)$$

(5) その他、階層的な Function、Macro の定義機能、データの構造化機能(vectorなど) で他、高階関数の定義機能を有する。

(例3)

(例4)

add: <u>function</u> (x,y:integer) <u>return</u> (integer) = x + y;

mul: <u>function</u> (x,y:integer) <u>return</u> (integer) = x + y;

高階関数 reduce を使うと、整数系列の和・積は次のように定義することができる。

sum (x) = reduce (add, x, o)product (x) = reduce (mul, x, 1)

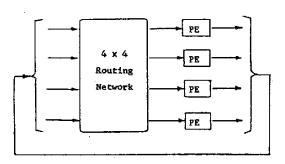

現在、Valid コンパイラ作成が終了し(Maclispで書かれている)、リンケージローダ等プログラミング環境の整備が行われている。Valid コンパイラはソースプログラムをS式表現された中間言語(データフローグラフ)に変換するものである。この中間言語から、DECシステム 2020 上で開発されたデータフローマシンミュレータおよび 4×4 P E 構成のデータフローブロセッサアレイ実験機EDDYのコードに変換するアセンプラが完成している。

VALIDでは I/Oのサポートが未だ行われてなく、stream 処理、history sensitivity 処理のための機能拡張を検討中である。

#### 一参考文献一

- 1) 雨宮, 『データフローマシン用高級言語 Valid の設計思想』, 昭和56年信学会全国大会 Na.1486.

- 2) 尾内, 雨宮, "データフローマシン用言語 Valid における並列実行式の処理", 情処学会第22回(昭和56年前期)全国大会, 5B-4.

- 3) Amamiya M., Hasegawa R., and Onai R., "A Functional Programming Language VALID and Data Flow Machine as Its Computing Apparatus", To be published shortly.

# 3. 1. 4 VAL

VAL (Value oriented Algorithmic Language )はMITのW.B. Ackerman, J. B. Dennis らによって1979 年頃開発されたデータフローマシン用高級言語である。

# A. 特 徵

VALは数学的意味においての関数型言語であり、並列性は implicit に表現される。つまりプログラマやコンパイラは特別な記法を用いることなく大部分の並列性を認識することができる。以下VALの特徴について簡単に述べる。

#### 関数型構造

通常の言語が文(statement)と変数によってプログラムを記述するのに対し、VALでは式(expression)とValueによって記述する。VALにおいてactiveなものは全て式であり、何らかの結果を生成する。これはif文、case文、loop文においても同じである。表記上VALにおいてValue はidentifierにバインドされるが、通常の変数とは異なる。この意味でVALはLISPと類似性を持つが、代数的表記であること、strongly-typed 言語であること、等が異なる。

VAL

LISP

A + B \* C

(PLUS A (TIMES B C ))

if A = B then C

(COND ((EQ A B ) C )

else D endif

(T D )

図 3.1.5

- Implicit concurrency

VALでは副作用がないため、プログラム内のほとんどの並列性は implicit に表現される。

- Special parallel features

VALではいくつかの特別な並列性表現が用意されている。図3.1.6 は配列計算におけるforallの例である。

forall I in (1,10)

Mean, SD: real

: = Stats(A(I), B(I), C(I));

Plus 2: real

: Mean + 2 ★ SD

construct

endall

• Explicit limits to concurrency

VALにおいて並列性を制限する言語構造は if 文, tag case文, for文の3つである。 for文の例を図3.1.7に示す。これはFibonacci(n)を求めるプログラムである。先頭の部分はループパラメータの初期化である。

```

for

Count, Fib, Pre-Fib: integer % init. Values for

:=0,0,1 % the loop parameters

do

if count < = N

then iter

Pre-Fib, Fib : =

Fib, Fib + Pre-Fib;

Count := count + 1

enditer

else

Fib

% Expr. result

endif

endfor

図 3.1.7

```

#### B. 現 状

言語仕様  $^{1)}$  も確定しており各種の応用プログラムによって評価が行われているが、 $^{3)}$  I / O 関係に不充分な点もあるため、言語仕様の練り直しも行われている。

#### 一参考文献一

- W.B. Ackerman, J.B. Dennis : VAL A Value Oriented Algorithmic Language Preliminary Reference Mannual, CSG, TR-218, MIT, June, 1979.

- 2) W. B. Ackerman: Data Flow Language, AFIPS, Vol. 48, June, 1979.

A CONTRACT OF A

3) J.R. MacGraw: The VAL Language Description and Analysis,

Lawrence Livermore Laboratory, Dec., 1980.

#### 3.1.5 CAJOLE

CAJOLE(1)は1978年,ロンドン大学のウェストフィードカレッジ, 計算機学科のC.L. Hankin, P.E. Osmon, J.A. Sharp によって発表された高水準データフロー言語である。 CAJOLE の特徴は以下の通りである。

(1) 非手続き的である。

プログラムは順序づけられない定義(文)の集合である。その実行順序はデータの到着状態に のみ依存する。

(2) 単一代入規則に従う。

このため、ループ構造を許さず再帰呼出しの形へ変換している。

(3) 関数型言語である。

プログラム内の全ての定義は関数定義と考えられる。関数定義の記述法は以下の通りである。

name expression = (parameter list)

value expression

ここで、 [parameter list]は省略することができる。

(4) 非決定的処理機構を導入している。

Dijkstra の guarded command(2)を取り入れている。その形式は以下の通りである。

guard : expression

guarded command の解釈法(特に複数の guard の値が真になるとき)については特に 規定していない。

(5) 名前の局所化機能を備えている。

with・・・ wend 節を用いて特定の式の名前を結合している。

(6) プートストラッピング機能を導入している。

との機能によってユーザ自身が構文を定義できる。プートストラップ定義の一般形は以下の通 りである。

(parameter list) construct name

= defining expression

construct name はハラメータを区切るシンボルの列である。シンボルには予約語(十,一等)を除く1文字, ないし下線を付した文字列である。

(7) オペレータ

言語では標準的な比較、論理および算術オペレータを用意している。そのオペランドは単純オ

ペランド(例えば整数)でもよいし、集合オペランド(例えばペタタ)でもよい。

(8) システム標準構文

条件式やくり返し式等のための構文はシステムで定義されている。

以下に階乗を求めるプログラム例を示す。

dummy, factorial n

= factorial (n,1)

with factorial

= (n, fact) if n > 0then factorial  $(n-1, fact \times n)$ else n, fact

wend

このプログラム例では関数(factorial)の再帰呼出しが発生する度に関数本体が次々とコピーされて実行される。

問題点としてはプログラミング上の制約条件が大きすぎる(例えばループ構文を許さない)と とがあげられる。

論文 1)を発表した時点では CAJOLE のコンパイルによって生成されるペース言語の設計 途中にあり、これをもとに従来マシン上でのシミュレーション/エミュレーションを行う予定で ある。

# 一参考文献一

- C. L. Hankin, P. E. Osman, J. A. Sharp, "A Data Flow Model of Computation". Department of Computer Science, Westfield College (Univ. of London), March 1978.

- 2) E. Dijkstra, "Guarded Command, Non-determinancy and a Calculus for the Derivation of Programs". Springer Verlag Lecture Notes in Computer Science Na 46, 1976.

# 3.2 データフローマシンの研究開発の現状

データフローマシンは現在、欧米・日本の各所で研究が進められている。データフローマシンの研究の発端は、1945 年にペンシルバニア大学の Van Neuman が提言して以来今日まで発展し続けてきたノイマン型アーキテクチャに対する物理的限界と、そのアーキテクチャがもたらすソフトウェア危機の認識にある。特に1970年代における並列計算機の研究においてその楽観論が後退したことにより、データフローマシンへの期待が一層高まってきたと言える。

データフローマシンの基盤となる言語やプログラムのデータフローに関する研究は、前節で述べたように1960年代後半からあった。これに対しデータフローマシンの構造についての研究が本格的に行われるようになったのは1970年に入ってからである。先駆的研究を進めてきたのはMITのDennisらのグループであり、当初は小規模な専用高速プロセッサから始まっている。それ以後米国のみならず欧州、日本など世界中に研究が広まってきている。

現在までに多数のマシンが提案・試作されてきており、データフローマシンの性格も、高速汎用機を目指したもの、数値計算向きのもの、記号処理向きのもの等、豊富になってきている。すでに ツールーズ大学、マンチェスタ大学、東京大学などにおいては実験機が稼動している。

これまでに行われてきたデータフローマシンの研究開発は、大学や研究所が中心であたったが、 現在は計算機メーカにおいても本格的に取り組んでおり、データフローマシンの研究が実用段階に 入っていることがわかる。

以下、海外および国内で進められているデータフローマシンの主な研究について述べる。

#### 3.2.1 Dennis (MIT)マシン

A. 開発時期 : 1970年前半

B. 開発者: J.B.Dennis (MIT)

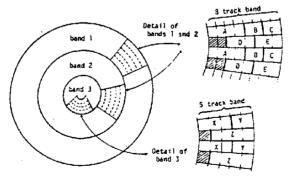

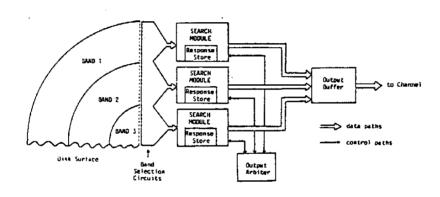

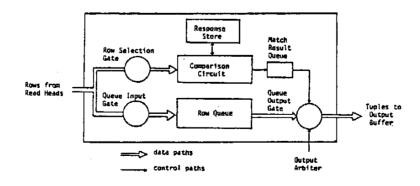

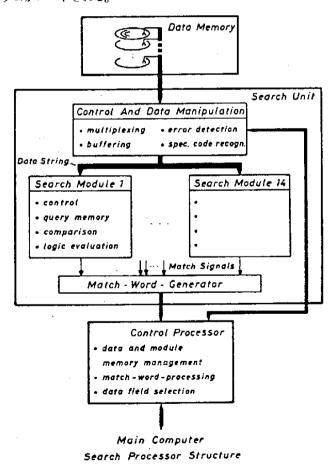

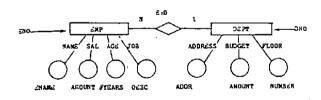

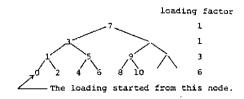

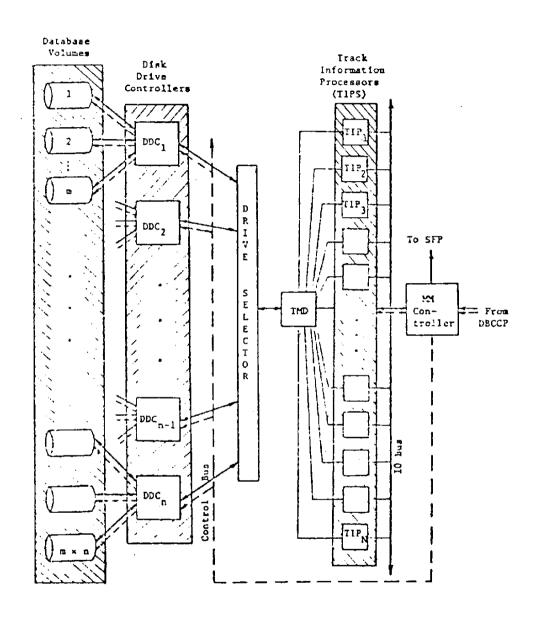

C. 特 徴 : データフローマシンとして最初に研究されたマシン。原始データフロープロセッサ、前基本データフロープロセッサ、基本データフローブロセッサへと段階的に研究が進められている。Dennisのマシンの思想は原始データフロープロセッサ [ DENNIS 79 ] に適切に表わされているので、そのシステム構成を図3.21に、また、その中のセルプロックの詳細を図3.2.2に示す。

o Function Unit を共有化

実行可能な命令を検出する部分と、実際にその命令を実行する部分とを分離し、実行ユニットを共有化している。従って、命令から命令への通信時間は、命令がどのセルに位置している

図3.2.1 Dennisマシンのシステム構成

図 3.2.2 セルブロックの構成

かに無関係である。

# o Ack信号の使用

命令の発火規則として,オペランドデータが揃り事以外に,その命令の出力アーク上に結果

が残っていない(即ち,その次の命令によって受け取られている)事をも条件として追加されている。それ故,アーク上には1個のトークンしか存在することが許されないが,パイプライン的にデータフローグラフを使えることになる。

セルブロックがキャッシュ的

入り切らない命令は、Instruction Memory に置いておく。例えば、手続きが呼び出された時には、手続全体のコピーを作らずに、その手続の最初の命令セルしか作らず、実行が進むにつれて順次コピーが増えて行くので必要な命令だけがセルブロックに存在する。

- D. 問題点: 特徴でもある点が逆に問題点にもなっている。

- 命令間の通信時間が大

実行ユニットを共有にして、実行可能な命令を検出する部分と分離した構成になっているととで、ローカルなフィードバックが出来ず、命令間の通信時間が常に遅いと考えられる。

o 並列性が小,通信量が大

Ack信号を使用しているため、アーク上には1個のトークンしか存在出来ないので、識別子をつけたトークン方式に比べて並列性が出ない。

また、Ack信号を使うために、通信量がほぼ2倍になり、ネットワークに負担がかかる。

E・現 状 : プロトタイプシステムの作成を計画している[DENNIS80]。その構成を図3.2.3 に示す。

図3.2.3 Dennis のプロトタイプマシン

当初の構成図と異なり、一見、Arvind型と同一に思われる。ただしPEがマイクロプロセッサを使ったユニバーサルなモジュールで考えているので、論理的には以前と同様なのかも知れない。プロセッサ3台分が出来上がっているが、マイクロの未実装で1台でしか動作していない。UNIXシステムに接続されていて簡単なプログラムを実行出来る。

# 一参考文献一

(DENNIS79) Dennis, J.B., "The Varieties of Data Flow Computers" Proc. 1st Intl Conf. on Dist. Comp., Huntsville, Alabama Aug. 1979.

(DENNIS80) Dennis, J.B., Boughton, G.A., Leung, Clement K.C.,

"Building Blocks for Data Flow Prototypes" Proc. of the 7th Annual Symposium on Computer Architecture, vol.8 Na.3 May 1980

# 3.2.2 Arvind (MIT)マシン

A. 場 所: マサチューセッツ工科大学

B. Arvind

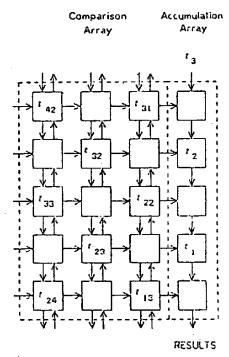

C. 特 徴: アーキテクチャの特徴は

(1) 高度の並列性を得るためプロセッシングエレメント(PE)を高度に分散すること。

- (2) 非同期動作

- (3) VLSI向き

- (4) 遅延があってもスループットの大きい構成。

- (5) 何台でも接続可能で台数に応じ性能が向上

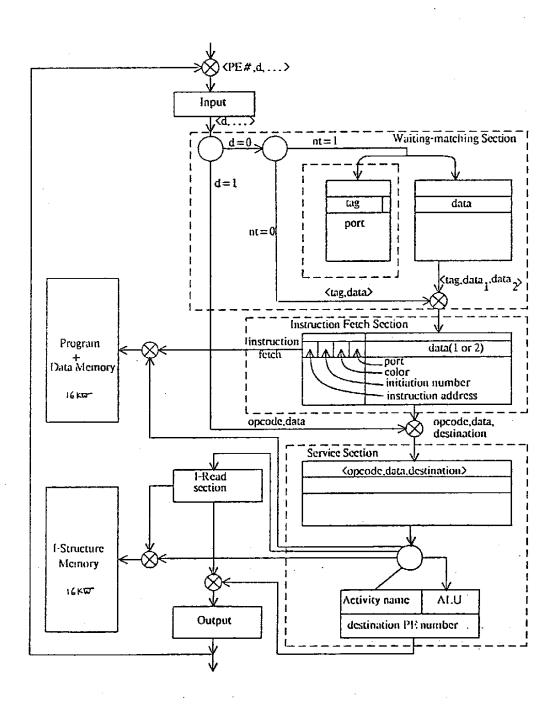

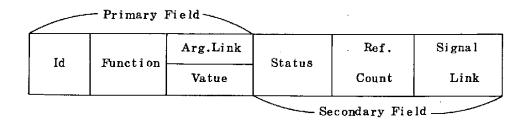

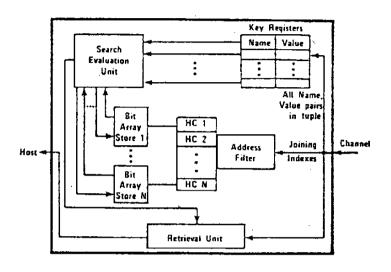

等である。とのマシンはIdのインタブリタをハードウェア化したものである。全体の構成を図3.2.4に示す。PEとネットワークはパケットを用いて通信し、パイプライン式に働く。PEの構成は図3.2.5である。Waiting Matching Section はトークンの待ち合わせを行う。Instruction Fetch Section はトークンに対応する命令をプログラムメモリから取り出す。Service Section は命令を実行し結果をトークンの形式にまとめる。Iーread Sectionは構造メモリの命令を処理する。その中にはまだデータが書き込まれていないメモリを読み出しに来た時はその命令を待たせる機能がある。

PEの特徴は各Section が非同期のパイプラインで動くこと、トークンの待ち合わせ方式、I-structureのサポート等にある。

ネットワークは8×8のルータを必要な数だけ並べてPEを接続する。PEは幾つかのグループに分けられており、プロシーシャや構造メモリはこのグループを単位として割り付けられる。 とれらの管理はスケジューラが行う。

# D. 問題点

構造メモリを各PEに分散しているのでデータアクセスのオーバヘッドが大きくなるかもしれない。手続きの割り付けやロード、構造メモリの割り付け等が動的に行われるためオーパヘッドが大きい。分散の程度が高いためスケジューリングが難しい。

図3.3.4 全体構成

# E. 現 <u>状</u>

このシステムの最終的インプリメントはPEと8×8ルータを nMos VLSIで作る予定である。 すでにWaiting Matching SectionとルータはVLSI化に着手している。またハードウェ アンミュレータとしてM68000を4~8台接続したシステムを作成中である。 このシステムの 目的はIdで書かれた大きなプログラムを実行し,種々のデータを取ることである。ソフトウェ アシミュレータは完成しておりスケシューラや構造メモリの研究,アーキテクチャのチューニング に使用されている。

# 一参考文献一 -

1) Arvind 他"A Data Flow Architecture with Tagged Tokens"MIT LCS Memo TM174, 1980

図3.3.5 PEの構成

# 3.2.3 Rumbaugh マシン

<u>A 研 究 者</u> : J.Rumbaugh, MIT(GE)

#### B. 特 徵

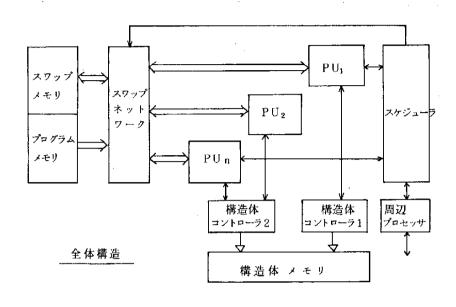

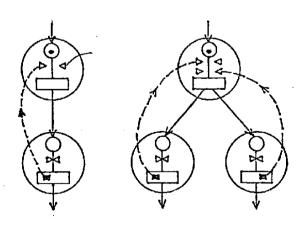

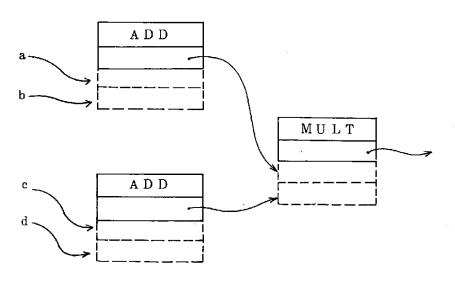

複数のPU(アクティビティメモリユニットとエグゼキューションユニットを中に含み、閉じた処理ができる)とスケシューリングを行う専用プロセッサ、1つの構造体メモリと複数の構造体メモリコントローラ、プログラムメモリとスワップメモリよりなる。

1つのPU に割り付けられるのは、常に1つの手続きであり、この割り付けは完全に動的であって、callがあったときに、idle PU がスケジューラにより割り付けられる。手続きの処理が終了したときは、スケジューラを通じて、caller に値が渡され、PUの解放もスケジューラが行う。従って、PU間の直接通信はなく、各PUはスケジューラとだけ通信する。

PUの有効利用のため、手続きはそれが終了していなくても、call した手続きの終了を待っているような場合には、スワップメモリにスワップアウトされ、他の割り付けを待っている手続きがとのPUに割り付けられる。スワップアウトされた手続きは、終わるのを待っていた手続きが終了したときidle PUが存在する場合には、そとへスワップインされる。従って、手続きは同一PUでずっと処理されるわけではない。以上の動的割り付けを行うために、各PUは内部の処理状態を示すアクティビティカウンタを持ち、スケジューラは各PUのそれを絶えず監視している。

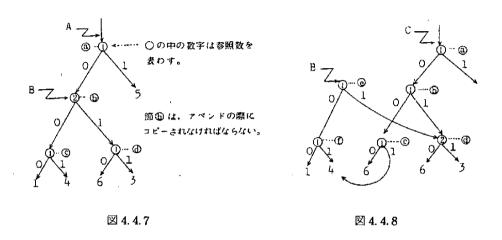

アクティビティの制御方式としては、コードの共有を行わないコピー生成方式であるので、カラーは用いない。また、手続きの起動やループの制御方式は、同期式である。

構造体データは一括して構造体メモリに蓄えられており、参照カウントにより管理されている。各PUはそれぞれ構造体メモリコントローラを通じて構造体メモリにアクセスする。 read, write 等の構造体操作命令は、構造体メモリコントローラで行われ、参照カウントの更新もこれにより行われる。

#### C. 問題点

スケジューラが全資源の管理を集中一括して動的に行うため、スケジューリングプロセッサが 常に高負荷であり、その処理速度が大規模システム構成にしたときに、ボトルネックになる。

#### D. 現 状

概念設計だけに終っている。

#### 一参考文献一

J.Rumbaugh, "A Data Flow Multiprocessor," IEEE Trans. Computers Vol.C-26, Na 2, 1977.

PUの構造 EXU: エグゼキューション・ユニット

図3.2.6 Rumbaugh 機

# 3.2.4 LAUシステム

A. 研究者: D.Comte, N.Hifdi, J.C.Syre. G.Durrieu 他, ツールーズ大学

### B. 特 徵

単一代入規則にもとづくLAU言語を実行する専用マシンである。LAU言語では、 すべての文は代入文と見なされ、プログラムは代入文の集合であるデータ生成集合(DPS:Data Production Set)を単位として構成される。DPSは入れ子にすることができ、DPS内部の文は単一代入規則にもとづくからデータ駆動で実行される。

実行制御については、カラーはなく、DPSごとに同期制御を行っている。すなわちDPSが終了するのは、その中のすべての文が終了したときとしている。手続きはコンパイル時にユーザが指定した数だけコピーを生成しておき、Callを実行したときに、free なコピーとリンクをとり、free なものがないときは待ち行列に並ぶようにしている。

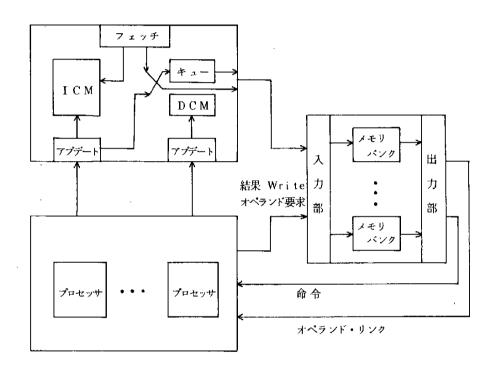

システムは、制御、メモリ、実行の3つのサプシステムよりなっている。命令及びデータはともにメモリサプシステムにあり、制御サプシステムは、データの有効性を示す1語1ビットのデータ制御メモリ(DCM: Data Conrol Memory)と命令ごとのオペランドの到着状態を示す命令制御メモリ(ICM: Instruction Control Memory)をもち、命令の発火制御を行う。命令実行は以下のようにして行われる。ICMより必要なオペランドすべてが到着していることが検出された命令は、そのアドレスがメモリサプシステムへ転送され、そこで、命令コードが読み出され、実行サプシステムに転送される。実行サプシステムはブロセッサアレイよりなっており、オペランドをメモリから読み出し、命令を実行し、終るとその結果をメモリサプシステムに格納し、同時に、そのデータの有効性を示すためDCM中の対応するビットをセットするよう制御サプシステムに伝える。制御サプシステムは、そのビットをセットし、その後、それをオペランドとする命令のICMを更新する。以上のようにして命令は処理される。

#### C. 問題点

メモリサプシステムは命令、オペランド、データリンク等、すべての情報を集中して管理してお り、その結果、制御サプシステム、実行サプシステムから頻繁なアクセス要求を受けるため、ボト ルネックになっている。

# D. 現 状

実行サプシステムが、32個のプロセッサをもつ試作機を完成し、現在評価中である。

#### 一参考文献一

1) A. Plas et al., "LAU System Architecture: A Parallel Data-Driven Processor Based on Single Assignment", Proc. of International Conference on Pa-

rallel Processing, 1976.

2) O.Gelly et al., "LAU System Software: A High Level Data Driven Language for Parallel Programming, "Proc. of International Conference on Parallel Processing 1976.

図 3.2.7 LAU

# 3.2.5 DDM 1 (Utah 大学)

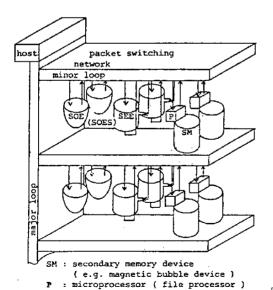

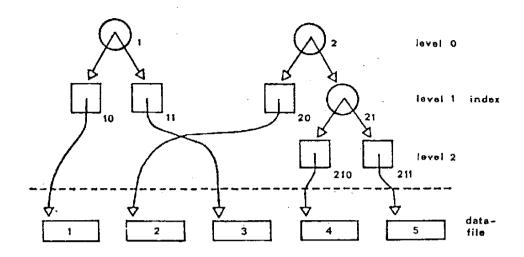

Davis の手によって開発された Utah 大学の DDM 1は,高度にmodular 化され,再帰的に構成されたデータフロー計算機である。 DDM 1はデータ駆動の原則にもとづいたプログラムを 処理でき,パイプライン的処理および高度の並列処理を実現できる。 DDM 1は充分に分散された 非同期多重処理を行い,規模を拡大する際にも,何ら物理的制約を課さない。 その上,タスクの物理的な割り付けを自動的にかつ動的に行うため,システム拡充の際のソフト的な配慮も不要である。

ハードウェアは大きく分けて、互いに非同期に演算実行を行えるProcessor-Module とそれ

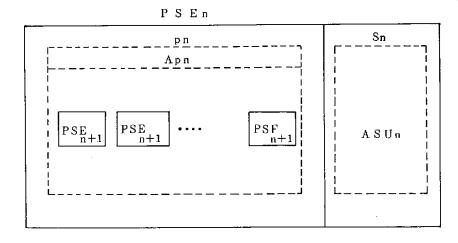

らをつなぐ通信moduleとから成っている。基本構成 unitはPSE (Processor Store Element ) と呼ばれ、processor module (P) と局所 storage module (S)とからなり、どの PSE単体も DDN (Data Driven Net: DDM 用のデータフロープログラム ) で書かれた機械語を実行できる。全体の構成はこの PSE を用いて再帰的に定義され BNF では次のように示すことができ

$\langle PSEn \rangle$ : = $\langle Pn \rangle \langle Sn \rangle$

$\langle Sn \rangle$ : = $\langle ASUn \rangle$

$\langle Pn \rangle$ : =  $\langle APn \rangle 1 \langle APn \rangle \langle PSEGROUPn + 1 \rangle$

<PSEGROUPn+1>: :=<PSEn+1>1<PSEn+1><PSEGROUPn+1>

図3.2.8 PSE(第nレベル)の再帰的定義

この構成は、階層化した分散記憶構成に適したものであり、Sn. ASUn における記憶の機能は、 任意の媒体を用いて、実現できる。PSEの上位レベル(添字が小)のものは、より多くの substructure を有するため、並列機能が高い。それゆえ下位のものに比べて access 時間が長く容 量の大きい媒体を用いるようにすれば、効率が良く、matchingがとれた、よいシステム 設計と いえる。

下位PSEから上位PSEへのmessageはスイッチによって任意に送られる。 それに対して上位 PSEから下位PSEへ送る場合は、headerを付加してゆき先を指定し、スイッチ部分で選択を行 う必要がある。

各PSE間にはキューが存在し、パイプライン制御を援助し、各モジュールの独立性を高める。 キューの容量を over しそうになると送出側は messageの伝達を一時停止し、空きが生じるまで 待たなければならない。

上位のPSEから"仕事"をもらったPSEは、その"仕事"の中に並列性を見出すことができ、 しかも下位のPSEがidleであることがわかれば、"仕事"を分解して、それぞれ下位のPSE に わたす。下位のPSEにわたさない場合は、当該PSEで実行し、その結果を必要とするPSE に必要 なだけ copy して転送する。 これらの動作を再帰的に繰り返し行うことにより、DDNを実行してゆ く。

DDM1の長所としては,

- (1) 並列処理、pipeline 処理による性能の向上

- (2) 分散制御による overhead の分散化、信頼性の向上

- (3) あらゆる構成レベルにおいて同一の構造をとるため、modular化、LSI化が容易で、機能の 拡張・追加が、特別な soft、hard の手直しを加えることなく容易にできる。

- (4) Memory 構成が flexibleで、任意のASUに、任意の媒体を用いることができる。

- (5) Processor の冗長構成により障害の庶蔽効果がある。 があげられる。逆に短所としては、

- (1) hard 的には、固定された木構造であるため他のPSEが下位レベルのPSEを必要とする場合でも、不要のPSEを供出することができない。

- (2) 効率を充分発揮させるためには、かなり冗長な(というよりむしろ無駄なくらいの)量のhardware を必要とする。

#### 一参考文献一

- 1) Davis, A.L. "System Aspects of Data Driven Nets (Data-Driven Computation Part II)" Buroughs IRC Report, Feb. 1975.

- 2) Davis , A.L. "Structured Data (Data Driven Computation Part III)" Burroughs IRC Report , Mar. 1975 .

- 3) Davis, A.L. "Data Driven Net Queueing Phenomenon ( Data Driven Computation Part VII)" Burroughs IRC Report, Tan. 1975.

- 4) Barton, R.S., Davis, A.L., et al "System and Method for Concurrent and Pipeline Processing Employing A Data Driven Network" U.S. Patent, no.3, 978, 452, Aug. 1976.

- 5) Davie, A.L. "An Overview of Data Driver Machine #1" Technical Report, Burroughs ASDO, July, 1976

- 6) Davis, A.L. "The Architecture of DDMI: A Recursive Structured Data

Driven Machine "UUCS-77-113, Oct. 1977.

- 7) Davis, A.L. "The Architecture of DDMI: A Recursively Structured Data Driven Machine" Proc. of the 5th Annual Symposium on Computer Architecture, pp. 210-215, 1978.

- 8) Davis, A.L. "Data Driven Nets: A Maximally Concurrent, Procedural, Parallel Process Representation for Distributed Control Systems"  $UUCS-78-108,\ Jnly.\ 1978.$

- 9) Davis, A. L. "A Data Flow Evaluation System Based on the Concept of Recursive Locality" Proc. of 1979 National Computer Conference, vol.48, PP. 1079-1086, 1979.

- 10) Glushkov, V.M., et al "Recursive Machines and Computing Technology "Proc. of IFIP Congress 1974, pp.65-70, 1974.

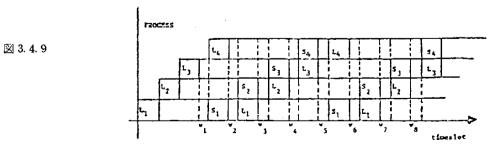

# 3.2.6 Manchester 大学のデータフローマシン

このマシンはManche**ste**r 大学の J.Gurd, I. Watson 等によって開発されている<sup>1)2)3)</sup>

図3.2.9 Manchester 大学のデータフローマシン

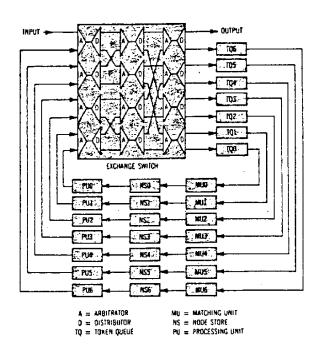

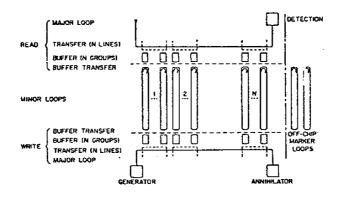

マシンは図3.2.9のようにサーキュラバイプラインを多層化した構造をなしている。各パイプラインのステージは、トークンのバッファリングを行う token queue 、 ノードの発火制御を行う matching unit ,プログラムを格納する node store,命令を実行する processing unit , および、層間や入出力装置への通信手段を提供する switch から構成される。

このマシンは主として数値計算の並列実行に主眼をおいており、その主要を特徴を以下にあげる。

#### (1) 非同期通信

各 unit 間の通信は非同期なハンドシェイク法で行っている。従って各 unit は独立な内部ク クックで動作できる。

## (2) 並列ハッシュによる発火検出

命令の発火検出を行うために、matching unit内に8パンクから構成される並列 ハッシュ表を用意している。各パンクのメモリ容量は2Kwords × 96bits である。さらに、ハッシュ表のオーパフローが発生したときのために overflow unitを用意している。トークンあたりのmatching unit内での処理時間は200 ns と想定している。

## (3) コードのセグメント化

命令アドレスをセグメント番号(6bits)とセグメント内の変位(12bits)で表わしコードの再配置を可能にしている。node store内には64エントリから成るセグメント表があり、実際のコードのアドレスはこのセグメント表から求められるペースアドレスとセグメント内の変位を加算して得られる。

### (4) マイクロプログラム制御の処理装置

柔軟性を考慮して処理装置としてはマイクロプログラム制御のビットスライスマイクロプロセッサ AMD 2900 シリーズを使用している。 処理要素はこのプロセッサ 6 個(24 ビットデータ幅)から成る演算装置とし、その平均命令実行時間を 4.5 #S と想定している。従って、matching store の処理速度(命令あたり 300ns)とのパランスを考慮して、 processing unit 内にはこの処理要素が 15 台並列に配置されている。

#### (5) 均質な層間通信

各層の間や層と入出力装置の間の通信は、バイナリルータを組み合わせた構成となっている switch が行う(図3.2.9を参照)。従って、各層間の通信遅延は均一になっている。

### (6) 色つきトークン

トークン長は96ビットであり、そのうち36ビットを色(識別子)フィールドとして割り当てている。このフィールドはさらに、関数識別子、繰り返し番号、およびインデックス識別子に分けられている。前2者は、例えばArvindのマシン4)と同様であるが、インデックス識別子は

配列要素の並列アクセス等のために使用される。

#### (7) 単一代入言語

前述のマシン開発と並行して、LAPSEと呼ばれる単一代入の高水準言語を設計し、そのコンパイラを開発した5)。この言語はPASCALをベースに単一代入規則を導入したもので、条件式、繰返し、(再帰)関数呼出し等の機能を備えている。また、データタイプとしては整数や論理値の外に、配列やレコード型も用意されている。

# (8) 非决定的処理

記憶ノードの概念を導入することにより、Dijkstraのguarded command 6)や Hoare の Communicating Process 7) のような非決定的な制御方式についても研究している 8)9)。記憶ノードは色の制御命令と matching store内のマッチング機能の追加によって実現している。

とのマシンの問題点としてはリストのような動的データ構造の機構が用意されていないという ことがあげられる。従って、知識情報処理に適用するためには構造メモリを付加する必要がある。 現在、1つのサーキュラパイプラインから成る実験機の試作・評価を行っている。また、デー タフロー言語コンパイラも稼動中である。今後、さらに、高機能な言語や多層構造マシンの開発 も予定している。

## 一参考文献一

- J.R.Gurd, I.Watson, "Data Driven System for High Speed Parallel Computing," Computer Design, July 1980.

- 2) J.R.Gurd, J.R.W.Glauert, "A Multilayeved Data Flow Computer Architecture," Dept. of Computer Science, University of Manchester, July 1978.

- 3) I.Watson, J.R.Gurd, "A Prototype Data Flow Compuputer With Token Labelling, "Proc. of AFIPS NCC VOL. 48, June 1979.

- 4) Arvind, V.Kathail, "A Multiple Processor Data Flow Machine that Support Generalized Procedures, "Proc. of 8th Symposium on Computer Architecture, May 1981.

- 5) J.R.W.Glanert, "A Single Assignment Language for Data Flow Computing," MSc. Dissertation, Dept of Computer Science, University of Manchester, Jan. 1981.

- 6) E.W.Diikstra, "Guarded Command, Nondeterminacy and Formal Derivation of Programs, "Comm. of ACM, Vol.18, Na.8, Aug. 1975.

- 7) C.A.R.Hoare, "Communicating Sequential Processes", Comm. of ACM, Vol. 21. Na 8, Aug. 1978.

- 8) A.J.Catto, J.R.Gurd, "Nondeterministic Data Flow Graphs", Proc. of IFIP Congress 80, North-Holland Publishing Company, Oct. 1980.

- 9) A.J.Catto, J.R Gurd, "Resource Management in Data Flow", Proc. of Functinal Programming Languages and Computer Architecture, Oct. 1981.

# 3.2.7 Keller マシン

Utah 大学のR. M. Keller, G. Lindstrom, S. Patil らによって提案された要求駆動型のデータフローマシンである。 $^{1)2}$  要求駆動型の発火機構では、命令はその実行結果が必要とされる場合(他から要求がある場合)にのみ発火するという特徴がある。

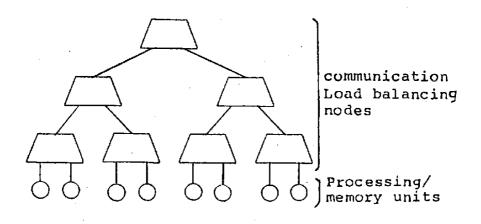

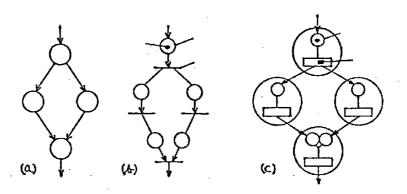

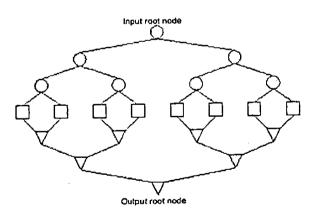

このマシンは図3.2.10に示すように、木構造を形成するノード群からなっている。台形のノードは通信用プロセッサで、調整/分配(arbitration and distribution)の働きを行う他に、配下のプロセッサの実行状態に応じて負荷の均衡を行う機能を持つ。円で示される終端のノードは汎用の処理ユニットで、それぞれがローカルメモリを持っている。これらのローカルメモリは、全体で1つのアドレス空間を提供する線形アドレスメモリとして機能することができる。場合によっては処理ユニットとしてI/Oプロセッサや特殊用途のプロセッサが接続される。これらの処理ユニットは要求駆動の原理にもとづいて動作し、要求元のユニットに必要な情報を送出する場合は、木の調整/分配ノードを経由して目的のユニットに送られることになる。

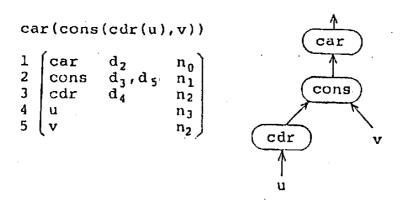

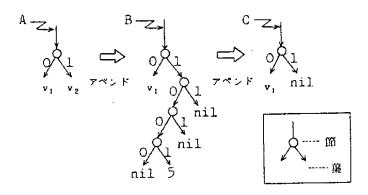

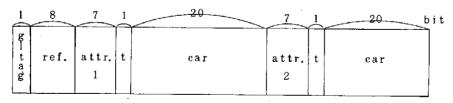

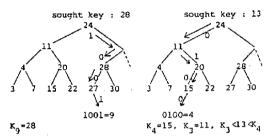

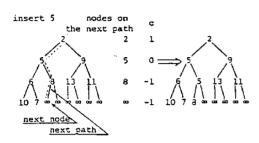

要求駆動型のプログラムはEGL (Flow Graph Language ) と呼ばれるLisp方言で書かれる。 プログラムは code block および data block からなっている。 code block には FGLのコンパイル結果 (データフローグラフの線形表現)が保持される。とこでは、 instruction コード は実行すると消費されデータに変化するという設計方針がとられているので、 関数の application を行う際、新たに data block が割り当てられ、そこへ source code がコピーされる。図 3.211 は car (cons (cdr(u), v)) に対する data block 内の初期コードを示したものである。 data block 内の各エントリは literal value か instruction かのいずれかである。

instructionは、a. operation code b. demand (オペレータの引数のアドレス) c. notifier (との命令の値を待っている命令のアドレス) d. global address (block間のリンケージのために使用される)等から構成される。プログラムの各行には参照用番号が付されている。例えば、このプログラムの第2行

cons d3, d5 n1

において、d3 、d5は「3 および5 の番号のついた命令にオペランドを要求せよ」ということを、またn1は「1 の番号のついた命令に(cons の) 実行結果を通知せよ」ということを意味している。

要求駆動型の特長は、引数の値が必要になった時点で要求を出すので、不要な計算を省くことができること、要求駆動と遅延評価(cons(x,y) の評価の際、引数x,yの評価を行わず先にセルだけを返す)の機能を組み合わせて無限リストの操作がうまく扱えることにある。しかし実行効率という観点からみると、要求が次々と最内側まで(値が得られる所まで)伝搬されねばならないので、このオーバヘッドが問題となる。

Kellerマシンでは,(1)木構造を利用して最短経路の通信プロセッサを用いて通信を行うことができる。(2)関数対応に参照があることを前提に(従来のLispインブリメンテーションを念頭に置いているためであろう),ローカルメモリ構成としている。(3)動的アロケーションを行う,などの特徴を有しているが,いまだ理論的提案の段階にあり不明な点が多い。現在の研究はマシンよりも適用性型言語FGLの理論的側面に向けられている。3)

### 一参考文献一

- Keller.R.M., Lindstrom G. and Patil S., "An Architecture for a Loosely

coupled Paralled Processor, "UUCS-78-105 Univ. of Utah, 1978.

- 2) Keller R.M., et al, "A Loosely-coupled Applicative Multi-Processing System", Proc.Nat.Comp.Conf., 1978.PP.861-870

- 3) Keller R.M., "Semantics and Applications of Function Graphs", Technical Report (MCS-77-09369), Univ. of Utah, March 6, 1980.

図3.2.10 Kellerマシン

図 3.2.11 グラフ表現と data block 内の初期コード

#### 3.2.8 TOPSTAR(東京大学)

1977年頃鈴木等によって開発が始められ、1978年に第1号機であるTOPSTAR-Iが、1980年にTOPSTAR-Iが栗原等によって試作された。TOPSTARはマルチマイクロプロセッサ システムを、プロシジャレベルのデータフローによって分散制御することをめざしたものである。

その構成は、処理要素であるPM(Processing Module )と通信および制御ノードである CM(Communication / Control Module )の2種類のモジュールが図3.212のよう に結合したものである。データフロー処理単位(これをアルゴリズムと呼ぶ)ごとにPMが実行し、これらの処理単位間のデータの流れやタスク(= アルゴリズム+データ)の生成などをCMが制御している。

アーキテクチャの特徴は

- (1) CMとPMの2種類のモジュール多数より成り、それぞれがベトリネットの"place"と "transition"の役割りを果たす。(図3.2.13)

- (2) CMとPMの結合は大規模システムの実現を可能にするため部分結合とする。この際データフローグラフとの対応を柔軟に行うために、この結合をオーバラップさせ可変構造を可能にしている。

- (3) プロシーシャレベルのデータフロー処理においては比較的多量のデータを扱うので、DMAに よってメモリ対メモリの高速転送を行う。

各PMは、結合している範囲の1つのCMに割り込みをかけ、DEQ(DEQ ueue)コマンドを送ることにより"仕事"を要求する。各CMには、それぞれいくつかのノードが割り当てられており、DEQコマンドを受けたCMは制御テーブルを調べて、実行可能な"仕事"があれ

ぱそのブロシージャ,データ,結果の送り先の情報をPMに送る。実行可能な"仕事"がない場合には、その旨を知らせる。"仕事"をもらったPMはその"仕事"を実行し、結果の送り先のノードが割り当てられているCMに割り込みをかけ、ENQ(ENQ ueue)マンドを送り、ひき続いて結果のデータを送る。アイドル状態になったPMは再び"仕事"を求めてCMに割り込みをかける。

図3.2.12 TOPSTAR-IのCM-PM間結合

図3.2.13 データフローグラフ、ペトリネットおよびTOPSTARにおける処理の関係

以上のように、各PMが"仕事"を求めて(部分結合の範囲で)自由競争を行うことにより、 "忙しい"すなわち、実行可能な"仕事"が多く存在するСMに、自然に多くのPMが集まり、 適切な負荷分散が行われる。

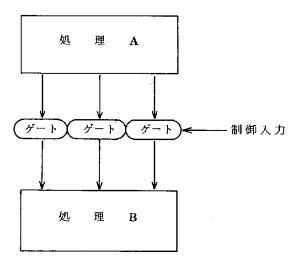

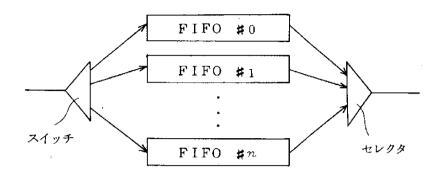

マルチプロセッサシステムにおける並列処理性には、パイプラインによる縦の並列性と独立した演算が並行して実行できる横の並列性が存在する。一般のパイプラインでは、FIFOによる制御が行われているが、データによって処理時間が大きく異なるような場合には、追い越しを許すととにより、並列処理性の向上が期待できる。しかし、無制限な追い越しを許すと、FORKーJOINの際にデッドロックを生じる可能性があるため、セマフォによるフローコントロールを行う必要があり、TOPSTARではこれを実装している(図3.2.14)。

すでに、応用プログラムとして、論理回路シミュレーション、並行故障シミュレーション、並列PROLOG等が実装され、評価が行われた。

問題点としては

- ① データフローグラフの各ノードを、どのCMに割り付ければ効率があがるか→(準)最適割り付けの問題。

- ② メモリ容量の不足と結合範囲の狭さ。

- ③ (データフロー一般の問題でもある)大きな構造データを扱う効率上の問題,歴史依存性,ファイル、データベースの扱い等のいわゆる「記憶」の問題。

- 障害の検出あるいは回復の問題。等があげられる。

図 3.2.14 セマフオによるフローコントロール

#### 一参考文献一

情報処理学会全国大会

- 1) 元岡,喜連川,鈴木「A High Level Data Flow Machine Hardware 」 1979

- 2) 元岡, 鈴木, 喜連川「A High Level Data Flow Machine -Software 」 1979

- 3) 鈴木,田中,元岡「データフローマシンTOPSTARの制御方式とその評価」1980

- 4) 栗原,鈴木,田中,元岡「データフローマシンTOPSTARのデータ駆動型制御方式」

- 5)深沢,栗原,鈴木,田中,元岡「データフローマシンTOPSTARによる論理回路シミュレーション」1980

- 6) 駒田, 鈴木, 田中, 元岡「データフローマシンTOPSTARによる並列LISPシステム」 1980

- 7)栗原,深沢,秋元,鈴木,田中,元岡「データフローマシンTOPSTAR-Iのハードウェア 構成と基本ユーテイリテイ | 1981

- 8) 秋元,深沢,栗原,鈴木,田中,元岡「データフローマシンTOPSTAR-Iによる論理シミュレーション」1981

- 9) 深沢, 栗原, 秋元, 鈴木, 田中, 元岡「データフローマシンTOPSTARーⅡの性能測定と評価」1981

- 10) 鈴木, 田中, 元岡「データフローマシンTOPSTAR-【における並列LISPシステム」

- 11) 相田, 松方, 鈴木, 田中, 元岡「データフローマシン向き PROLOG型言語に関する一考察」 1981

- 12) 中田, 田中, 元岡「データフローマシン" TOPSTAR— II "によるコンカレント故障シミュレーション」1981

- 13) 相田, 田中, 元岡「データフローマシン TOPSTAR-I"を用いたPROLOG並列処理 試作システムの検討」1981

- 14) 相田, 田中, 元岡「並列PROLOGシステム "Paralog "の性能測定」1982 (寄稿中)

- 15) 萩野,田中,元岡「データフローマシンTOPSTAR─Ⅱの動作解析と評価」1982(寄稿中)

雷気学会全国大会シンポジュウム

16) 元陶, 鈴木「SAMD (Single Algorithm÷stream Multiple Data-stream)」 1979 研究会

- 17) 鈴木, 田中, 元岡「バイブライン式 S A M D 計算機とその漢字認識への応用」信学技報 E C 7 8 2, 1978 年 4 月

- 18) 元岡, 鈴木, 喜連川, 新岡「SAMD計算機~A High Level Data Flow Machine~」 情処, 計算機アーキテクチャー研, 1979年5月

- 19) 栗原, 鈴木, 元岡「High Level Data Flow Machine (TOPSTAR)のシステムプログラム」信学技報EC79-56, 1980年1月

- 20) 鈴木, 元岡「データフロー計算機の制御と評価」情処, 計算機システムの解析と制御研, 1980 年2月

- 21) 深沢, 田中, 元岡「Multi Processor Simulator」電子装置設計技術研究連絡会 夏期シンポジウム研究発表資料

- 22) 深沢, 栗原, 鈴木, 田中, 元岡「データフロー計算機による論理シミュレータ」電子装置設計技 術6-3 1980年10月21日

# 3.2.9 D3C(東京大学)

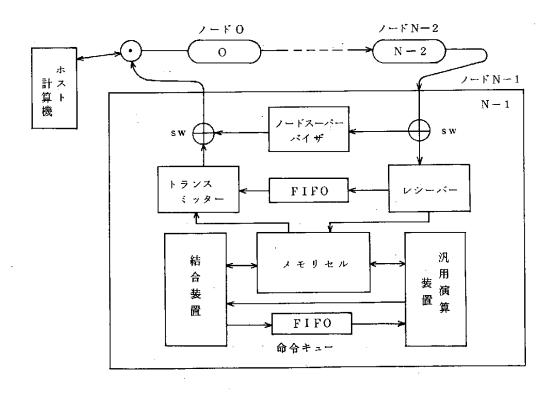

D³Cは1979年後半から開発されたデータフローマンンで、後田、グエン等によって試作された。 アーキクチャ上の特徴は、「分散形・ループネットワーク、非同期演算実行システム」ということ ができる。分散型とは「演算の実行の際に、ハードウェアユニットの選択が何らかの形である程度 制御可能」なもので、概念図を示すと図3.2.15のようになる。すなわち各構成モジュールは、メ

図3.215 分散形モデル

モリセル・演算・結合の各ユニットを有し、それぞれ単体でデータフロー計算機をなしており、その構成モジュールをネットワークによって結合して、より高性能のシステムを目ざしている。ネットワークとしてはループネットワークを採用しているが、システム拡張性を考慮にいれた結果であり、実用化にあたってはモジュール数を数十以上接続することを想定している。ループネットワークの欠点としてトータルシステムの信頼性の低さが考えられるが、①各ノードに開閉容易なバイパススイッチを設ける ②ノード間結合はフォトカプラとする、③1ノードの停電時には、電磁リレーで強制的にバイパスされる 等の手法を実験システムにも実装し、信頼性の向上をはかっている。

「分散型」にした1つのねらいはこの「信頼性向上」にある。集中型の場合には、演算ユニットが完全な自由競争の原理で実行可能な演算をとりこんで実行するため、どの命令がどの演算装置で行われたかを知ることが容易ではなく、故障個所の検出は極めて困難である。それに対して各アクタに対して、どの構成モジュールで実行すべきかをある程度制御(監視)できれば、故障の検出、さらには故障モジュールの切断が可能であり、アクタを再配置することにより、実行の再開も可能である。

図3.2.16 D<sup>3</sup>Cの概念構成図

ユーザのプログラムから並列性をとり出してスループットをあげるという一般的なデータフローマシンの目的の他に、ユーザプログラムの copy を異なる構成モジュールで走らせ(原ユーザプログラムと並列に走る)、結果を照合することにより、スループットをさほど下げることなく、信頼性の向上をはかることも目指している。

問題点としては、発火時の自由競争にある程度の制約を加えることにより、上記の目的を達成しているため、アクタの各構成モジュールへの割り付け方がスループットを大きく左右すること、ネットワーク構成(ループ結合)に内在する課題などがあげられる。

現在,グエン,大山等によるバス結合分散形データフロー計算機「EDAC」が開発中であり、 シミュレーションを通して,各種設定パラメータが検討されつつある。

# 一参考文献一

- 1) 浅田, グエン・ニュット, 堀, 斉藤, 猪瀬, "データフロー計算機における故障検出の一方式" 854情報処理分散処理システム研究会1-4

- 2) 堀, 浅田, 斉藤, 猪瀬 "データフロー計算機における牧障検出の一方式" S 5 4 信学全大情報システム部門 3 6 0

- 3) グエン・ニュット, 浅田, 斉藤, 猪瀬 \*\*分散形データフローコンピュータの構成 \*\* S 5 4 信学全 大情報システム部門 3 5 9

- 4) 浅田, グエン・ニュット, 堀. 斉藤, 猪瀬 "分散形データフロー計算機の故障検出方式の評価" S 5 4 信学全大情報システム部門 3 5 8

- 5) 浅田"計算機複合体における故障診断修復方式に関する研究"東京大学博士論文 S 5 5

- 6) 池田,"分散型データフロー計算機におけるアクタの割り付け"東京大学卒業論文S55

- 7) グエン・ニュット, 大山, 斉藤, 猪瀬, 『高性能分散型データフロー計算機の制御機能 " S 5 6 信学全大情報システム部門 5 1 0

- 8) 大山, グェン・ニュット, 斉藤, 猪瀬, "高性能分散形データフロー計算機の通信機能"S 5 6 信学全大情報システム部門 5 1 1

- 9) 大山, 斉藤, 猪瀬, "分散型データフロー計算機のプログラムモデルを用いた性能評価"信学技 報EC80-14 1980年6月

- 10) 大山,斉藤,猪瀬、分散形データフロー計算機(EDAC)の待行列モデルによる理論解析" S 5 7 信学全大情報システム部門寄稿中

# 3.2.10 D<sup>3</sup>P(沖電気工業)

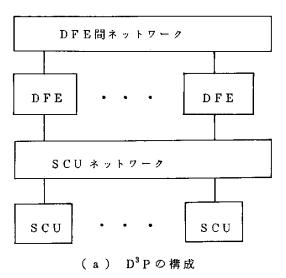

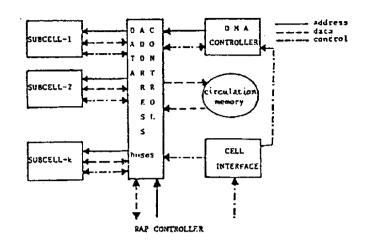

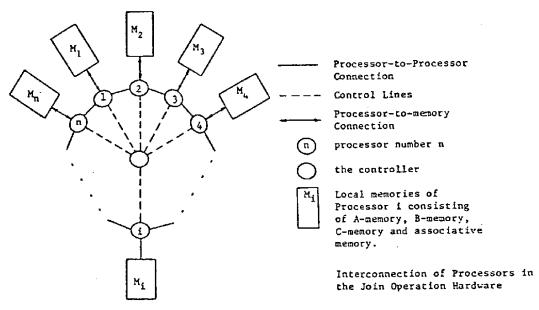

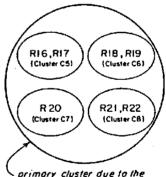

沖電気の伊藤,来住,安原によって開発されているデータフローマシンである<sup>1)2)3)</sup> マシンは図 3.2.1 7 のように,関数クラスタ(関数又は関数の集合)を実行するDFE群,構造メモリの格納,管理,操作を行うSCU群,およびそれらの装置間の結合ネットワークから成る。

(b) DFEの構成 図 3. 2. 1 7 D<sup>3</sup>Pの構成

DFE内はさらに、サーキュラバイプライン構造のPE群、色(アクティペーション番号)の割り当て管理を行うACU、およびPE間の結合ネットワークを形成するリングバスから構成される。各PE内のバイプラインの各ステージは、コードを格納し、命令の発火制御を行うIM、命令を実行するPU、リングバスのトークンの入出力を制御するBCから成る(同図(b))。

本マシンの特徴は以下の通りである。

#### A. 関数クラスタの並列実行

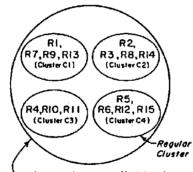

各DFEはそれぞれ独立に関数クラスタを並列実行すると共に、関数クラスタを適当なアルゴリズムによりDFE内のPE群にマッピングすることで、クラスタの並列性も生かす。 このマッピングアルゴリズムとしては、ノードAの出力が2つ以上のノードB、C、D、……に渡されるとき、うち1つのノード(例えばB)をノードAと同一のPEに、それ以外のノード(C、D、……)を順次ノードAの隣接PEに群に割り当てる方式を採用した。

関数やループの起動はトリガートークンを用いた先行制御方式とした。

#### B. 統合化された色

関数識別子とループ (繰り返し)識別子を区別せず統合化された色を使用している。また使い終えた色を解放するプリミティブも用意されている。これによって色空間の効率的な使用が可能となる (色フィールド長が比較的小さくてよい)。

#### C. ハッシュとタグによる発火検出

命令のオペランドが揃ったか否かを検出(発火検出)するために、ハッシュ表およびオペランドタクを組み合わせたハードウェア構成にしている。即ち、色フィールドをも含めたアドレス空間(各PE当たり 2<sup>21</sup> 語)を16語単位のプロックに分割し、このプロック単位で物理アドレス(各PE当たり 2<sup>12</sup> 語)に変換するためにハッシュ表を使用している。実際の発火検出はこの物理アドレスをもとにオペランドタクを読み出すことによって行われる。

# D. 構造データの非同期アクセス

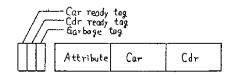

構造データの非同期アクセス機能を実現するために、SCUメモリ内の各セル毎にWタグとRタグと呼ばれる2つのフラグが存在する。Wタグは該セルへの書き込みが行われたか否か(即ち、セル内のデータが有効か否か)を示し、Rタグは該セルに対して読み出し要求があったか否かを示す(要求があったときは、SCU内の待ち行列にチェインされる)。この機構によってlenient consやstreamのような操作をサポートできる。

#### E. 可変語長データ

オペランド語長は16ビット(基本語長)から64ビット(4倍語長)まで可変である。この ため浮動小数点や短いストリン等も基本データとして処理できる。 問題点としてはSCU内のガーベッシコレクションの実現方法(現在はヒープ管理法)の検討, DFE間やSCUへのネットワークの設計・評価および高水準言語の設計等が残されている。 現在, 4台のPEから成るDFEの実験システムを試作し, 調整中である。IMおよびPUはマイクロプログラム制御であり, PUのALUとしてはビットスライスマイクロプロセッサ2900シリーズを用いている(SCUおよびACUの機能は各PU内でエミュレートする)。

# 一参考文献一

- 1) 来住, 伊藤, 安原, 河村, 「データフロー実験機の構成」, 昭和57年信学会全国大会, 1982 年3月。

- 2) 伊藤, 来住, 安原, 河村, 「データフロー計算機 D³Pのアーキテクチャ」, 情報処理学会,計算機アーキテクチャ研究会, № 42, 1981年7月

- 3) 安原, 伊藤, 来住, 「データフロー計算機 D³Pのアーキテクチャ」, 沖電気研究開発, Vol, 47, Na 2, 1980年12月。

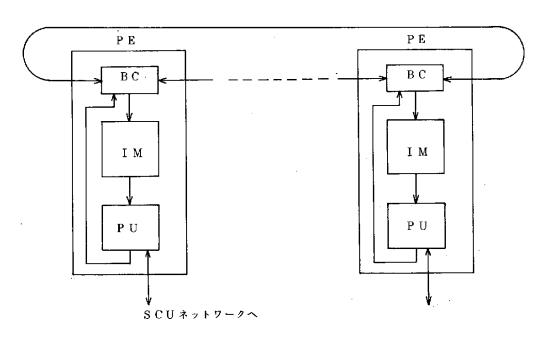

### 3.2.11 東北大学のデータフローマシン

とのマシンは東北大学・工学部の伊藤,斉藤,星子等によって研究・開発されている。 $^{1),2)}$  図 3.2.1.8 にその構成を示す。マシンは,トークンの同期制御や命令フェッチを行うECU群,命令の実行制御を行うFU群,構造データの記憶,管理,操作を行うMCU群,プロセス(関数呼出し)のスケジューリングを行うPCU,およびこれらの装置間を結ぶ2つのバスから構成される。さらに,とのマシンを複数結合したシステムも検討している(同図(b))。

図 3.2.18 東北大学のデータフローマシン

本マシンの特徴は以下の通りである。

### A. 関数性の徹底

データフローマシンにおける意味付けのあいまいなループ制御やTrueゲート, False ゲート等のオペレータを排除し、命令レベルにおいても関数性を徹底させている。

# B. 縮約過程にもとづく計算

コピー規則にもとづいてプログラムの実行過程を縮約(reduction)の過程として実現している。即ち、ECUには連想機能を有する命令レジスタ群が存在し、先着オペランドが現われた時点で(即ち、命令レジスタ群を連想検索して対応する命令がないことが確認されたとき)、その命令がコードメモリよりフェッチされ、レジスタ内の空きスロットに格納(コピー)される。このレジスタの内容はその命令の全オペランドが揃った時点で読み出されて無効にされる。

#### C. 多入力オペランド命令

命令レンスタの各エントリにはEC(Enabling Count)と呼ぶカウンタが存在し、オペランド到着毎にデクリメントされる。この値は先着オペランド到着時に初期設定され、値がゼロになると全オペランドが揃ったことになり、命令は実行可能となる。多入力オペランド命令は主として多入力引数を有する関係呼び出し用に使用される。

# D. 柔軟なデータ構造

MCUはリスト構造や配列等の柔軟なデータ構造をサポートする。とのため参照カウント方式を採用し、メモリの動的管理はMCU側で行う。さらに、データにタグを付与し、実行時の正当性チェックも行っている。

本マシンの問題点としては関数の起動をその全引数が揃うまで待つために並列度が低下する恐れのあること、各装置間の通信を共通パスによって行っているので接続される装置数に制限があること、およびハードウェア構造が複雑になると予想されることがあげられる。

現在、マシンのエミュレートを行うためにビットスライスマイクロプロセッサから成る4台の 汎用ユニットを作成し、そのファームウエアおよびソフトウエアの開発を行っている。

### 一参考文献一

- 1) 伊藤, 斉藤, 星子, 「関数型データフロー計算機システム」, 信学技報 E C 3 1, 1981 年 10月,

- 2) 伊藤, 斉藤, 星子, 「関数型データフローマシンのシステム構成」, 情報処理学会第22回全国 大会, 1981年3月, PP.55~56.

### 3.2.12 Passive Memoryless Architecture

A. 研究者: 寺田浩韶, 浅田勝彦, 大阪大学

### B. 特 徵

受動的でメモリをもたないタスクレベルでの処理機能をもつ多数の処理ユニット(PU:

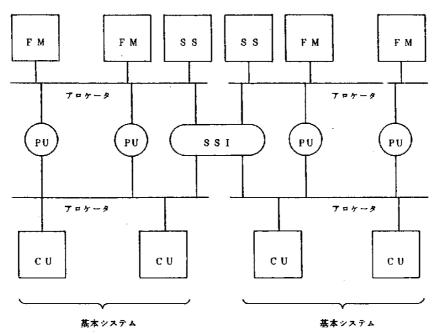

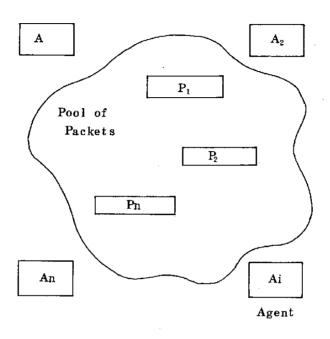

Processing Unit )と能動的でデータフローグラフをもちデータ駆動制御を行う多数の制御 ユニット(CU: Control Unit)とそれらを選択的に結合するアロケータからなる。

アロケータはモジュールの追加・除去が容易であり、適当をインタフェースを介することにより、階層化、多重化等の種々の構成をとることができる。2つの非同期2線式自己診断リングアービタと共通バスで構成されており、2つのアービタはそれぞれ能動モジュール、受動モジュールでのアービトレーションを行い、バスは結合の確立されたユニット間でのデータ転送に使われる。アロケータによる選択的結合は常に能動的モジュールであるCUの要求にもとづき、CUの出すセレクションコードにより行われる。セレクションコードは、CUよりPUへのオペレーションの転送のときは、ファンクション名、PUより CUへのトークン転送のときは、目的ノードとカラーである。

SSI: システム システムインターフェース

SS : 入出力サプシステム

FM :機能メモリ

⊠3.2.19 PASSIVE MEMORYLESS ARCHITECTURE

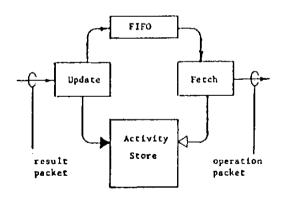

CUにおけるタスクの発火制御は次のようになっている。CU中のあるタスクノードに最初にトークンが到着すると、CUは発火に必要な残りのすべてのトークンをPUに要求する。そして、すべてそろった後、オペレーションパケットを作り、freeでかつそのオペレーションを処理できるPUへアロケータを通じて転送する。PUは結果を生成するとそれを要求しているCUがあるかどうかを見、あればそれを転送する

### C. 問題点

アロケータに要求を出せるのがCUだけであるため、ノードに最初のトークンが届いてから最後のトークンが届き、オペレーションパケットを転送するまで、1つのCUが完全に占有されてしまい、CUの利用効率が悪い。

### D. 現 状

試作機を作り, 評価中である。

#### 一参考文献一

- 1) 寺田浩韶, 浅田勝彦, "Passive Memoryless Architecture,"情報処理学会アーキテクチャ研究会 31-2, 1978

- 2) 浅田勝彦, 小谷武史, 寺田浩韶, "Passive Memoryless Architecture の一実現法," 信学技報 EC79-76, 1980

- 3) 浅田勝彦, 寺田浩韶, 他, "Passive Memoryless Architecture 上でのデータフロー 形実行制御, "信学会技報 E C 8 0 - 4 9, 1981

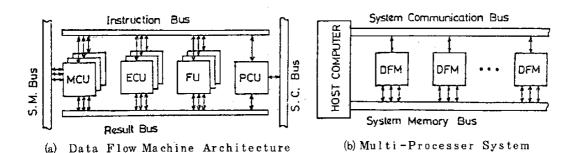

#### 3.2.13 富士通のデータフローマシン

A 開発時期 : 1981年

B. 開発者: 富士通研究所

#### C. 特 徴

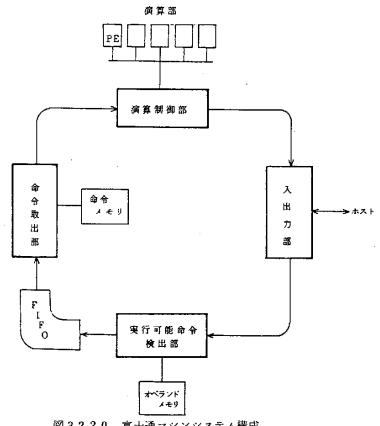

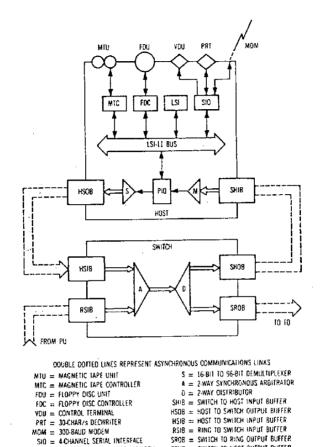

データフローの原理を、実マシンの試作を通じて把握することを主目的としたマシンであり、 命令レベルでの並列処理を可能としている。アーキテクチャとしては、Dennis型のセルブロッ クが1個でファンクションユニットが複数の場合とやや似た構成と考えられる。システム構成を 図3.2.20に示す。[MASUZAWA81]

図3.2.20 富士通マシンシステム構成

- o 命令メモリとオペランドメモリを別構成してメモリ競合を避けた構成。

- o 演算部だけが複数個用意されており、コモンバスで接続されている。

- o 高級言語を設定し、コンパイラをサポートしている[ITASHIKI82]。

## D. 問題点

小規模な試作マシンであり、機能的に小さいのであまり言及出来ないが、

ο 機能的に低い

構造データ、手続、ループ等に関する機能が無い。

o 演算ユニットへのバスがネック

演算ユニットは複数用意されているが、コモンバスによって接続されているため、バスがネックとなる。

o 条件分岐の扱い方

条件文に対して、真偽の結果より前に式の評価を先行しており、見かけ上の並列度は上るが トータルとして見ると実行時間に不利となっている。

演算部に汎用演算チップ4個と特殊演算ハード(ゲート,コピー等)を使い、残りの部分はハードワイヤドロジック。座標変換用の数値計算プログラムを実行させ、多重度2前後で動作する。

### 一参考文献 一

[MASUZAWA81] 増沢, 板敷, 相馬, "データ駆動型プロセッサー基礎実験機一" 昭和56年度 信学会全国大会, Ma1445

[ITASHIKI82] 板敷、佐藤、増沢、相馬、"データフローマシン用高級言語コンパイラの試作"昭和57年 情報処理学会第24回全国大会、Na7D-3

### 3.2.14 電総研のデータフローマシン

A. 場 所: 電子技術総合研究所

B. 人 弓锡, 島田, 山口

### C.特 徵

数値演算用とLISP用の2つのデータフローマシンの研究が行われている。数値演算用は Arvindマシンに関してスケジューラの構成法やスケジューリングアルゴリズムについて研究し、 その改良を目指している。

LISP用データプローマシンEM-3はLazy 評価機構を並列化することにより、LISP 言語の実行においてより多くの並列性を引き出そうとしている。このような試みは、CONSについてはユタ大学や武蔵野通研で行われているが、電総研では一般的な関数評価の機構にまでこの概念を拡張している。

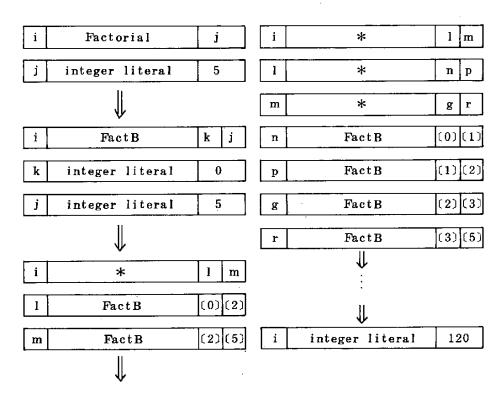

この関数評価機構の特徴は、関数の呼び出し機構に特別の処理形態をもうけることによってデータ駆動制御における高度な並列性の実現とLazy関数評価機構を自然な形で融合している点に

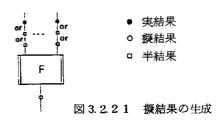

ある。関数の呼び出しが行われた場合、ことではデータ駆動制御にもとづき、この関数がある特別のオペレーションを実行したものとみなす。そしてこの関数呼び出しによって得られる関数の値を擬結果(pseudo result)と名付ける。(図 3.2.2.1 参照)。

#### F: Defined Function

関数本体の実行は擬結果の出力と同時に行われ、擬結果はその関数本体の処理が終了した時点で実結果(actual result) に置き換えられる。

擬結果はデータ駆動制御において、通常の値を持った実結果と同様に演算や関数を発火させる働きを持つ。このためデータ駆動方式を用いた関数の評価機構に対して先廻り制御やパイプライン動作が導入され、その並列性を増大する効果をもたらす。特にリスト構造を生成するオペレーションの値として半結果(semi result)というデータ型を導入し、これを本制御機構上で動作させることによりLenient Consが自然に導入される。実結果が必要とされるオペレーション(たとえば数値演算)に擬結果が渡された場合には、実結果が得られるまでそのオペレーションの実行は待たされる。

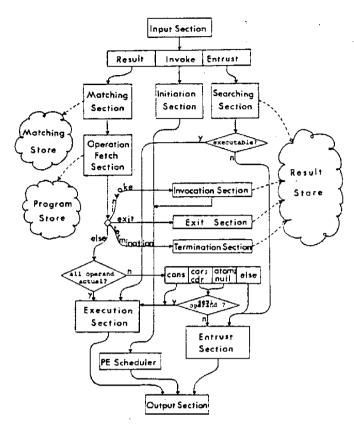

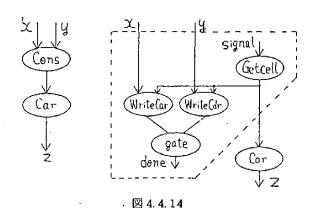

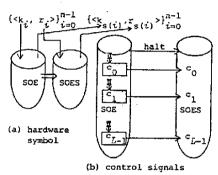

複数台のプロセッサエレメント(PE)で上述の評価機構を実行するためのPEの機能モデルが提案されている。これを図3.2.2.2に示す。上述の擬結果を管理するために各PE内には結果記憶(result store)と呼ばれる擬結果の管理領域が必要とされ、ここにおかれた擬結果表や遅延バッファによって、各PEが独立して関数評価の制御を行うようになっている。

### D. 現 状

高級言語としてデータフロー用LISP言語(EM-LISP)とデータフローグラフレベルの中間言語(EMIL)の仕様を定め、そのコンパイラが作成されている。上記のメカニズムの妥当性とデータ収集のためのソフトウェアシミュレータを作成中である。またLISPで書かれたプログラムの動的実行形態を並列処理の立場から分析するための統計データを収集中である。

#### E. 問題点

構造データが分散配置されるため、関数評価におけるスケジューリンクアルゴリズムをネット ワークのハードウェア構成に従って適切に選択する必要がある。また扱結果のガーベジコレクシ

図3.2.2 2 PEの機能ブロック図

ョンなどが必要とされ、オーバーヘッドが増大する危険もある。

#### 一参考文献一

- 1) 山口, 弓場, 島田:「データ駆動計算機 EM-3の関数評価機構」, 信学技報, EC81-57 (昭56.12.)

- 2) 島田:「タク付トークンを使用するデータ駆動計算機シミュレータ」,信学技報,EC81 58 (昭5 6.1 2.)

- 3) 島田:「タグ付トークンを使用するデータ駆動計算機のシミュレーション」,情報処理学会第 24回全国大会(昭573)

- 4) 山口, 弓場:「データ駆動計算機 EM-3のソフトウエアシミュレータ」, 同上

- 5) 弓場, 山口, 島田; 「データ駆動計算機用Lisp とその中間言語」同上

- 6) 山口,弓場,山田:「データ駆動モデルからみたLispプログラムの動特性」同上

#### 3.2.15 通研のデータフローマシン

電電公社武蔵野通研で開発が進められているデータフローマシンである。超高速料学技術計算を指向した数値処理用(DFM-U)と知能処理などの非数値計算を指向した記号処理用(DFM-L)の2種類がある。

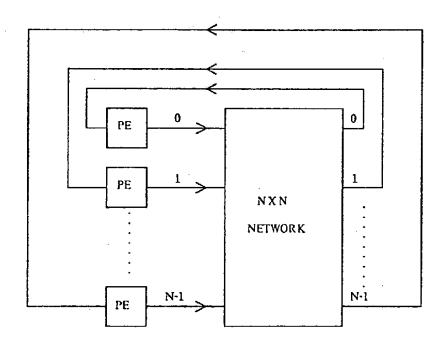

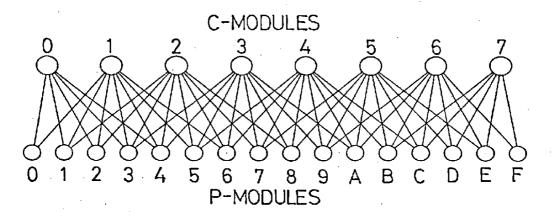

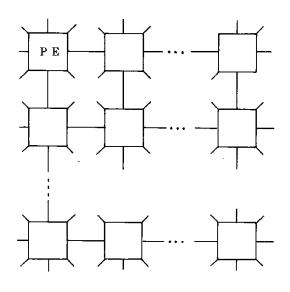

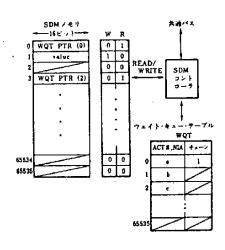

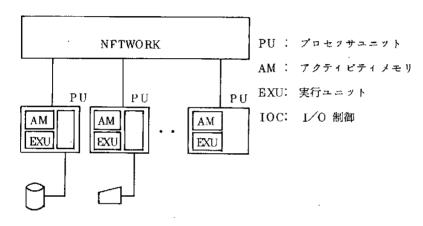

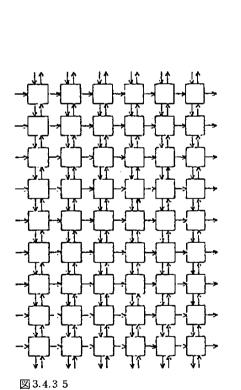

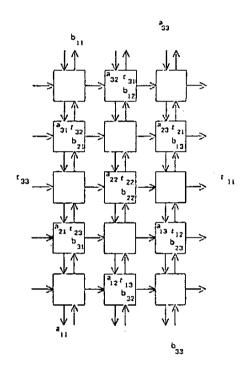

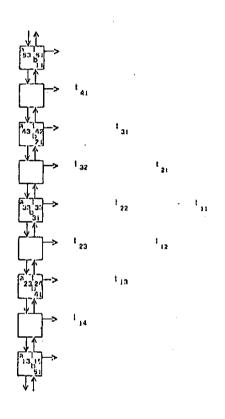

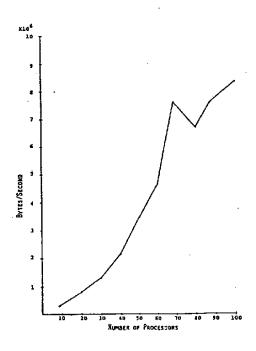

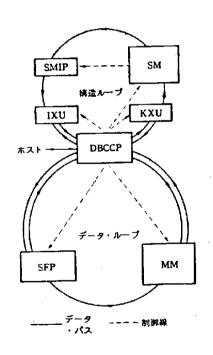

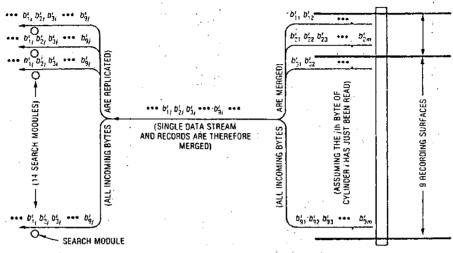

DFM-Nは、自律的に動作する多数のデータフロープロセッサ (PEと呼ぶ)をアレイ状に結合したシステムである。 $^{(1)}$  2) ( $\boxtimes$  3.2.2.3 )

図3.2.2.3 DFM-Nの構成

- o プロセッサ内およびプロセッサ間の制御を全てデータフロー概念で統一することにより、自 律的で並列度の高いシステムを実現すること。

- 偏微分方程式の解析等の格子問題では近傍計算が主なので、各格子点をアレイ要素のPEに 割り当てることにより、通信コストおよび遅延時間の問題を解決することを主な狙いとする。

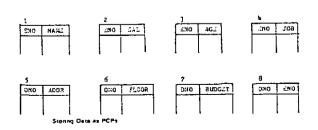

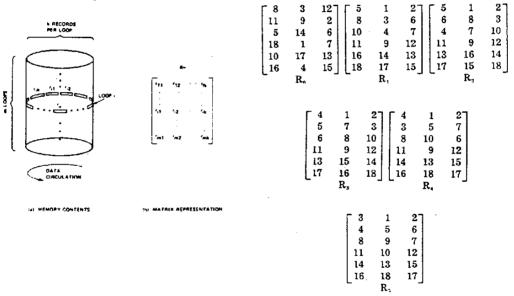

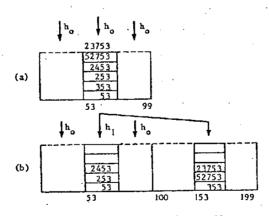

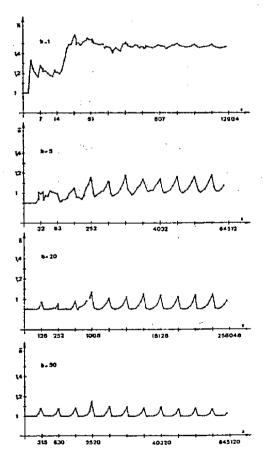

色つきトークン方式を採用しており、静的(コンパイル時)および動的(実行時)名前づけを併用したアレイデータ処理に特徴がある。アレイデータの各要素は各PEに写像され分散処理される。要素とPEとの対応関係は、アレイ型データ対応に写像方式を定めるディスクリプタ(D)と、要素対応にPEの割り当てを定めるインデクス(I)を用いて、予め静的に与えられている。処理中Iの変更があると、インデクス操作のマクロ命令が実行され、結果のプロセッサ間転送が引き起こされる。ループで実行されるデータはループカウントフィールド長に制限があるので、オーバフローした時点で同期をとる命令が設けられている。

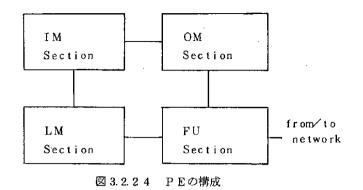

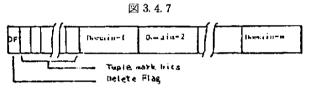

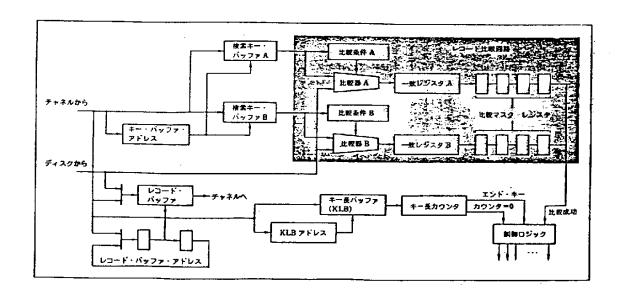

PEは図3.2.2.4のように、命令メモリ(IM)、オペランドメモリ(OM)、演算ユニット(FU)、リンクメモリ(LM)からなる循環パイプライン構成である。IMにはプログラム(本体)が格納され、OMは到着オペランドを保持するパッファとして使用される。LMには結果の分配先命令名が格納されている。LMではFUの実行結果パケットに付された結果名で分配先命令名を求め、それを基にオペランドパケットを作る。オペランドパケットがIMに到着すると対応する命令が読み出され、オペランドパケットを作る。オペランドパケットがIMに到着すると対応する命令が読み出され、オペランドパケットと共にOMへ送られる。命令が2オペランド形式であれば、オペランドパケット中の<命令名、instance名>をKeyとしてOMを検索する。OMのKey検索には、8重並列ハッシュ方式を採用している。一致すれば該(対となる)データを読み出し、命令パケットを構成してFUへ送る。一致しなければ、オペランドパケットをOMに保持しておく。命令が1オペランド形式ならば直ちに命令パケットと構成しFUへ送る。命令パケットには実行後の結果名が含まれている。FUは複数の演算器からなり、浮動小数点演算、通信処理、I/O処理ユニット等が含まれる。

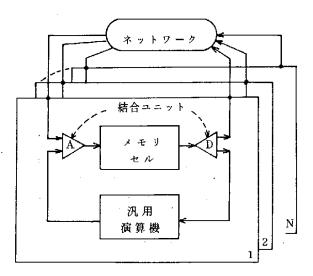

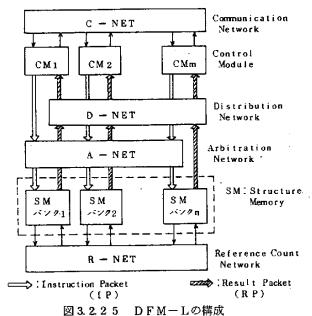

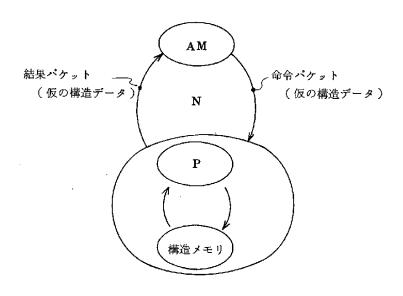

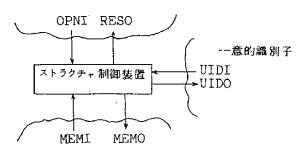

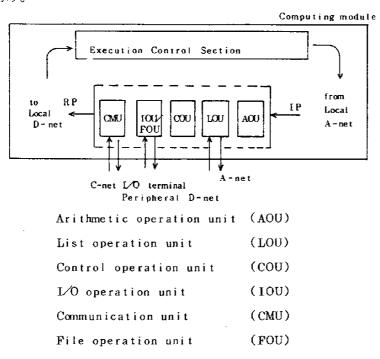

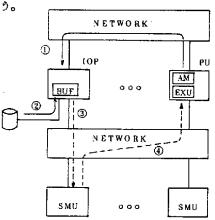

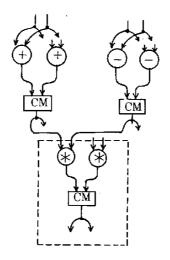

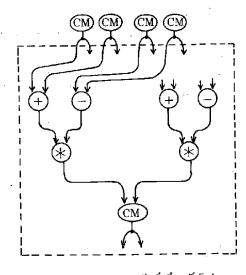

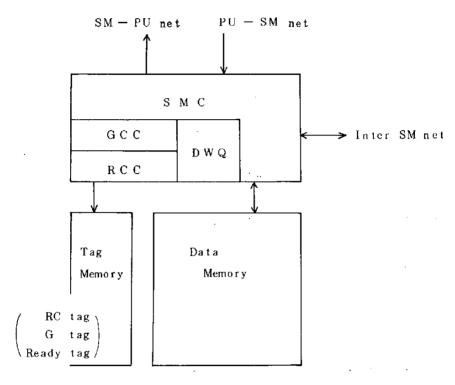

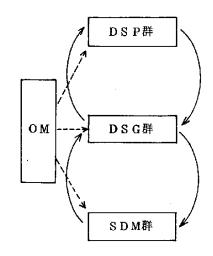

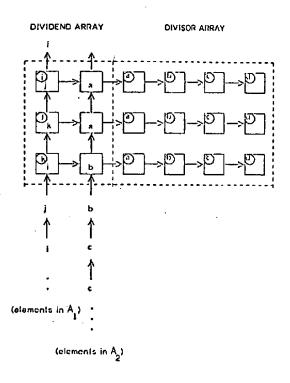

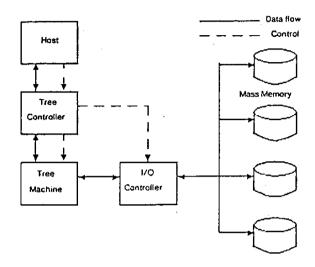

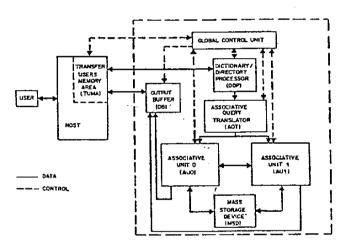

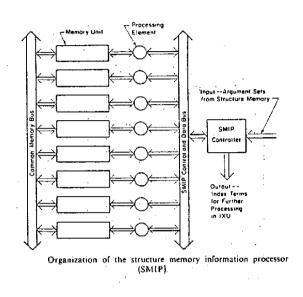

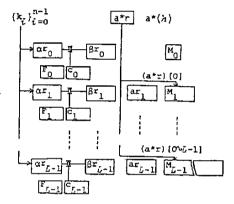

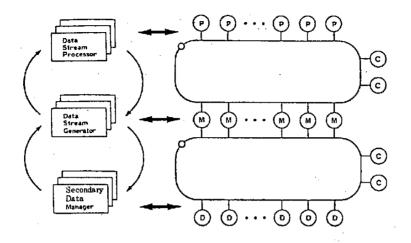

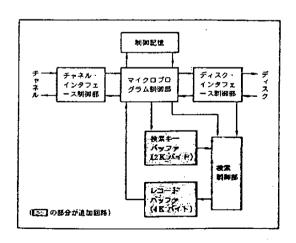

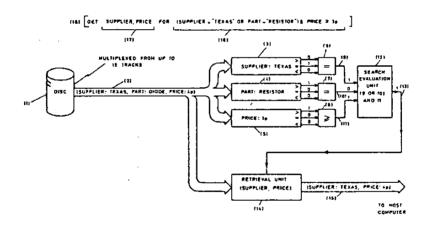

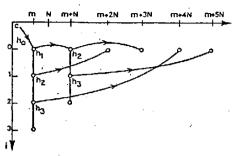

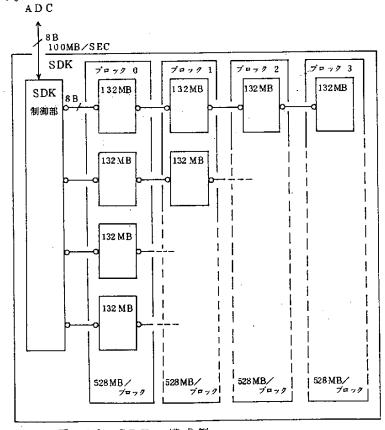

DFM-Lは、実行制御部(CM)、CM間をつなぐ通信ネットワーク、複数のバンクから構成される構造体メモリ(SM) および CM-SM間を結合する調整ネットワーク(A-uet)、分配ネットワーク(D-net) からなる。 $^3$ (図3.2.25)

DFM-NとDFM-Lの実行制御機構は共通である。CMはPEとほぼ同様の構成をとり、浮動小数点演算ユニットの代わりにA-net およびD-netへのインタフェース回路が置かれる。リスト処理の演算ユニットはSMに組込まれている。SMの各パンクはさらに独立動作可能な car, cdr, attribute, reference count のフィールドに分解され、それぞれに専用の操作ユニットが設けられる。CMから送出された構造体操作命令パケットはパケット中のオペランドアドレスのデコードにより、対応するSMパンクへ転送される。D-netはSMから送出された結果パケットを受け取ると、結果パケット中のCM番号を基に要求元CMへその結果パケットを送る。

図3.2.23 DrM-Lの構成

car, cdr フィールドには ready (値が未到着)を示すタグがあり、これにより Lenient cons, Lazy evaluation の機能が実現されている。

現在,数値処理用および非数値処理用データフローマシンの共通の基盤となる循環パイプライン型PE1台と,SM2パンクからなる実験機の設計を行っている。この実験機はPE1台であるがデータフローマシンとして動き,データ駆動原理の確認の他,データフロー用高級言語Validの開発ツールとしても使用される。また,複数PEでの性能を調べるため,先に開発された4×4PE(ソフトウェアでデータ駆動制御を模擬)のデータフロープロセッサアレイ実験機EDDYを使って評価が進められている。

### 一参考文献一

- 1) 高橋, 雨宮, "超高速科学技術計算を指向したデータフロープロセッサアレイ計算機の提案," 信学技報 EC80-24, 1980.

- 2) 高橋,吉田,成瀬,雨宮, "超高速科学技術計算向きデータフロープロセッサアレイ計算機の構成と制御,"昭57電子通信科学会全国大会

- 3) 雨官,長谷川,三上,"リスト処理向きデータフローアシンアーキテクチャとそのソフトウェアシミュレータ、" 信学技報 EC80-69, Feb.18, 1981.

- 4) 中村, 長谷川, 雨宮, "リスト処理向きデータフローマシン用構造体メモリの設計と評価," 信学技報 EC81-32, Oct. 29.1981.

5) 長谷川, 雨宮, "データフローマシン上でのLazy evaluation の実現について," : 情処学会第24回(昭57前期)全国大会, 5D-8.

### 3.3 リダクションマシン研究開発の現状

本章では、式の還元(reduction)という形で計算が行われるリダクション型マシンの研究開発の現状について調査を行う。リダクション型マシンでは、計算はすべて書換え規則の適用とみなされる。データフロー型マシンでの計算の考え方は、値に対してオペレーションを実行することである。即ちデータフロー型マシンではグラフのノードにデータトークンが到着すると実行可能となり、実行結果がアーク上に送出される。この過程を置換という観点からみると、ストリングまたはグラフの書き換え規則の適用としてとらえることもできる。リダクションとデータフローとの関連については、今後検討していく必要がある。

リダクション型マシンの実現の仕方には、文字列そのものを置換する string reduction と、ポインタを利用してグラフ(リスト)を操作する graph reduction の 2 通りの方法がある。 string reduction では、還元の過程で string が伸縮する際にコピーやメモリ再配置の問題が 生じてくる。 graph reductionではグラフの共有が行われるのでコピーオーバベッドの問題は ないが、共有グラフ操作のための代価は支払わねばならない。

リダクション型マシンの提案は比較的少ない。国外では、Berklingが提案したラムダ計算マシン(スタックマシン)と、Backusの提唱した関数型言語FPを実行する木構造のMago マシン、シフトレジスタを使ったTreleavenのマシンの例と、国内では日電小長谷によるCombinatorを使ったデータ駆動型リダクションマシンの例がある。以下、各マシンの特徴について述べる。

#### 3.3.1 Berkling マシン

A. 場 所 Gesellschaft fur Mathematik und Daten (西独)

B. 人 Berkling

#### C. 特 徵

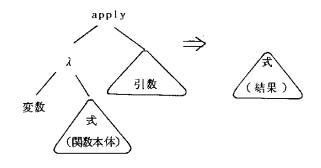

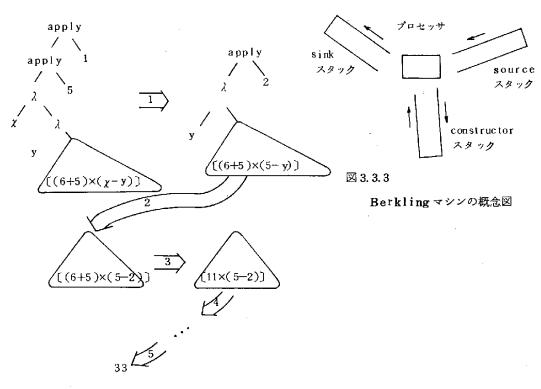

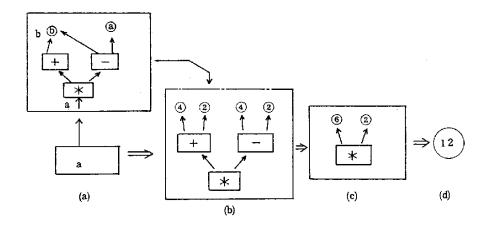

ラムダ計算にもとづき、文字列置き換えにより計算を行う。マシンには関数型言語を 2 分木で表現したものが与えられる。計算は図 3.3.1 で apply の右下の引数を $\lambda$  の左下の変数の値とし、 $\lambda$  の右下の式の中の変数に代入する形で進められる。この手順を繰り返し、式の中のすべての変数が定数に置き換わった時、計算が終了する。例として図 3.3.2 に f (x, y) = (6+x)×(x-y) の式で f (f (f ) を計算したものを示す。

Berkling マシンではこの2分木をたどり置き換える過程をスタックを用いて実現している。 アーキテクチャの概念図を図3.3.3 に示す。入力は source スタックに置かれる。 プロセッサ は source スタックの上部から要素を取り出す。もしその要素が2分木の terminal ノードで

図 3.3.1 2 分木表現とラムダ計算

図3.3.2 計算の例

あれば constructor スタックに push する。プロセッサはこうして 2 分木をたどる間いつも 3 つのスタックを監視し、もし置き換えが可能であれば置き換えを行う。 1 回も置き換えを行わず に木を始めから終りまでたどった時、計算が終了する。

←AB(AをBに適用せよ)の計算例を図3.3.4 に示す。まず←ABを source スタックに置き,終了符号(@)を constructor スタックに置く(a). 次に source スタックの先頭の ←を

図 3.3.4 Berkling マシンの動作例

プロセッサが取り出す。 $\leftarrow$ は作用素なのでconstructor スタックに push し 「印を付けておく (b)。次に source スタックからAを取り出す。これは terminal ノードなので sink スタックへ push するたびに constructor スタックから 1 個 取り出し,置き換えが可能かチェックするがこれは  $\leftarrow$  であり 「印が付いているので 「印を消去し,  $\leftarrow$  constructor スタックに戻す(d)。次に source スタックからBを取り出すとこれは terminal ノードなので sink スタックに pushし(e), constructor から 1 個取り出す。これは $\leftarrow$  なので sink のA, Bを使って $\leftarrow$  A Bを実行する(f)。再び constructor から 1 個取り出すと終了記号(@)なので計算を終了する(g)。

すべてスタックだけで操作でき、非常にシンプルなのが特徴である。

#### D. 問 題 点

文字列置き換えの方法が効率の点で問題である。並列計算へどう拡張していくかが不明である。

### E. 現 状

TTLを使って1号機が作成されている。各スタックの容量は8キロバイトである。

### 一参考文献一

- 1) Berkling, K.J.: Reduction Language for Reduction Machines, Proc 2nd Symp. on Computer Architecture, P. P. 133-138, 1975.

- 2 ) Organic, E.I.:コンピュータシステムアーキテクチャの技術動向,電子協昭和53年度特別セミナー講演録54-C-371。

#### 3.3.2 Treleaven のリダクションマシン

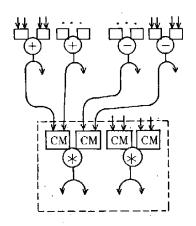

Newcastle 大のP.C. Treleaven らは図3.3.5 に示すリング構造リ ダクションマシンを 1980年に提案している。

#### A. 概 要

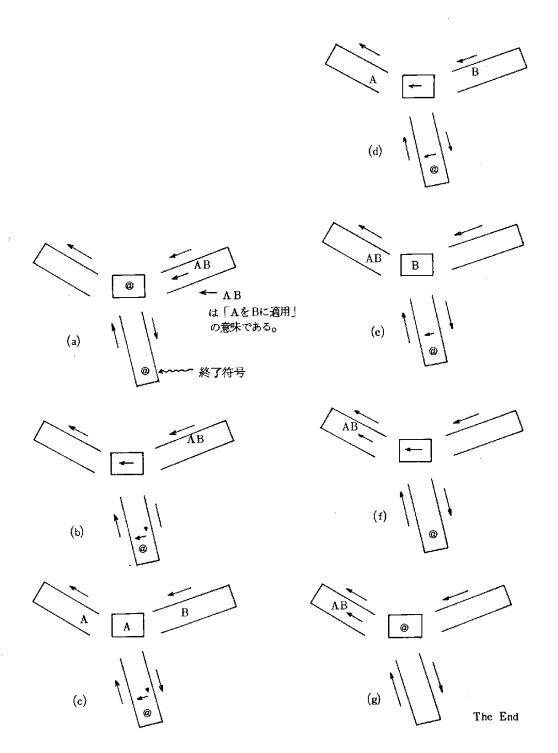

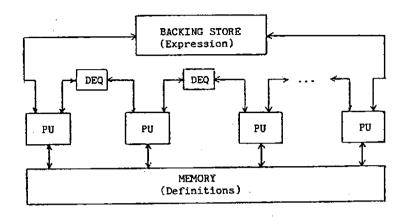

マシンの全体構成は図3.3.5 に示すように複数台の処理ユニット(PU), DEQ, Backing メモリ、定義メモリからなる。

定義メモリにはユーザの定義式を入れ、Backing メモリとDEQには計算を行う式を入れる。PUは図3.3.6 に示すように、バッファレジスタ、状態レジスタ、リダクション表、演算ユニット等から成る。リダクション表はPUの状態遷移を決めるもので、PUの現在の状態とDEQから読み込んだ式に対して次に何を実行するかが記述されている。

DEQ = double ended queue

PU = processing unit

$\boxtimes 3.3.5$  Multi-processor Reduction Machine Architecture.

Processing Unit.

図 3.3.6

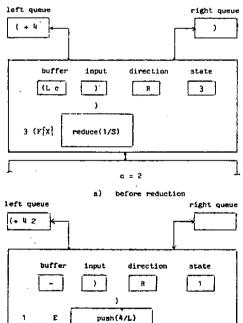

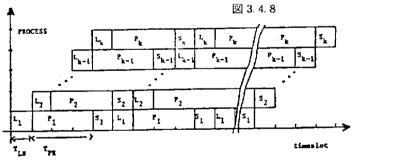

次に簡単な例に従って実行の様子を示す。図3.3.7はリダクション言語で書かれた簡単なプログラムである。ここでLはLoad, SはStore のオペレータである。このプログラムは図3.3.8 のように実行される。マシン上では図3.3.8 の式が図3.3.9 のように各PUとDEQ上に置かれリダクション表(図3.3.1 0)に従って計算が実行されていく。

|    |   |                   | stage | state of evaluation                       |

|----|---|-------------------|-------|-------------------------------------------|

|    |   |                   | 1     | (S a (L a))                               |

| t1 | = | (+ (L b) (L c))   | 2     | (S a (* (L t1) (L t2))                    |

| t2 | = | (- (L b) (L e))   | 3     | (S a (* (+ (L b) (L c)) (- (L b) (L c)))) |

| ь  | = | 4                 | . 4   | (S a (* (+ 4 2) (- 4 2)))                 |

| e  | = | 2                 | 5     | (Sa(*62))                                 |

| а  | = | (* (L t1) (L t2)) | 6     | (S a 12)                                  |

|    |   |                   | 7     | ·<br>• ·                                  |

|    |   | TT                |       | (78.0.0.0                                 |

図 3.3.7

図 3.3.8

Operation of a Processing Unit. .

after reduction

図 3.3.9

### B. 問 題 点

本マシンでは、各PU間のデッドロック等が起こらないようなリタクション表をつくることが ポイントとなる。Tre leauen らは compiler -compiler に類するリタクション表ジェネレ ータを提案しているが、現在検討中の段階である。

## 一参考文献一

P.C. Terleaven, G.F.Mole: A Multi-Processor Reduction Machine for User-defined Reduction Languages, Proc. the 1980 Symposium on Computer Architecture, May 1980.

| Input                                    |                                         |                                                   |                                                                 |                                                     |                                                    |                                                                 |  |  |  |  |  |  |  |

|------------------------------------------|-----------------------------------------|---------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|--|--|--|

| Directio                                 | n State                                 |                                                   | operand<br>X                                                    | operator<br>F                                       | brack<br>(                                         | ≱ts<br>)                                                        |  |  |  |  |  |  |  |

| right $\begin{cases} 2 \\ 3 \end{cases}$ | E ( (F{x}  {x})  F{x})                  | wait(1/S) wait(2/S) wait(3/S) give(1/C) give(1/C) | pass(1/S)<br>error(1/C)<br>push(3/S)<br>push(4/S)<br>error(1/C) | pass(1/S) push(3/S) error(1/C) push(5/S) error(1/C) | push(2/R) pop(2/S) pop(2/S) error(1/C) reduce(1/S) | <pre>push(4/L) error(1/C) reduce(1/S) pop(4/S) error(1/C)</pre> |  |  |  |  |  |  |  |

| Format o                                 | direction)  S same d  C change  R right | irection direction                                |                                                                 |                                                     |                                                    |                                                                 |  |  |  |  |  |  |  |

⊠ 3.3.10 Example Reduction Table

### 3.3.3 Magó

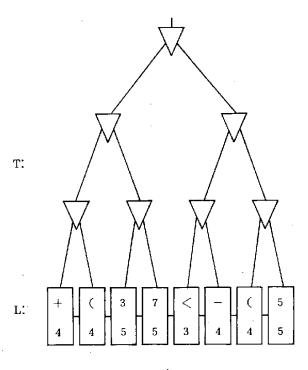

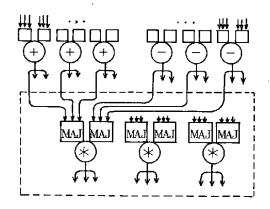

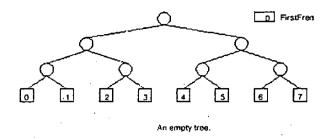

North Carolina 大学のGyula A. Magó によって提案されたリダクション型マシンであり、図3.3.11に示すような2進木状の構成をとっている。このマシンの特徴は次の通りである。

(1) VLSI化を念頭に、数種のチップを多数規則正しく並べ木構造セルを形成する。(cellular

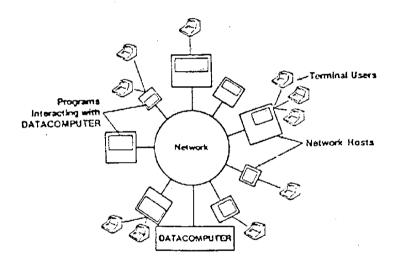

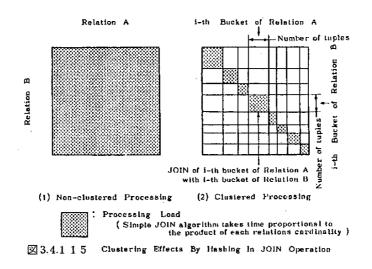

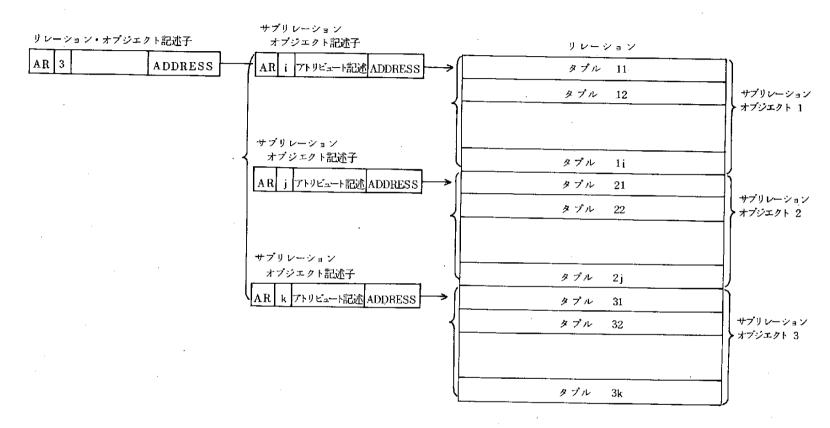

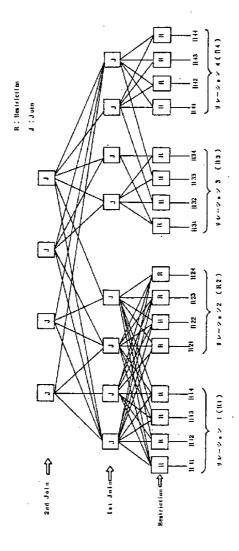

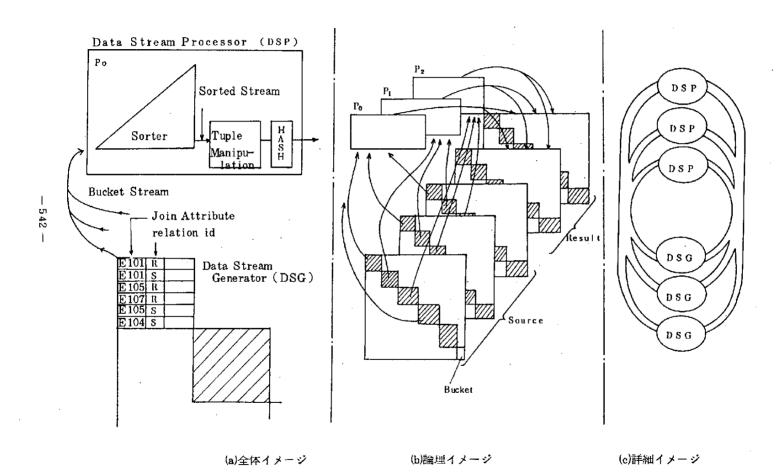

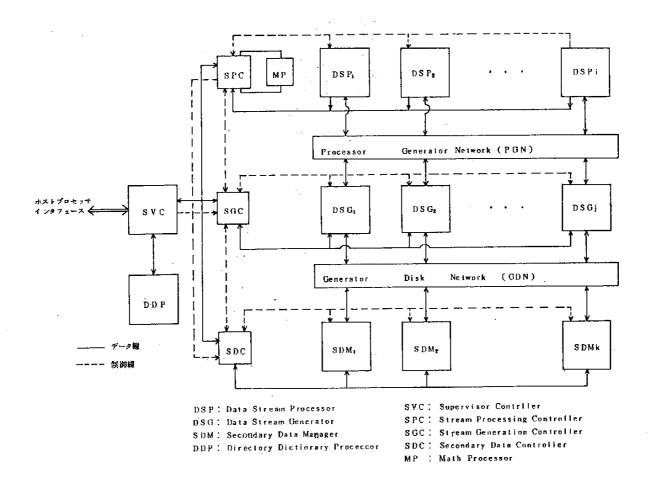

tree machine ) (2) Backus のFPクラスの言語を直接実行する。(3) FPプログラムに内在する並列性はそのまま引き出される。(4) 機械語そのものがFP言語である。